Fターム[5B060KA02]の内容

Fターム[5B060KA02]に分類される特許

1 - 20 / 186

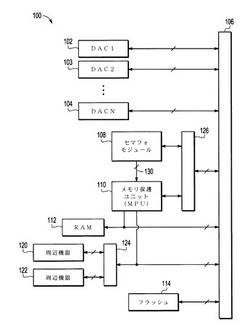

共有システムリソースのセマフォベースの保護のためのシステムおよび方法

【課題】共有システムリソースのセマフォベースの保護のためのシステムおよび方法を提供する。

【解決手段】データアクセス構成要素は、各々が共有システムリソースに対するアクセスを要求するアクセス要求を発行するように構成される。データアクセス構成要素は、前記共有システムリソースに領域記述子が関連付けられる。セマフォモジュールは、前記共有システムリソースについてのセマフォを実装するように、および、前記複数のデータアクセス構成要素のいずれかが前記共有システムリソースについての前記セマフォをロックした場合、いずれのデータアクセス構成要素が前記共有システムリソースについての前記セマフォをロックしたかを示すセマフォ信号を生成するように構成される。メモリ保護ユニットは、前記セマフォ信号および前記領域記述子に基づいて前記アクセス要求を認可または拒否するように構成される。

(もっと読む)

情報処理システム、制御システム及び半導体装置

【課題】制御システムがメモリシステムのバンクグループにアクセスする際の効率を高めることが可能な情報処理システムを提供する。

【解決手段】本発明の情報処理システムは、例えば、メモリシステム20と、アクセス制御部15を含む制御システム13とを備えている。メモリシステム20は、記憶領域が複数のバンクにより構成され、この複数のバンクが複数のバンクグループにグループ化されている。アクセス制御部15は、複数のプロセシングエンジンによるアクセスの優先順位に対応し、バンクグループ毎にレイテンシを含むアクセス情報を第1のレジスタ15aに保持し、バスマスタ11aを介してプロセシングエンジンからのアクセス要求を受けたとき、第1のレジスタ15aを参照し、その内容に基づいてアクセス対象のバンクグループに対するアクセスをフレキシブルに制御する。

(もっと読む)

動的ポート優先割当能力を有しているメモリコントローラー

【課題】動的ポート優先割当能力を有しているメモリコントローラーを提供すること。

【解決手段】メモリにアクセスするように動作可能な集積回路であって、該集積回路は、メモリアクセスリクエストを生成するように動作可能なプログラマブルマスター回路と、メモリコントローラーであって、該メモリコントローラーは、該メモリアクセスリクエストを該プログラマブルマスター回路から第1および第2のポートにおいて受信するように動作可能であり、該メモリーコントローラーは、該メモリアクセスリクエストを実行するために、該メモリにアクセスするように動作可能であり、該メモリコントローラーは、該メモリアクセスリクエストを順番に実行するように動作可能である、メモリコントローラーと、該メモリコントローラーが該メモリアクセスリクエストを実行する順番を制御するように動作可能である制御回路とを含む、集積回路。

(もっと読む)

プロセッサ、マルチプロセッサシステムおよびメモリ制御方法

【課題】ローカル命令メモリのサイズを実質的に拡大する形態でローカル命令メモリを各プロセッサ間で共有できるマルチプロセッサシステムにおけるプロセッサを提供する。

【解決手段】第1CPU100は、メモリ共有モード設定レジスタ107に格納された情報を参照することで、第1CPU100が命令フェッチを行うアドレスが、ローカル命令メモリ先頭アドレスレジスタ103とローカル命令メモリ終了アドレスレジスタ104とで定義される領域内であるか、または、共有命令メモリ先頭アドレスレジスタ105と共有命令メモリ終了アドレスレジスタ106とで定義される領域内であるかを判定し、その判定の結果に基づいてセレクタ102を制御することで、命令メモリ101と命令メモリ201とを切り替え、切り替え後の命令メモリから命令をフェッチして実行する。

(もっと読む)

情報処理システム、調停方法

【課題】精度の良い調停を行うことができる情報処理システム、及び調停方法を提供する。

【解決手段】イニシエータIP1−1は、ターゲットIP5に対し、一定処理を行うために必要なデータ転送に応じて複数のアクセスリクエストを順次生成して発行する。算出装置2−1は、データ転送の総データ量と、予め設定された転送許容時間と、から第1の転送レートを算出する。算出装置2−1は、所定の設定タイミング毎に、イニシエータIP1−1に転送済みのデータ量と、イニシエータIP1−1がデータ転送を開始してからの経過時間と、から第2の転送レートを算出する。算出装置2−1は、第1の転送レートと、第2の転送レートと、の比較結果に基づいて、イニシエータIP1−1が発行前のアクセスリクエストに対応付ける重みづけを設定する。調停回路4は、アクセスリクエストに対応付けられた重みづけに基づいて、転送処理の調停を行う。

(もっと読む)

アイソレーションメモリバッファを組み込んだロードリデュースド・デュアル・インライン・メモリ・モジュール(LR−DIMM)を利用したスイッチ/ネットワークアダプタ・ポートインターフェースを含むヘテロジニアスコンピューティングシステム

【課題】アイソレーションメモリバッファを組み込んだLR−DIMMを利用したスイッチ/ネットワークアダプタ・ポートインターフェースを含むヘテロジニアスコンピューティングシステムを提供する。

【解決手段】コンピュータシステム100は、少なくとも1つの高密度ロジックデバイス106及びメモリバスに高密度ロジックデバイスを接続するコントローラを備える。複数のメモリスロットがメモリバスと接続され、アダプタポートが複数のメモリスロットのうちの少なくとも一部と関連付けられ、アダプタポートの各々は、関連付けられたメモリリソースを含む。ダイレクト・エクセキューション・ロジック要素108は、アダプタポートのうちの少なくとも1つと接続される。メモリリソース110は、少なくとも1つの高密度ロジックデバイス及びダイレクト・エクセキューション・ロジック要素によって、選択的にアクセス可能である。

(もっと読む)

組込み型チャネル選択を備えるマルチチャネルメモリ

【課題】マルチチャネルメモリデバイス、及び、マルチチャネルデバイスの1つ又は複数のチャネルを選択する方法を提供する。

【解決手段】メモリデバイスに組み込まれたスイッチインターフェース(SI)レジスタ147は、複数のインターフェースの特権レベルを管理する。SIレジスタ147は、インターフェースに帰する特権レベルに関係なく、複数のインターフェースを介してアクセス可能であってもよい。ステータスレジスタ149はステートマシーンビジービットを含み、デュアルチャネルメモリにおいて、どちらかのインターフェースは、ステータスレジスタ149をいつでも読み出してもよく、一方では、メモリアレイ143にアクセスする比較的高い特権レベルを有するインターフェースのみが、ステータスレジスタ149に書き込んでもよい。

(もっと読む)

マルチプロセッサシステム、メモリ管理方法、および、メモリ管理プログラム

【課題】システム全体として、メモリアクセスのレイテンシを小さくすることのできるマルチプロセッサシステムを提供する。

【解決手段】あるプロセッサ8が別のノードのメインメモリ9にアクセスしたのをトリガとして、プロセッサ8がアクセスしたデータをそのメインメモリ9から取得して、アクセスしたプロセッサ8と対になったメインメモリ9に移動するアクセスデータ移動手段と、アクセスデータを格納するメインメモリ9から一部データを廃棄してアクセスデータを格納するための容量を確保する格納容量確保手段と、廃棄したデータを替わりに格納するためのメインメモリ9を複数のメインメモリ9の中から選択する格納メモリ選択手段と、選択したメインメモリに廃棄したデータを格納する廃棄データ格納手段を有するメモリ管理機構10をプロセッサ8とメインメモリ9の間に設置する。

(もっと読む)

計算機システム、計算機間メモリコピー方法、及びスイッチ

【課題】マイグレーション時に生じるI/Oデバイスからのメモリ変更に依る再コピーを仮想計算機環境に依らずに防止する。

【解決手段】第一の計算機10aと第二の計算機10bが第一のスイッチ20aおよび第二のスイッチ20bを経由して複数のI/Oデバイス30a,30bに接続されている計算機システムであって、第一のスイッチ20aのメモリコピー制御部201aが、実行するメモリのコピー情報を、コピー中領域情報と、複製領域情報として第二のスイッチ20bに通知し、第二のスイッチの複製制御部202bは、I/Oデバイス30bからデータを受信した際に、通知されたコピー中領域情報と複製領域情報に基づき、自律的にトランザクションの転送・複製・保留を行う。

(もっと読む)

FIFOデータ読出装置

【課題】1個のFIFO回路に格納されているデータを複数のCPUが互いに独立して読出せるFIFOデータ読出装置を提供する。

【解決手段】CPU2およびCPU4によるFIFO回路12に対する読出要求は、FIFO読出回路20により処理される。FIFO回路12に対するCPU2による総読出回数がCPU4による総読出回数以上であれば、FIFO読出回路20はFIFO回路12からデータを読み出してCPU2に送出するとともに、CPU4用のDPRAM32にそのデータを書き込む。CPU2による総読出回数がCPU4による総読出回数よりも小さい場合、CPU2によるFIFO回路12に対する読出要求に対応するデータは、すでにCPU4に送出されているとともにCPU2用のDPRAM30に書き込まれているので、FIFO読出回路20は、DPRAM30の該当アドレス位置からデータを読出してCPU2に出力する。

(もっと読む)

アクセス管理装置、情報処理装置、アクセス管理方法

【課題】複数のプロセッサが共有リソースにアクセスする際の調停頻度を、キャッシュやバッファを抑制するアクセス管理装置、情報処理装置及びアクセス管理方法を提供すること。

【解決手段】複数のプロセッサ11から要求された共通のリソース16へのアクセス要求を制御するアクセス管理装置100であって、複数のプロセッサ11から受け付けたリードアクセスの複数のアドレスを比較するアドレス比較手段13と、複数のアドレスのうち一致したアドレスのデータをリソース16からリードするデータリード手段14と、データリード手段14がリードしたデータを、一致した複数のアドレスを出力した複数のプロセッサ11に同じタイミングで出力するデータ出力手段15と、を有することを特徴とする。

(もっと読む)

メモリー制御装置、メモリー制御システム、記録装置及びメモリー制御方法

【課題】ダイナミックRAMにアクセスする際のレイテンシーを改善することができるメモリー制御装置、メモリー制御システム、記録装置及びメモリー制御方法を提供する。

【解決手段】複数のマスターM1〜MnとDRAMとの間に介在するメモリーコントローラー37は、メモリーシーケンス制御回路64とレイテンシー改善回路67等を備える。レイテンシー改善回路67は、マスター数判定回路71と、ページヒット率判定回路72と、ページ制御回路73とを備える。マスター数判定回路71は特定時間におけるアクセスマスター数が有効バンク数(例えば「8」)以下であるか否かを判定し、ページヒット率判定回路72はページヒット率が設定値Q(本例では50%)以上であるか否かを判定する。ページ制御回路73は両条件成立時にページオープン制御信号Sopenを出力し、一方の条件でも不成立であるとページクローズ制御信号Scloseを出力する。

(もっと読む)

メモリ管理装置及び方法

【課題】プロセッサで用いられるアドレス空間を拡張する。

【解決手段】メモリ管理装置35は、プロセッサ3bのプロセッサ論理アドレス空間PLA1に含まれるメモリウィンドウMW1に配置される各データの特性に基づいて生成され、当該各データの配置領域を決定するヒントとなる配置ヒント情報38を記憶する第1の記憶部17と、各データに対する配置ヒント情報38を生成する第1の管理部15と、配置ヒント情報に基づいて、メモリウィンドウMW1からプロセッサ物理アドレス空間34に書き込まれるデータに対して、プロセッサ物理アドレス空間34の中から、書き込み領域を決定する第2の管理部15と、各データのプロセッサ論理アドレスとプロセッサ物理アドレスとを関連付けたアドレス変換情報39を、第2の記憶部17に記憶する第3の管理部15とを具備する。

(もっと読む)

マルチプロセッサシステムおよびマルチプロセッサシステムのプログラム

【課題】 マルチプロセッサシステムの計算処理の効率を向上させる。

【解決手段】 マルチプロセッサシステムは、第1メモリと、第1メモリに接続され、第1メモリに記憶されたデータを用いて処理を実施する処理部とを有している。処理部は、第2メモリと、データおよび処理の結果である処理データの少なくとも一方を第1メモリと第2メモリとの間で転送するデータ転送を実施する第1プロセッサと、第1メモリと第2メモリとの間でのデータ転送と処理とを切り替え可能に実施する第2プロセッサと、第2メモリに転送されたデータを用いて、処理を実施する第3プロセッサとを有している。

(もっと読む)

メモリアクセス制御システムおよびメモリアクセス制御方法

【課題】効率的なメモリアクセスを行う。

【解決手段】アクセス頻度通知部200が、CPU100から主記憶400−1〜400−2へのアクセス頻度を、主記憶400−1〜400−2にあらかじめ設定されたアドレスごとに監視し、監視したアクセス頻度があらかじめ設定された頻度閾値を超えたアドレスがある場合、CPU100へ通知を行い、そのアドレスをレジスタに保持し、アクセス頻度通知部200からCPU100へ通知があった場合、割り当て変更部300が、レジスタに保持されているアドレスに基づいて、CPU100における主記憶400−1〜400−2のアドレスの割り当てを変更する。

(もっと読む)

計算機システム

【課題】 高密度実装するサーバモジュールのメモリ容量の増設を容易にする。

【解決方法】 メモリ容量を追加するためのメモリ増設モジュールをサーバシステムに備えることにより、サーバブレードのCPUには通常のメモリと認識可能な外部メモリの増設手段を持ち、複数のサーバブレードで1つのモジュールを共有することにより、複数のサーバブレードのメモリ容量を増設が可能なサーバシステム。

(もっと読む)

複数メモリ特定用途向けデジタル信号プロセッサ

回路基板(210)と、この回路基板上に実装された1又はそれ以上のデジタル信号プロセッサ(100)とを含む集積回路装置(200)を提供する。デジタル信号プロセッサ(100)は、データユニット(120)及び制御ユニット(110)を含み、データユニットは、特定のアプリケーションの少なくとも一部を実行するために特定の数式を実行するように構成された関数コア(124)と、特定のアプリケーションを実行するためのコマンドを制御ユニット及びデータユニットに送信するように構成された1又はそれ以上の命令を記憶する命令メモリ(122)とを含み、制御ユニットは、複数のメモリバンク(130、140)と関数コアの間の、特定のアプリケーションを実行するためのデータの流れを制御するように構成され、複数のメモリバンクは、1又はそれ以上のデジタル信号プロセッサの各々に結合されるとともに、回路基板上に統合された少なくとも2又はそれ以上のローカルメモリバンク(130)を含む。 (もっと読む)

不均一ページサイズを有する多チャンネルメモリシステムへのアクセス

方法は、複数のマスターの各マスターのメモリアクセスパターンを予測するステップを含む。複数のマスターは、クロスバー相互接続部を介して多チャンネルメモリにアクセスすることができ、その多チャンネルメモリは、複数のバンクを有する。本方法は、複数のバンクの各バンクと関連するページサイズを識別するステップを含む。本方法はまた、各マスターのメモリアクセスパターンに基づいて複数のバンクの少なくとも1つのバンクを複数のマスターの各マスターに割り当てるステップも含む。  (もっと読む)

(もっと読む)

ローカル物理メモリとリモート物理メモリとの間で共有されるバーチャルメモリのためのハードウェアサポートの提供

【課題】ローカル物理メモリとリモート物理メモリとの間で共有されるバーチャルメモリのためのハードウェアサポートを提供すること。

【解決手段】本発明の一態様は、バーチャルアドレスを含むメモリアクセスリクエストを受信するステップと、前記バーチャルアドレスに対応する物理アドレス(PA)がプロセッサに付属されるローカルメモリ又は非コヒーラントリンクを介し前記プロセッサに接続されるアクセラレータに付属するリモートメモリに存在するか判断するため、前記プロセッサの変換ルックアサイドバッファ(TLB)に格納される前記バーチャルアドレスに対応するエントリを解析するステップと、前記PAが前記リモートメモリに存在する場合、前記メモリアクセスリクエストを実行するため、リバースプロキシ実行リクエストを前記リモートメモリに送信するステップとを有する方法であって、前記ローカルメモリと前記リモートメモリとは、一緒になって共有バーチャルメモリスペースを構成する方法に関する。

(もっと読む)

コンピュータのメモリ再配置制御方法およびプログラム並びにコンピュータシステム

【課題】コンピュータの使用量が減った際に積極的に省電力状態に遷移させることが可能となり、コンピュータの使用電力の削減を可能とする。

【解決手段】コンピュータシステムは、1個または複数のCPUコア、メモリコントローラ、メモリ、及びクロスバスイッチを備えたCPUソケットを複数接続して構成されるコンピュータを有する。コンピュータは、あるCPUソケット内のCPUコアが全て省電力状態になった場合、メモリの全体使用容量が予め定められたしきい値を下回ったときに、該当CPUソケット配下に接続されているメモリの内容を他のCPUソケット配下のメモリに再配置することにより、該当CPUソケット配下に接続されているメモリへのアクセスをなくし、該当CPUソケット全体を省電力状態に遷移させる。

(もっと読む)

1 - 20 / 186

[ Back to top ]