Fターム[5B060MM09]の内容

メモリシステム (7,345) | メモリモジュール構成、管理技術 (856) | 着脱可能、メモリカード、カートリッジ (138)

Fターム[5B060MM09]の下位に属するFターム

接続部、コネクタ部に関するもの (23)

Fターム[5B060MM09]に分類される特許

1 - 20 / 115

メモリモジュール

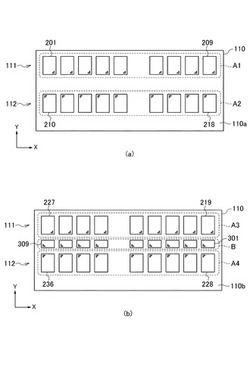

【課題】Load Reduced型のメモリモジュールにおいてメモリデバイスの搭載位置によるデータのスキューを低減する。

【解決手段】データコネクタを有するモジュール基板110と、複数のメモリデバイス201〜236と、データコネクタとメモリデバイスとの間に接続されたデータレジスタバッファ301〜309とを備える。モジュール基板110は、メモリデバイスが搭載されたメモリ搭載領域A1,A2と、平面視でメモリ搭載領域A1,A2に挟まれた位置に定義され、データレジスタバッファが搭載されたレジスタ搭載領域Bとを有する。各メモリデバイスとデータレジスタバッファとの配線距離がほぼ均一になるため、メモリデバイスの搭載位置によるデータのスキューが低減される。

(もっと読む)

メモリデバイスに対する電力制御

【課題】余分のピンを使用すること、およびそれに関わる費用は、ある厳しい予算の環境下で、チップサイズおよび回路基板の大きさが決定的な要因である場合には、関心事項になる。

【解決手段】電力コントローラは、異なるタイプのメモリデバイスに異なるレベルの電力を供給するように構成される。電力コントローラは、メモリデバイスに供給する電力を制御する制御モードを選定する選定ユニットを含む。選定ユニットは、モード信号を受信するように構成された第1の入力と、いくつかの制御モード信号を受信するように構成された複数の制御入力と、メモリデバイスに電力を出力するように構成された複数の出力とを含む。選定ユニットは、受信したモード信号に従って制御モードを選定し、制御モード信号に従って電力を出力する。

(もっと読む)

メモリシステム、メモリ制御方法及びメモリ制御プログラム

【課題】本発明は、JEDEC準拠とJEDEC非準拠の双方のDIMMのメモリ制御を適切に行う。

【解決手段】メモリシステム1は、DIMMコネクタ4に着脱可能に装着されているDIMM10がJEDEC準拠DIMMとJEDEC非準拠DIMMのいずれであるかのDIMMの種別をメモリコントローラ3が判別し、メモリコントローラ3が、該DIMM10に搭載され該DIMM10の構成情報及び搭載メモリチップの情報等を格納するSPDに格納されている情報を読み取って、該SPDの情報及び該DIMM種別判別の判別結果に基づいて該DIMM10のアクセス制御を行う。

(もっと読む)

メモリシステム

【課題】メモリアクセスを伴うデータ処理効率向上に寄与するメモリシステムを提供する。

【解決手段】書換え可能な不揮発性メモリ(2)、バッファメモリ(5)及びコントローラ(4)を有する。コントローラは外部装置に接続される第1データ転送制御部(11)、不揮発性メモリに接続される第2データ転送制御部(12)、及び第1データ転送制御部からの転送要求と第2データ転送制御部からの転送要求に応答してバッファメモリとの間のデータ転送を制御する転送調停部(13)を有する。前記第1データ転送制御部は外部装置と転送調停部に接続され、転送調停部に転送要求を出力する。第2データ転送制御部は不揮発性メモリと転送調停部に接続され、転送調停部に転送要求を出力する。転送調停部は、第1データ転送制御部からの転送要求と第2データ転送制御部からの転送要求に対し、バッファメモリに対する書き込みと読み出しの転送を時分割で制御する。

(もっと読む)

情報処理装置、その制御方法およびプログラム

【課題】メモリモジュールへのアクセス性能を低下させることなく、メモリモジュールの消費電力を削減すること。

【解決手段】情報処理装置は、第1の状態と該第1の状態よりも消費電力の少ない第2の状態とを有するメモリモジュールと、メモリモジュールに対するアクセスが発生しなかった期間の平均値をアクセス未発生平均期間として保持するとともに、メモリモジュールへのアクセスが発生した場合には、メモリモジュールへの前回のアクセスから今回のアクセスまでの期間をアクセス未発生期間として計測するとともに、アクセス未発生平均期間を更新して保持する平均期間記録部と、アクセス未発生平均期間が所定の閾値以上である場合は、メモリモジュールを第1の状態から第2の状態へ遷移させるメモリモジュール制御部と、を備えている。

(もっと読む)

半導体記憶システム

【課題】複数のチップを実装した場合において、回路構成の増大を抑えて確実且つ十分にピーク電流を抑制可能な半導体記憶システムを提供する。

【解決手段】制御回路73は、第1、第2の半導体記憶装置71、72に接続されている。電圧発生回路90は、制御回路73に設けられ、電圧を発生する。制御回路73は、第1、第2の半導体記憶装置71、72の一方に電圧発生回路90からの電圧を供給する。

(もっと読む)

ICチップ、ICチップにおけるメモリ初期化方法、ICチップ用処理プログラム、携帯端末

【課題】インターフェースが行う処理動作に影響を与えることなく、効率よくメモリを初期化可能なICチップ等を提供する。

【解決手段】複数のインターフェースを備え、各インターフェースが非同期に他の通信端末と通信するために動作するICチップであって、すべての前記インターフェースの動作処理に用いられる共通の情報が記憶される共通領域、各インターフェースの動作処理のみで用いられる情報が記憶される専用領域、とを有するメモリと、1のインターフェースの起動を検出する第1の検出手段と、検出した前記インターフェースの起動後、各インターフェースの動作状態を検出する第2の検出手段と、前記各インターフェースの動作状態に応じて、当該共通領域又は少なくとも1のインターフェースの専用領域を初期化する初期化手段と、を備えている。

(もっと読む)

記憶装置

【課題】記憶しているデータを他の装置との間で送受信する機能を無線通信により実現し、さらに、ユーザがこの機能の開始指示等を簡単な操作で行うことが可能で、なおかつ接続される機器に関係なくこの機能をユーザに使用させることが可能な記憶装置を提供する。

【解決手段】記憶装置1は、無線通信機能を提供する無線通信処理部16およびメモリ15と、加速度センサ12と、ブザー11と、加速度センサ12から出力される加速度情報に基づきユーザによる操作を検出し、当該検出結果に基づいて、前記メモリ15へのアクセスを含むファイル管理動作を開始するか否か、および前記ブザー11を鳴動させるか否かを判定する制御部13と、を備えている。

(もっと読む)

ランダムアクセス動作及びファイル格納動作をサポートする分散型メモリアレイ

【課題】ランダムアクセス動作及びファイル格納動作をサポートする分散型メモリアレイを提供する。

【解決手段】分散型メモリアレイ102は、データを格納するメモリアセンブリ125を備え、各メモリアセンブリ125は双方向交差ストラップ式ネットワークを介して共に結合された複数のメモリモジュールを有し、各メモリモジュールはスイッチングメカニズムを有する。メモリアセンブリ125と結合されたゲートウェイ117をさらに備える。ゲートウェイ117は、メモリアセンブリ125へのアクセスを提供する複数のユーザーアクセスポートと、ユーザーアクセスポートにおいて、ユーザーからファイル格納動作又はランダムアクセス動作のいずれかのためのメモリアセンブリ125へのアクセス要求を受信するように、かつ、メモリアセンブリ125における利用可能なメモリの割当てユニットを割り当てるように構成されたファイルマネージャーとを備える。

(もっと読む)

メモリ装置

【課題】空きソケットとなっている第2ソケットでの信号の反射を抑制可能なメモリ装置を提供する。

【解決手段】メモリモジュール2が接続されたソケット3と、空きソケットとなっているソケット4と、コントローラ5とは、接続配線6によって接続されている。接続配線6は、ソケット3とコントローラ5とを接続する配線6aと、配線6aから分岐点6bで分岐しソケット4と接続する配線6cと、を備える。配線6cには、ダミー配線7の一端7aが接続され、ダミー配線7の他端7bは、終端抵抗8に接続されている。

(もっと読む)

半導体装置

【課題】スタブ配線の形成による信号波形の劣化を改善可能な半導体装置を提供する。

【解決手段】第1の信号経路Fが第1の入力端Faに対応して分岐を有さない1本の経路として形成され、複数の第1の入力端Faとこれに対応する複数の半導体パッケージD1の複数の第1の端子T1とが各々複数の第1の信号経路Fのうちの対応する1つによってフライバイ形式にて接続される。半導体パッケージパターン等の構成に限定されるものではなく、分岐を有さない1本の経路としてフライバイトポロジ(Fly−by Topology)が実現可能なものであれば、他の構成とすることも可能である。

(もっと読む)

メモリモジュール及び半導体記憶装置

【課題】アドレス信号と制御信号のタイミングの不一致に起因する誤動作が防止できるメモリモジュールを提供する。

【解決手段】メモリモジュールに、データを入出力する単位である複数のランクに区分けされた複数の半導体記憶装置と、全ランクの半導体記憶装置が縦列接続される、外部から入力されたアドレス信号を該半導体記憶装置に供給するための配線であるアドレス信号配線と、ランク単位で半導体記憶装置が縦列接続される、外部から入力された制御信号を該半導体記憶装置に供給するための配線である制御信号配線と、制御信号配線と接続された各半導体記憶装置に対応して設けられた、半導体記憶装置の入力容量と(ランク数−1)との積に等しい容量を持つ容量部とを備える。

(もっと読む)

電子機器

【課題】アクセスを制御する半導体部品に負担をかけることなく当該半導体部品が出力する信号の高調波成分によって当該信号によるタイミングウインドウが不所望に狭められことを抑制する。

【解決手段】基板上でアクセスを制御する半導体部品が出力するクロック信号やコマンド及びアドレス信号の有効性を示すイネーブル制御信号を基板上でアクセスされる別の半導体部品に供給する信号伝送経路の所定ノードから分岐してグランドプレーンに至る特定伝送経路に容量素子を直列配置する。前記容量素子は、イネーブル制御信号の高調波成分に対してグランドプレーンへのショート経路として機能し、当該容量素子がない場合に比べて前記イネーブル制御信号のスルーレートを小さくし且つそのタイミングウインドウを大きくする。

(もっと読む)

携帯可能電子装置及び携帯可能電子装置の制御方法

【課題】 ICカード処理装置からのコマンドに応じてICカードが不揮発性メモリ上のデータ格納領域へのデータの書き込みを行う処理に要する時間を短縮することができる。

【解決手段】 外部装置から受信したコマンドに基づいてデータを不揮発性メモリ上のデータ格納領域に書き込む必要がある場合、不揮発性メモリ上のバッファ領域に当該データを書き込み、上記バッファ領域へのデータの書き込みが終了した際にバッファ領域への書き込み完了を示す応答データを外部装置へ出力し、当該データをデータ格納領域に書き込むようにしたものである。

(もっと読む)

非ソースシンクロナスインターフェイスのための入出力の強化

1つのインターフェースを有するハイブリッド・メモリ・デバイス

【課題】メモリ・コントローラを、SDRAMとフラッシュ・メモリを内部に有するハイブリッド・メモリ・デバイスの一構成要素とする。

【解決手段】コントローラ308Bは、標準的なSDRAMインターフェースを有するメモリ・デバイスがSDRAM304とフラッシュ306A,306Bへのアクセスを与えることを可能にし、SDRAMアドレス空間の1つ以上の指定ブロック320A,320BにおいてSDRAMを無効にする。コマンド・プロトコルは、メモリ・ページをSDRAMインターフェース・アドレス空間にマッピングし、フラッシュ・メモリを設けることを望む計算機において、1つのピン互換マルチチップ・パッケージと既存のSDRAMとを交換することを可能とし、フラッシュにアクセスするためのソフトウェアの変更が行われる。

(もっと読む)

データ記憶装置およびデータ記憶装置の低消費電力制御方法

【課題】可及的に消費電力を低減すること。

【解決手段】パワーマネジメント部(SATAC111およびMPU114)は、ホスト装置200から読み出し要求を受信したとき、読み出し要求されたデータをNANDメモリ130からRAM120へ転送させるNANDC転送指令をNANDC113に送信するとともに低消費電力モードへ移行し、NANDC113が前記転送を完了したとき、低消費電力モードから復帰して、RAM120に転送されたデータをホスト装置200へ転送する。

(もっと読む)

取替え可能な複数の不揮発メモリを装着したメモリ・システム

【課題】半導体用フォトマスクの欠陥検査装置等の大量の画像データを収集し、その画像データに基づいてコンピュータがフォトマスク上の欠陥を検出する装置などでは、画像データの任意の部分に直接アクセスできる一次記憶装置、即ちメモリ上にその全てを収納できるならばデータ処理の利便性が飛躍的に向上する。

【解決手段】メモリボード1に複数のソケット2を装着し、そこにSDカードなどの取り外し可能な不揮発性メモリ・カードを装着する。それをメモリボードの中心部に設けた制御回路4で制御することにより装着したメモリの容量の総合計が全体の容量となるメモリ・システムを構築した。

(もっと読む)

終端基板、メモリシステム及びその反射波抑制方法

【課題】メモリコントローラに対して複数のメモリスロットが並列にバス接続されるメモリシステムの空きスロットからの反射波を抑制する。

【解決手段】

空きスロットに終端基板を挿入する。終端基板は、メモリモジュールの挿入部と同一に構成された挿入部と、挿入部に含まれる複数の信号系接栓の各々に一端が接続され、かつ他端が挿入部に含まれる複数の電源系接栓のいずれかに接続されている複数の抵抗素子とを備える。

(もっと読む)

情報処理装置およびメモリ制御方法

【課題】複数のメモリモジュールに対して最適な制御を行うことができる情報処理装置およびメモリ制御方法を提供する。

【解決手段】コンピュータが起動した後の状態であり、かつコンピュータが備えるオペレーティングシステムの起動前の状態において、メインメモリ112である複数のメモリモジュールの夫々に同等の負荷を掛けて初期化を行い、初期化時における複数のメモリモジュールの夫々の温度の値を測定すると共に、オペレーティングシステムの稼働時における複数のメモリモジュールの夫々の温度の最大値を測定する。測定された温度の値に基づいて、chB内において、初期化時とオペレーティングシステムの稼働時との温度の値の差が一番小さいメモリモジュールDIMM3、および初期化時の値が一番小さいメモリモジュールDIMM4を判別し、メモリモジュールDIMM3に割り当てられていたメモリアドレス空間をメモリモジュールDIMM4にマッピングする。

(もっと読む)

1 - 20 / 115

[ Back to top ]