Fターム[5B061BC07]の内容

Fターム[5B061BC07]に分類される特許

1 - 20 / 27

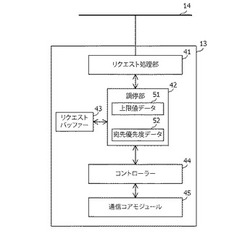

電子機器

【課題】 シリアルバスシステムにおけるリードレイテンシーの異なる複数の宛先に対する複数のリードリクエストが混在しても、各宛先に対するリードリクエストが円滑に処理されていくようにする。

【解決手段】 リクエストバッファー43は、所定の数のリクエストをキューイング可能であって、リクエストの宛先ごとに未処理リードリクエストの数の上限値を設定されている。調停部42は、新たなリードリクエストが受け付けられると、受け付けられたリードリクエストの宛先を特定し、特定した宛先についてのリクエストバッファー内の未処理リードリクエストの数が、特定した宛先についての上限値に到達している場合には、特定した宛先より優先度の低い宛先についての上限値を低くした上で、特定した宛先についての上限値を高くする。

(もっと読む)

バスアービタ、バスアービタシステム、バスアービタの処理方法

【課題】同程度の優先度の複数のバスマスタに対し、より優先度の高いバスマスタの使用効率を圧迫しないアービタを提供すること。

【解決手段】共通のバス12に接続されている複数のバスマスタ110からのバス獲得要求を、予め設定されている各バスマスタの優先度に基づき調停するバスアービタ100であって、優先度が最も高い第一のバスマスタからの第一のバス獲得要求、及び、前記第一のバスマスタと同等の優先度である第二のバスマスタからの第二のバス獲得要求を監視するバス獲得要求監視手段14と、前記バス獲得要求監視手段の監視結果を取得して、前記第一のバス獲得要求の頻度及び前記第二のバス獲得要求の頻度が予め定められた基準を満たす特定事象を検知する特定事象検知手段15と、前記特定事象検知手段から特定事象検知信号を取得して、前記第二のバス獲得要求の頻度を制限するバス獲得制御手段13と、を有することを特徴とする。

(もっと読む)

画像形成装置

【課題】画像の印刷時にアンダーランをより確実に防止することが可能な画像形成装置を提供する。

【解決手段】第1のDMA制御部17は、転送要求R1の時にFIFO25に一時蓄積されている黒成分データの量を主走査ライン数に換算した情報I1を、転送要求R1と一緒にバス調停部35に送る。第2のDMA制御部19Cは、転送要求R2の時にFIFO31Cに一時蓄積されているシアン成分データの量を主走査ライン数に換算した情報I2を、転送要求R2と一緒にバス調停部35に送る。前記第1のDMA転送要求と前記第2のDMA転送要求とが競合した場合、情報I1で示される主走査ライン数が情報I2で示される主走査ライン数よりも小さければ、第1のDMA制御部17にバス21の使用権が与えら、情報I2で示される主走査ライン数が情報I1で示される主走査ライン数よりも小さければ、第2のDMA制御部19Cにバス21の使用権が与えられる。

(もっと読む)

調停装置、画像形成装置、調停方法及びプログラム

【課題】優先順位の異なる複数のDMACからの転送要求を調停するときに、システム全体のパフォーマンスを向上させる。

【解決手段】第1のライトDMAC15は、1ライン単位で入力されるデータを1ライン期間内にメモリに転送させる必要がある。アービタ113内の必要転送時間計算部121は、バースト長と、バス幅と、必要転送レートRaとから、要求されたデータの転送に必要な時間T2を計算する。また、ラインスタート信号により起動されるタイマーにより、1ラインの開始からの経過時間T1を計測する。T1の方がT2より長ければ、T1とT2が等しくなるまで、第1のライトDMAC15からの転送要求に対して、ウェイト要求信号をアサートする。

(もっと読む)

中継装置およびプロセッサーシステム

【課題】先入れ先出し方式のバッファーをより適切に構成して効率的にリクエストを中継する。

【解決手段】転送元であるマスターデバイス30側からのリクエストの分配を行なうTブリッジ42と、Tブリッジ42から分配されたリクエストを転送先であるスレーブデバイス80側に転送するIブリッジ46とを備えて通信を中継するクロスバースイッチ40において、Tブリッジ42のT−B0内に各スレーブデバイスの共用のFIFO43aを構成し、Tブリッジ42とIブリッジ46との間に各スレーブデバイスの専用のFIFO45a〜45cを構成するから、転送先のスレーブデバイスが受け入れ可能な状態になくリクエストの転送待ちが生じる場合であっても、他のスレーブデバイスに転送されるリクエストが転送待ちとなるのを減少させることができる。

(もっと読む)

データ転送制御装置およびデータ転送制御方法

【課題】共有バスに接続する複数のDMAチャネルがあって、SDRAM等のメモリにアクセスする際に、あらかじめ決められた優先順位を守りながら、高効率にメモリアクセスする調停手段を提供する。

【解決手段】マスターデバイスからのデータ転送要求を一定量保持する要求保持部と、保持されたデータ転送要求を優先順位及び予め定められた回数だけ連続するように並び替える要求並び替え部とを備え、前記データ転送要求を前記要求並び替え部が並び替えた順で発行することで、優先順位に応じて複数チャネルを並び替えるとともに同格の優先順位を持つ複数チャネルを平均的に連続させることができる。

(もっと読む)

リクエスト発行ノード、リクエスト受信ノード、システム、及び制御方法

【課題】 システム性能の低下の問題を解決するリクエスト発行ノード、リクエスト受信ノード、システム、及び制御方法を提供する。

【解決手段】 本発明のリクエスト発行ノードは、リクエストをリクエスト受信ノードに送信するリクエスト送信手段と、リクエストに対するリプライをリクエスト受信ノードから受信した場合に、リクエストを格納したリクエスト受信ノード内のリクエスト格納場所を開放させるリクエスト開放指示をリクエスト受信ノードに送信するリクエスト開放指示送信手段と、リクエスト受信ノード内の所定の数のリクエスト格納場所の全てが使用中となった場合に、リクエストの送信とリクエスト開放指示の送信とが競合したときには、優先する送信をリクエストの送信からリクエスト開放指示の送信に切り替える調停手段とを含む。

(もっと読む)

バス調停装置

【課題】共通バス方式を使用する場合において、低コストを実現するだけでなく、効率よくバスを使用して高パフォーマンスを実現できるバス調停装置を提供する。

【解決手段】DMAデータ転送を制御するDMA制御手段によるDMAアクセスと、CPUによるCPUアクセスとの両方に共通で使用される共通バスと接続され、共通バスにおけるDMAアクセスとCPUアクセスとの間のバス調停を行うバス調停装置であって、CPUの処理量に応じて、DMAアクセスとCPUアクセスとの間のバス調停の割合を変更する。

(もっと読む)

マルチCPUバス占有方式

【課題】安価な構成にて複雑膨大な負荷を高速処理することが可能なマルチCPUバス占有方式を提供すること。

【解決手段】共有メモリ5が接続されているバス1に複数のCPU2,3,4を接続すると共に、いずれかのCPUをマスタCPU2、他のCPUをスレーブCPU3,4となし、マスタCPU2により、バス解放、バス使用のウエイト、およびスレーブCPU3,4のバス占有許可を、所定のラダープログラムに従い、制御するシステム。

(もっと読む)

バスシステム

【課題】複数のマスタからのバスアクセスの順番を制御して、アクセスの効率を高めるとともに、優先度の高いマスタからの要求が後回しにされることによって、システム全体の処理に不具合が生じることを防止したバスシステムを提供する。

【解決手段】バスシステムBS1は、N個のマスタMSからの情報を選択してSDRAMコントローラSCに与えるマルチプレクサMUXと、データ転送要求のあるマスタのうち1つを選択してバス権を与えるバス権調停部AR1を備えている。また、pri信号比較部PC1と、追い越し監視・記録部OV1と、バンクアドレス監視部BAMと、前回アクセスバンクアドレス保持部BAHと、優先順位設定レジスタRS1、再追い越し禁止期間設定レジスタRS2およびバンクアドレス位置指定レジスタRS3を有するレジスタ部RSPとを備えている。

(もっと読む)

バスマスターシステム、コンピュータ装置、アクセス調停方法およびアクセス調停プログラム

【課題】複数のバスマスターが同一の資源にアクセスするコンピュータ装置において、いずれのバスマスターも該資源にアクセスしない無駄なタイミングの発生を抑制して、装置全体としての動作効率を向上させることができるバスマスターシステムを提供する。

【解決手段】本発明に係るバスマスターシステム1は、複数のバスマスター10〜15と、複数のバスマスターによって共有されるコンピュータ資源17と、複数のバスマスターの各々に対応し、コンピュータ資源にアクセスしようとするバスマスターがデータを記録するフラグ20〜25と、固定タイミングに該当するバスマスターに対応するフラグにデータが記録されていれば該バスマスターにコンピュータ資源へのアクセスを許可し、記録されていなければ該バスマスター以外のバスマスターにコンピュータ資源へのアクセスを許可する調停装置16とを有する。

(もっと読む)

バスシステム

【課題】システムバスを介して接続されたマスタモジュールと複数のスレーブモジュールのいずれかとの間で、前記マスタモジュールのコマンドに基づいてデータ信号が送受信されるように構成されたバスシステムにおいて、データ転送効率を向上させること。

【解決手段】スレーブモジュール2A、2Bは、マスタモジュール1へ自身の負荷状況を通知し、マスタモジュール1は、スレーブモジュール2A、2Bに対するコマンドの優先度を負荷が高くなるにしたがって引き下げる。

(もっと読む)

プロセッサシステム、バス制御方法および半導体装置

【課題】共有メモリにアクセスする複数のマスターユニット間で共有メモリへのアクセス性能を均等に分散し、しかも簡単な構成のマルチプロセッサシステムを提供する。

【解決手段】

共有メモリをアクセスするためのアクセス要求を発行する複数のマスターユニットPU0、PU1と、前記アクセス要求を受理するリクエストフェーズと、受理されたアクセス要求に従ってデータ転送する転送フェーズとを分離して実行するスプリット・トランザクション型のバスIF部4−10とを備え、前記バスIF部4−10は、1つのマスターユニットから所定の期間を空けずに複数のアクセス要求が連続して発行された場合に、当該複数のアクセス要求に対応する転送フェーズの連続実行回数をN回までに制限する。

(もっと読む)

競合調停装置、マスタスレーブシステム及び競合調停方法

【課題】 複数のマスタデバイスからスレーブデバイスへの要求を調停する競合調停装置において、複数のマスタデバイス上のタスクの実行順序に依存関係があるときにも、それに対応した調停が可能な競合調停装置を提供する。

【解決手段】 複数のマスタデバイス101〜103の動作状態の組合せに応じた競合処理内容を予め設定しておいたテーブルを元に基本優先度を導出する。マスタデバイス101〜103上で待ち状態となっているタスクが絡む依存関係を考慮するための補正を基本優先度に対して行うことにより最終優先度を決定する。決定した最終優先度を各マスタデバイス101〜103からのアクセス要求に割り付ける。

(もっと読む)

バスシステム

【課題】バスシステムにおけるマスタ装置は、スレーブ装置における状態変化のため、リード動作を周期的に行うので、負荷が大きい。

【解決手段】スレーブ側のLSI24は、状態検出回路50にて、リード対象状態の発生を検出すると、当該状態を表すデータをシステムバスI/F回路56に書き込むと共に、フラグ出力回路52に対してトリガパルスを出力する。フラグ出力回路52は、リード対象状態が発生すると、このトリガパルスに応じて検出フラグをセット状態とする。検出フラグは信号線38を介してマスタ側のマイクロコンピュータ22に伝達され、フラグ監視部36により検出される。フラグ監視部36が検出フラグのセット状態を検知した場合にのみ、演算処理部30はLSI24のリード対象状態の確認のためのリード動作を行う。

(もっと読む)

プロセッサ及びデータ転送ユニット

【課題】プロセッサコア間でのデータ転送のオーバーヘッドを低減し、プロセッサ全体の処理能力を向上させる。

【解決手段】演算処理または信号処理を行うCPU20と、データを記憶する内蔵メモリ30と、内蔵メモリ30と共有メモリ60の間でデータの転送を実行するデータ転送機構40と、を備えて、データ転送機構40は、CPU20が内蔵メモリ30に書き込んだデータ転送指令を複数のコマンドからなるコマンド列を実行するコマンドチェイン部と、コマンドが所定の監視コマンドのときには、内蔵メモリ30または共有メモリ60に予め設定されたデータを読み込んで、予め設定された比較値と前記データの値が一致するまで当該データの監視を繰り返す監視部と、を備え、コマンドチェイン部は、監視部による監視が完了した後に、コマンド列から次のコマンドを実行させる。

(もっと読む)

優先クラスに応じたダイナミックメモリ管理方法及び装置

【課題】優先クラスに応じたダイナミックメモリ管理方法及び装置に関し、メモリの使用効率を改善し、書き込み/読み出しの制御の簡易化を図る。

【解決手段】メモリ1−1の領域を複数の領域に区分けしたメモリバンクを構成し、各優先クラスで各メモリバンクを共有させ、ポリサ(ライト制御部)1−2は、入力される優先度の異なる複数のクラスのフレームデータを、優先度に応じてダイナミックにメモリバンクに割り当て優先クラス毎に格納する。スケジューラ(リード制御部)1−3は、優先度の高いクラスに割り当てられたメモリバンクに格納されたフレームデータから順に読み出して送信する。バースト的に入力される優先クラスのフレームデータの格納には、該優先クラスに複数のメモリバンクを割り当ててバースト耐性を高める。データの書き込み及び読み出しの制御をメモリバンク単位で行うことにより、制御を簡素化することができる。

(もっと読む)

リクエスト送信制御装置およびリクエスト送信制御方法

【課題】ライブロックを回避することができ、システム停止を防止することを課題とする。

【解決手段】アドレスクロスバスイッチは、受信したアドレスリクエストを一時的にバッファリングするとともに監視して、所定の種別のアドレスリクエスト(例えば、ロングパケットのアドレスリクエスト)を計数する。そして、アドレスクロスバスイッチは、所定の種別のアドレスリクエストの計数値が所定の閾値を超えた場合には(例えば、ロングパケットカウンタが100を超えた場合には)、リトライされたアドレスリクエストのブロードキャストを一定時間停止する。そして、アドレスクロスバスイッチは、ブロードキャスト停止期間が終了すると、受信していた順番にアドレスリクエストのブロードキャストを再開する。

(もっと読む)

データ転送装置

【課題】 画像データを転送するためのデータ転送用の専用バス、及びCPU(プロセッサ)がメモリアクセスを行なう専用バスの両方の信号線が必要となる。

【解決手段】 CPU2はCPUバス12を介して、DMAC3はDMAバス13を介してローカルバスコントローラ5と接続し、ローカルバスコントローラ5は、外部のローカルバス11と接続され、ローカルバス11に外部I/Fコントローラ8、コードROM9、フォントROM10が接続されて、外部I/Fからのデータ転送を行うバスとCPUが使用するコードROM9が接続されるバスとしてローカルバス11を共用する。

(もっと読む)

バス・ブリッジのアビトレーション方法

【課題】 この発明は、バス・ブリッジにIEEE 1394に準拠したバスとの異なる動作バスとが接続されている場合に、IEEE 1394以外のバスにアクセス権が亘らない状況を回避することを目的とする。

【解決手段】 システム内のローカルバスである1次側バスと2次側のバスに相当するバスとのインターフェースを行うブリッジデバイスであり、かつ1デバイスで2種類以上の異なる動作をサポートし、そのうちの1種類がIEEE 1394に準拠したシリアルバスであるバス・ブリッジのアビトレーション方法であって、2次側のアービトレーションの状態にかかわらず、1次側から2次側へのアクセスの場合はそのアクセスを最優先することを特徴とする。

(もっと読む)

1 - 20 / 27

[ Back to top ]