Fターム[5B061DD11]の内容

Fターム[5B061DD11]に分類される特許

21 - 40 / 165

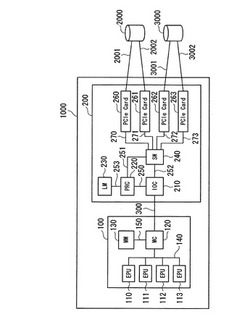

情報処理装置

【課題】メインメモリと周辺装置との間でデータを転送すること。

【解決手段】メインメモリ130を具備する中央処理装置100と、PCI Expressカード260〜263及びローカルメモリ230を具備する入出力処理装置200とを備え、入出力処理装置200は、PCI Expressカード260〜263からメインメモリ130に対して直接データ転送を行う第1の経路と、PCI Expressカード260〜263又はメインメモリ130からローカルメモリ230に一度データ転送した後、メインメモリ130又はPCI Expressカード260〜263にデータ転送を行う第2の経路とを有する。

(もっと読む)

データ転送回路及び方法

【課題】通信路のデータ転送レートを向上させる。

【解決手段】データ転送回路1を構成する制御部10は、一のデータ転送周期で、メモリ3から読み出した周期転送用ポインタ情報P_A及び非周期転送用ポインタ情報P_Bを、第1及び第2の格納領域20及び30にそれぞれ格納する。制御部10は、ポインタ情報P_A及びP_Bをそれぞれ参照してメモリ3から読み出した周期転送用データD_A及び非周期転送用データD_Bを、通信バス4へ順次転送する。データD_Bの転送に際して、ポインタ情報P_Bが示すデータ長分の転送を完了できなかった場合、制御部10は、前記データ長を残りのデータのデータ長に更新すると共に、ポインタ情報P_Bが示すアドレスを前記残りのデータのメモリ3上のアドレスに更新する。制御部10は、次のデータ転送周期で、ポインタ情報P_Bを参照して前記残りのデータをメモリ3から読み出し、通信バス4へ転送する。

(もっと読む)

データ転送装置、データ転送方法、データ転送プログラム及び記録媒体

【課題】優先順位の異なる複数のDMACからのメモリへのアクセス要求を優先順を変更して適切に調停するデータ転送装置、データ転送方法、データ転送プログラム及び記録媒体を提供する。

【解決手段】ライン同期信号LSYNCと画像先端同期信号FSYNCに基づいて1ライン分の画像データをメモリから読み取って転送するRDMAC134を含む複数のDMAC123、124からのメモリへのリクエストを予め設定されている優先順位に基づいてリクエスト調停部112が調停する場合、画像処理部11の転送データ量監視部136が2つのラインバッファ132がフル状態か否か監視して、該監視結果に基づいて必要転送量計算部105が、上記優先順位の変更の要否を判定し、優先順位制御部111が該判定結果に基づいてリクエスト調停部112の優先順位を制御する。

(もっと読む)

情報処理装置、及び、情報処理方法

【課題】通信のパフォーマンスを低下させることなく、ログの記録を行う情報処理装置、及び、情報処理方法を提供すること。

【解決手段】通信手段により送受信される通信データを格納する通信データ領域をメモリ上に設定する通信領域設定部と、前記通信手段に対し、前記通信データ領域の情報を通知する領域通知部と、前記通信手段により送受信信された通信データが格納された前記通信データ領域を、ログデータ領域に変更し、前記通信データをログデータとするログデータ領域設定部と、を有する情報処理装置。

(もっと読む)

オーディオ処理装置

【課題】リアルタイム性を求められるアプリケーション処理において、ハードウェアコストや制御プログラムの開発負担を削減し、処理性能の低下等の課題を最小限にし、信号処理プロセッサがデータの出力状態を把握できるオーディオ処理装置を提供すること。

【解決手段】オーディオ処理装置100は、音情報とは異なる制御情報を付加情報としてオーディオデータに重畳する付加情報重畳部113と、メモリ120とオーディオデータ出力回路140を接続するデータバスに接続され、オーディオデータに付加された付加情報200を検出する付加情報検出部150とを備える。付加情報検出部150は、検出した付加情報200を付加情報検出状態読出経路117を通じて信号処理プロセッサ110の出力制御部111に出力する。出力制御部111は、付加情報検出部150により検出された付加情報200に基づいてオーディオデータの出力制御を行う。

(もっと読む)

データ処理装置

【課題】データ転送処理に関して、効率良くアクセスを行うかによって、システム全体の性能を上げる技術を提供する。

【解決手段】内蔵メモリ(2)と、マスタデバイス(6−1〜6−n、7)から渡されたデータをその内蔵メモリ(2)に転送するメモリコントローラ(3)とを具備するデータ処理装置(1)を構成する。ここで、その内蔵メモリ(2)は、第1データバス幅のデータに対応した第1内蔵メモリと、その第1内蔵メモリと独立に動作する第2内蔵メモリとを含むことが好ましい。そして、そのメモリコントローラ(3)は、そのマスタデバイス(6−1〜6−n、7)から供給されたデータのデータバス幅が、その第1データバス幅を超えるとき、その第1内蔵メモリとその第2内蔵メモリとをあわせて単一のメモリデバイスとして機能させる。

(もっと読む)

データ転送装置及び方法

【課題】DMAC連動で生じる可能性のある無駄なリクエストの発行を抑制する。

【解決手段】書き込みDMAC111と読み出しDMAC112は連動してメモリアクセスする。ライトリクエスト受信カウンタ1153は、書き込みDMAC111によるライトリクエストのデータ量(ライトリクエスト数)を計算し、読み出しDMAC112に通知する。好ましくは、同時にライトリクエストの受領通知(Ack通知)もともに通知する。サイズ比較部116がライトリクエストのデータ量と、受信したAck通知に基づくリクエストが成立したライトリクエストのデータ量とを比較。一致した場合に、リクエスト発行制御部118が読み出しDMAC112のメモリアクセスを実行する制御を行う。

(もっと読む)

データ転送制御装置及び画像処理装置

【課題】簡易的な設定を基に局所的なバス負荷を低減するためにデータ経路を調整し、システム全体のデータスループットを向上させること。

【解決手段】データバス及びデータのアクセスルートを複数備えるデータ処理システムにおいて、データ転送制御装置100は、データ転送開始前に、外部からデータ転送における設定値が設定記憶される制御レジスタ部103と、上記制御レジスタ部103に記憶された上記設定値に基づき、上記複数のデータバス300,400の何れかを使用する、データが通過する経路を、自律的に決定する比較部104と、を備える。

(もっと読む)

DMA転送制御装置

【課題】ユーザー空間で確保されたメインメモリ領域であって、物理アドレス空間においては離散的にマッピングされるメインメモリ領域に高速に取り溢しなくデータを転送する。

【解決手段】ユーザー空間でデータの転送先となるメモリ領域を確保した時点でその領域に対応する物理アドレスをカーネル空間で取得し、DMA転送制御装置300が具備するディスクリプタ格納メモリ304に予め総ページ数、各ページの先頭物理アドレス、各ページの転送サイズ情報をデータの転送に必要な転送情報として記録してからDMA転送を開始する。DMA転送制御装置300はページ単位の転送が完了したタイミングで残りページ数をデクリメントするとともに、次ページの転送情報をディスクリプタ格納メモリ304から取得できるので、CPUがページ単位の転送完了を認識する必要はなく、高速なデータ転送が可能となる。

(もっと読む)

同時中間プロキシ・ダイレクト・メモリ・アクセス

【課題】写真および動画の保存、共有は、ますます大きなストレージ・システムを求める需要を助長する。これらの増大する需要に対する、ディスクアレイの使用における構成要素間のデータ転送を効率化する。

【解決手段】DMAデータを周辺装置からハードウェア支援機能およびプロセッサRAM111に同時に転送する方法が開示される。第1のDMA転送が、データを周辺装置から周辺DMAエンジン120に転送するように構成される。データを受信している間に、DMAエンジン120は、このデータをプロセッサRAM111に同時に転送する。DMAエンジン120はまた、データのコピーをハードウェア支援機能に転送する。DMAエンジン120はまた、コピーをハードウェア支援機能に転送している間に、データをプロセッサRAM111から周辺装置に同時に転送する。

(もっと読む)

データ転送制御装置、データ転送制御方法、データ転送制御プログラム及び記録媒体

【課題】本発明は、データ転送を効率的に行うデータ転送制御装置、データ転送制御方法、データ転送制御プログラム及び記録媒体に関する。

【解決手段】画像処理装置1は、メインCPU3を介したデータ転送要求が、複数のDMAC20a〜50aからあると、内部アービタ70が、該データ転送要求に対して公平に所定転送期間だけデータ転送を許可するデータ転送の許可/不許可を制御するとともに、許可したデータ転送が該転送期間を経過すると、該DMAC20a〜50aからのデータ転送要求をマスク期間だけマスクするマスク処理を制御する際に、メインCPU3の内部バッファのデータ量をフローコントロール処理時間毎に取得して、取得した内部バッファのデータ量に基づいてメインCPU3によるデータ転送状況を判定し、該判定結果に基づいてマスク処理を制御する。

(もっと読む)

処理装置、画像形成装置及び処理方法

【課題】データ処理の処理速度を低下させることなく別のデータ処理を行うことができる処理装置、画像形成装置及び処理方法を提供する。

【解決手段】主DMA制御部22は、レジスタ部23、DMA起動部24などを備え、従DMA制御部25は、レジスタ部26、DMA起動部27などを備えている。主DMA制御部22は、主DMA転送及び主画像処理の制御を行う。また、従DMA制御部25は、従DMA転送及び従画像処理の制御を行う。マルチプレクサ28は、CPUからのセレクト信号SELがローレベル(Lo)の場合には、主DMA制御部22からの信号を画像処理部21へ出力し、セレクト信号SELがハイレベル(Hi)の場合には、従DMA制御部25からの信号を画像処理部21へ出力する。

(もっと読む)

オーディオ再生装置、およびオーディオ再生方法

【課題】停止要求から停止完了までの応答性が確保でき、更に停止時のノイズ発生も抑制できるオーディオ再生装置を提供することである。

【解決手段】本発明にかかるオーディオ再生装置は、第1のプロセッサ1と、圧縮された音声データをデコード処理する第2のプロセッサ2と、デコード後データを格納するメモリ3と、を有する。更に、メモリ3に格納されたデコード後データを転送すると共に、転送中のデコード後データのアドレスを格納する第1アドレスレジスタ8と、転送中に停止要求がされた際に、第1アドレスレジスタ8に格納されたデータアドレスから所定バイト先のデコード後データに対してフェードアウト処理を行い、フェードアウト処理を行ったデコード後データの終端アドレスを格納する第2アドレスレジスタ9とを備えるDMA転送部4を有する。

(もっと読む)

信号処理装置

【課題】一定時間毎にA/D変換器を起動して複数のアナログ信号をA/D変換する信号処理装置において、何れかのアナログ信号について、それのA/D変換データのA/D変換器からメモリへのDMA転送を、A/D変換器の起動間隔とは異なる任意の間隔で行えるようにする。

【解決手段】マイコン10にて、A/D変換器11からRAM17にデータを転送するDMAコントローラ16へは、A/D変換完了時毎に生じるDMA転送要求信号(TrgB)とは別のDMA転送要求信号(TrrC)が、タイマユニット25から与えられ、そのタイマユニット25は、CPU21により周期とパルス幅が設定されるPWM信号出力回路23からのPWM信号に特定方向のエッジが生じるとTrgCを出力する。更にDMAコントローラ16は、TrgB,Cの各々について、A/D変換器11のどのチャンネルのA/D変換データを転送対象とするかがCPU21により指定される。

(もっと読む)

データ転送装置及び半導体試験装置

【課題】システムコールのオーバーヘッドを削減するとともにDMAコントローラの待ち時間を削減して転送効率の悪化を防止することができるデータ転送装置等を提供する。

【解決手段】データ転送装置1は、ソフトウェアによってシステム制御部21及びデバイスドライバ部22が実現されるCPU11と、複数のテスタデバイス12a〜12nに設けられたDMAコントローラ31a〜31nとを備える。システム制御部21は、DMAコントローラ31a〜31nに対するDMA転送コマンドを一まとめにしたDMA転送コマンド群を出力する。デバイスドライバ部22は、システム制御部21からのDMA転送コマンド群をデバイスノード24で受信し、受信したDMA転送コマンド群に基づいてテスタデバイス12a〜12nの各々で行われるデータ転送の予測転送終了時間を求めてテスタデバイス12a〜12nの各々で行われるデータ転送の転送開始順序を制御する。

(もっと読む)

マルチプロセッサシステム及びそれを搭載した流体吐出装置

【課題】第1制御部と第2制御部とによるコヒーレンシをより容易且つ確実に実現する。

【解決手段】マルチプロセッサシステム30は、リクエストの出力先としてDMAコントローラ35が予め対応付けられているDMAメッセージボックス37を備えており、このDMAメッセージボックス37へのリクエストをメインプロセッサ31からブリッジ32が入力すると、メモリ34に対する先のリクエストのAck信号を入力したあとリクエストをDMAメッセージボックス37へ出力し、このリクエストをDMAメッセージボックス37が対応付けられたDMAコントローラ35へ出力する。このように、複数あるプロセッサのうち、DMAコントローラ35へのリクエストは、先のリクエスト、例えばメモリ34へのデータの書込などが完了した回答を得たあとに出力される。

(もっと読む)

バス調停装置

【課題】共通バス方式を使用する場合において、低コストを実現するだけでなく、効率よくバスを使用して高パフォーマンスを実現できるバス調停装置を提供する。

【解決手段】DMAデータ転送を制御するDMA制御手段によるDMAアクセスと、CPUによるCPUアクセスとの両方に共通で使用される共通バスと接続され、共通バスにおけるDMAアクセスとCPUアクセスとの間のバス調停を行うバス調停装置であって、CPUの処理量に応じて、DMAアクセスとCPUアクセスとの間のバス調停の割合を変更する。

(もっと読む)

データ転送制御装置、データ転送制御システム、データ転送制御プログラム、ドライブレコーダ、及びデータ転送制御方法

【課題】セクタへのデータ転送の完了を確認する作業により、CPUの負荷が重かった。

【解決手段】各データが1回で転送可能な単位データである複数のデータを第1の装置から第2の装置へ転送するのに必要な、前記第1の装置及び前記第2の装置の少なくとも一の装置の動作を規定する動作規定情報の通知をCPUから受ける被通知部と、前記動作規定情報に基づき、前記複数のデータを、前記第1の装置から前記第2の装置へ転送する転送部と、前記転送が終了したとき、当該終了の旨を前記CPUへ通知する通知部と、を含む。

(もっと読む)

データ転送装置、データ出力装置、データ処理装置、データ転送システム、ドライブレコーダ、電子機器、データ転送プログラム、及び、データ転送方法

【課題】データを2つのメモリに転送しようとするとき、2回の転送を行わなければならなかった。

【解決手段】転送元装置からデータの転送を受けるべき第1の転送先装置及び第2の転送先装置の両アドレスが割り当てられているアドレスを指定することにより前記第1の転送先装置及び前記第2の転送先装置の両装置を選択する選択部と、前記転送元装置から前記データを前記選択された前記第1の転送先装置及び前記第2の転送先装置の両装置へ実質的に同時に転送する転送部と、を含む。

(もっと読む)

データ転送システム、DMAコントローラ、ドライブレコーダ、データ転送方法、データ転送プログラム、電子機器装置

【課題】第2の装置DV2に障害(例えば、ハードディスクのトラブル)が発生すると、第2のデータDT2を第1の装置DV1から第2の装置DV2に転送しようとしても、転送することが不可能になるという問題があった。

【解決手段】第1の装置DV1と、第2の装置DV2と、メモリMと、転送部10と、第2の装置DV2に障害が発生したか否かを検出する障害発生検出部20と、を有するDMAコントローラ2と、第1の装置DV1から第2の装置DV2へ第1のデータDT1、第2のデータDT2を転送すべき旨をDMAコントローラ2に指示するCPU1と、を備え、CPU1からの指示に応えて転送部10が第1のデータDT1を第1の装置DV1から第2の装置DV2へ転送した後に、障害発生検出部20が障害を検出したとき、転送部10は、第2のデータDT2を第2の装置DV2に代えてメモリMに転送する。

(もっと読む)

21 - 40 / 165

[ Back to top ]