Fターム[5B061RR07]の内容

Fターム[5B061RR07]に分類される特許

1 - 20 / 21

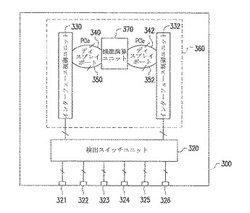

複数のデータ接続ポートを備えた電気装置

【課題】複数のデータ接続ポートを備えた電気装置を提供する。

【解決手段】電気装置は、本体、処理ユニット、及び検出スイッチユニットを備える。本体には、M個の面と面上に配置されるN個のデータ接続ポートを備える。処理ユニットは、第1のインターフェース制御ユニットと第2のインターフェース制御ユニットを備える。検出スイッチユニットは、データ接続ポートが接続されているかどうかを検出する。 i番目とj番目のデータ接続ポートの接続を検出しているとき、検出スイッチユニットはi番目とj番目のデータ接続ポートをそれぞれ第1のインターフェース制御ユニットと第2のインターフェース制御ユニットによって制御されるように割り当て、i番目とj番目のデータ接続ポート以外のデータ接続ポートを無効にする。したがって、電気装置はデータ接続ポートの柔軟性の形式により他の電気装置に接続することができる。

(もっと読む)

インターフェース装置

【課題】 コストを抑えて、接続される装置を制御することが可能なインターフェース装置を提供することを目的とする。

【解決手段】 本発明のインターフェース装置10は、第1の装置と接続される第1のインターフェースと、第2の装置と接続される第2のインターフェースと、データを記憶する記憶手段と、を備え、記憶手段30に記憶されたファイルシステムによりデータをファイルとして扱うインターフェース装置であって、第1の装置により第1のインターフェースを介して記憶手段30へ書き込まれた所定のファイルの内容に基づいて、第2のインターフェースを介して第2の装置を制御する制御手段32を備えることを特徴とする。

(もっと読む)

デバイス機器

【課題】2種類の規格の系統で同時に接続可能に構成され、一方の系統が優先的に使用されるインタフェースの利用性を向上させる。

【解決手段】ホスト機器と接続可能なデバイス機器は、第1の規格によって規定された第1の接続部と、該第1の規格と異なる第2の規格に準拠して該第1の接続部と独立して設けられた第2の接続部とを備え、該第1の接続部と該第2の接続部とを前記ホスト機器の対応するインタフェースに同時に接続可能なインタフェース部を備える。また、デバイス機器は、第1の接続部に接続され、デバイス機器の少なくとも一部の機能を制御する制御部と、第2の接続部に接続され、第2の規格に準拠したデバイス機器と接続可能な第3の接続部とを備える。

(もっと読む)

プロセッサーシステム

【課題】各デバイス間の通信を効率よく中継する。

【解決手段】マスターデバイス40とそれに対するスレーブデバイスとしての第1のスレーブデバイス50とを接続してデバイス間の通信を中継するクロスバースイッチ45と、マスターデバイス40および第1のスレーブデバイス50に対するスレーブデバイスとしての第2のスレーブデバイス60と第1のスレーブデバイス50とを接続してデバイス間の通信を中継する多段ブリッジ55とを備えて、クロスバースイッチ45と多段ブリッジ55との接続を介してマスターデバイス40と第2のスレーブデバイス60とを接続してデバイス間の通信を中継するから(経路(3))、各デバイス間の通信において通信対象となるデバイス以外のデバイスを経由する必要がなく、各デバイス間の通信を効率よく中継することができる。

(もっと読む)

データ転送デバイス

本発明は、プラットフォーム上のデータを転送するための、特に、プラットフォームの異なるコンポーネント間で同時にデータを転送するためのデータ転送デバイス(10)に関する。少なくとも一つがインプットポート(13、14、15)であり少なくとも一つがアウトプットポート(16、17、18)である少なくとも三つのポート間でデータを同時に転送するように調整されたデータ転送デバイスが、示される。データ転送デバイス(10)は、インプットポート(13、14、15)とアウトプットポート(16、17、18)との間でデータを転送する命令を実行する少なくとも二つのコントローラ(20、21)を含む。コントローラ(20、21)は、コントローラ(20、21)間で同期するための同期命令、及び/又はインプットポート(13、14、15)とアウトプットポート(16、17、18)を同期させるための同期命令を受信するよう調整されている。  (もっと読む)

(もっと読む)

スイッチ、スイッチの制御方法及びスイッチシステムの制御方法

【課題】本発明の課題は、バス階層を増加させることなく、システムを増大させることである。

【解決手段】上記課題を解決するために、第1ブリッジに備えられた第1ステートマシンは、第1ポートからパケットを受信した時、テーブルを参照して当該パケット内のアドレスに対応する入出力装置または他のスイッチに当該パケットを転送し、第2ブリッジに備えられた第2ステートマシンは、当該第1ブリッジから転送されたパケット内のアドレスと、第2レジスタに格納されたアドレスとを参照して、当該パケットを第2ポートを介して当該入出力装置に転送し、第3ブリッジに備えられた第3ステートマシンは、第1ブリッジから転送されたパケットを第3ポートを介して当該他のスイッチに転送する。

(もっと読む)

マルチコアシステム

【課題】全体的なレイテンシを小さくし、かつシステム全体のメモリコストを削減することのできるマルチコアシステムを得る。

【解決手段】入力バッファ部5−1〜5−mは、各バスマスタ2−1〜2−mからの転送データを蓄積する。グリッドキューメモリ6は、バスマスタ2−1〜2−mの個数とバススレーブ3−1〜3−nの個数を乗じた数だけ転送データを格納可能で、これら格納した転送データを同時に出力することが可能に構成されている。グリッドキューメモリ6からの転送データは、クロスバ8によって調停され、バススレーブ3−1〜3−nに対応して設けられた出力バッファ部9−1〜9−nに出力される。

(もっと読む)

イニシエータの通知方法および装置

本発明の一実施形態において、メモリシステムは、少なくとも1つのイニシエータと、SATAデバイスと、改善されたブリッジデバイスとを含むことが開示される。該改善されたブリッジデバイスは、該少なくとも1つのイニシエータと該SATAデバイスとの間の通信を容易にするように構成され、そして少なくとも1つの入力ポートを有し、該(1つ以上の)入力ポートを介して該イニシエータからの情報を受信するように動作可能である。該改善されたブリッジデバイスは、通知イベントの間に、通知が該少なくとも1つのイニシエータに送信される通知イベントを処理し、そしてイベントに基づいて動作を実行し、それによって、イニシエータとSATAデバイスとの間の通信の容易さを促進する。  (もっと読む)

(もっと読む)

コンピュータ装置及びそのデータ転送方法

【課題】 リクエストが圧縮された演算器の数や圧縮のパターン数が多い場合でも圧縮情報のビット数を小さくすることが可能なデータ転送方法を提供する。

【解決手段】 番号が連続する複数の演算器からのメモリリクエストが一のメモリポートに競合する場合には、これら複数のメモリリクエストを1つに圧縮する。この際、演算器番号情報とメモリアドレス特定用情報とを含む圧縮情報を生成する。演算器番号情報は、圧縮される複数のメモリリクエストの発行元である複数の演算器のうち特定の演算器の番号を示す情報である。メモリアドレス特定用情報は、前記一のメモリポートに含まれるメモリアドレスのうち何れのメモリアドレスに対するリクエストを圧縮したのかを示す情報である。リプライが前記一のメモリポートから戻ってくると、該リプライを圧縮情報に基づいてリクエスト発行元の演算器に分配する。

(もっと読む)

ブリッジ、情報処理装置およびアクセス制御方法

【課題】周辺デバイスからプロセッサのメモリへのアクセスにおいて、効率向上を図る。

【解決手段】プロセッサユニットと周辺デバイスを接続するブリッジ20の下流ポート22は、周辺デバイスとの間に提供されるバーチャルチャネルであって、周辺デバイスがそのいずれかを利用してプロセッサユニットのメモリにアクセスするための複数の下流チャネルのいずれかを介して、周辺デバイスからのアクセスを受け付ける。中継部24は、このアクセスを、プロセッサユニットによりサポートされる複数のバーチャルチャネルであって、各チャネルについてメモリへアクセスする際に使用可能なメモリ帯域がそれぞれ割り当てられた上流チャネルへ中継する。その際、下流チャネルの識別子と上流チャネルの識別子とを対応付けて記憶したテーブルを参照して、周辺デバイスからのアクセスに応じて、該周辺デバイスが用いる下流チャネルに対応する上流チャネルを割り当てる。

(もっと読む)

クロスバースイッチ、情報処理装置および転送方法

【課題】スループットを低下させることなく高周波動作が可能なクロスバースイッチを提供する。

【解決手段】ポート入力部200は、ノード100からの2つのフリットを第1のレジスタ014と第2のレジスタ300とに格納し、2つの調停要求信号を生成する。また、いずれかの要求先への第1の調停要求信号があるか否かを通知するための第1の通知信号335を生成する。レジスタ322、323を備えた調停部は、複数のポート入力部からの2つの調停要求信号および第1の通知信号335と、第2の通知信号405〜406とに基づき調停回路320にて調停を行う。ポート入力部200は、調停結果信号に従って第1のレジスタ301からフリットを出力する。ポート出力部210は、調停結果信号に従って、いずれかのポート入力部の第1のレジスタ301から出力されたフリットをノード100に順次出力する。

(もっと読む)

結合システムおよび方法

【課題】複数のバス間での情報転送のために改善されたシステムを提供する。

【解決手段】ホストコンピュータによりアクセスできるブリッジであって、第一バス10から第二バス12にアクセスを拡張できる。結合システムは、第一と第二のインターフェイスとともにリンク40,46をもつ。第一インターフェイス14は第一バスとリンクとの間に結合される。第二インターフェイス16は第二バスとリンクとの間に結合される。第一インターフェイスと第二インターフェイスは、次のように動作する。(a)第一バスと第二バスフォーマットと異なるフォーマットのリンクを介して情報をシリアルに出力する、(b)第一バスを介して通信するポータブルコンピュータは、該第一バスの装置にアクセスするのに使用されたのと実質的に同じアドレス処理するタイプの一つもしくは二つの該第二バスのバスコンパチブル装置を独立にアドレスすることを可能にする。

(もっと読む)

データ転送システム、データ転送方法およびクロスバLSI

【課題】 リンク調整に起因するデータ転送効率の低下を抑制することができるデータ転送システムを提供する。

【解決手段】 タイマカウンタ52の値が”0”になった場合には、リンク調整検出回路54は、そのことを検出して、リンク調整中フラグレジスタ55に”1”をセットする。すなわち、リンク調整を指示する。リンク切断判定回路62は、エラー発生数に応じてタイマ設定値選択回路50が扱うタイマ設定値を調整するための信号を生成して、タイマ設定値選択回路50に出力する。以後、タイマ設定値選択回路50は、リンク切断判定回路62が出力した信号が示すタイマ設定値を選択する。

(もっと読む)

情報処理装置

【課題】例えばPCI Express等におけるポートアービトレーション制御の設定を使用目的等に応じて任意に行うことを可能とした情報処理装置を提供する。

【解決手段】システムコントローラ13のポートアービトレーション100は、複数のポート101に接続されたPCI Expressデバイスのデータ転送をレジスタ102の内容に応じて調停する。BIOS−ROM18には、各PCI Expressデバイス毎にそのデバイスを優先すべくレジスタ102を設定するためのポートアービトレーションテーブル群が格納されており、このBIOS−ROM18に格納されてCPU11により実行されるシステムBIOSは、ユーザの選択に基づき、複数のポートアービトレーションテーブル群からいずれかのポートアービトレーションテーブルを選択し、ユーザが選択したPCI Expressデバイスが優先されるようにレジスタ102の設定を行う。

(もっと読む)

デバイス

【課題】 データ転送の効率が高められるとともにデータ転送の時間の短縮化が図られたデバイスを提供する。

【解決手段】 リング接続型バス20で接続されたマスタ1_1,1_2,1_3,1_4およびスレーブ2_1,2_2,2_3,2_4と、それらマスタ1_1,1_2,1_3,1_4およびスレーブ2_1,2_2,2_3,2_4にダイレクトバス30で接続されたマスタポート1_1a,1_2a,1_3a,1_4a,スレーブ2_1,2_2,2_3,2_4を有する制御部10を備えた。

(もっと読む)

バス転送装置

【課題】1または複数のNICポートによって送受信されるパケットを、PCIバス上で高速にかつ効率よくDMA転送を行なうバス転送装置を得ること。

【解決手段】DMAフレーマ112が、パケットバッファ113に一時保持されたパケットにこのパケットを扱うNICポート120〜12nを識別するためのデータ長を含むフレーム情報を付加したDMAフレームをDMA転送するとともに、PCIバス104を介してDMA転送されたNICポート120〜12nへのパケットを含むDMAフレームからパケットを抽出してNICポート120〜12nに送信し、DMA転送が終了した際に、割り込み要因提示装置114が、PCIバスインタフェース111がアサートにした割り込み信号の割り込み要因を提示する。

(もっと読む)

オンチップバスシステム

【課題】 少ないFIFOの構成でスループットの低下を防ぐことを可能としたオンチップバスシステムを提供する。

【解決手段】 第1のスレーブデバイス12Aから出力されるリードデータを保持する第1のFIFO141Aがフル状態となったとき、第2のスレーブデバイス12Bから出力されるリードデータを保持する第2のFIFO141Bの空き状況を確認して、フル状態でなければ該第2のFIFO141Bにリードデータを書き込み、第1のFIFO141Aを迂回するように制御回路142Aが制御する。

(もっと読む)

転送制御装置、転送制御システム及び信号処理装置

【課題】 複数の出力装置から入力される信号に対応する応答信号を、適切な順序で適切な出力装置へ返信することが可能な転送制御装置、該転送制御装置を利用した転送制御システム及び前記転送制御装置を備えた信号処理装置を提供する。

【解決手段】 命令入出力部11,12から命令信号が入力された場合、命令制御部14は命令信号に命令番号を割り当て、割り当てた命令番号をこの命令信号が入力された命令入出力部11,12に対応させて命令番号格納部15に記憶させ、命令信号と命令番号とを応答入出力部13から出力する。応答入出力部13から応答信号が入力された場合、応答制御部16は応答信号を命令番号に対応させて応答格納部17に記憶させ、命令番号格納部15の命令番号欄の1番目の命令番号に対応する応答信号が応答格納部17に格納された場合、この応答信号を対応する命令入出力部11,12を介してPC21,22へ送信する。

(もっと読む)

インタフェース回路生成装置およびインタフェース回路

【課題】デッドロックを回避でき、各種の優先順位方式による調停を実現できるインタフェース回路を容易に設計すること。

【解決手段】複数のバスとの間のインタフェース回路であるハブ1についての論理表現を作成するインタフェース回路生成装置において、複数のバスの各々に対応したポートをグループとして定義する定義ファイルを備えており、定義ファイルを用い、一のバスに対応したグループから他のバスに対応したグループへのアクセスが同時に発生した場合に優先順位の低いグループのアクセス要求についてはリトライを返信する回路の論理表現を作成するものである。

(もっと読む)

クロスバ

【課題】スループットを向上させることを課題とする。

【解決手段】クロスバ100は、入力ポートA、入力ポートB、入力ポートCおよび入力ポートDそれぞれに、データ転送先が「宛先W」および「宛先Y」であるデータパケットをキューイングする入力キューおよびデータ転送先が「宛先X」および「宛先Z」であるデータパケットをキューイングする入力キューを多段に配設した入力キュー群と、入力ポートに入力されたデータパケットのデータ転送先(すなわち、「宛先W」および「宛先Y」、或いは「宛先X」および「宛先Z」)に応じて当該データパケットを入力キュー群に振り分ける振分処理部110とを備える。

(もっと読む)

1 - 20 / 21

[ Back to top ]