Fターム[5B062EE02]の内容

マイクロコンピュータ (2,258) | チップ外部との入出力 (243) | 出力回路 (25)

Fターム[5B062EE02]に分類される特許

1 - 20 / 25

IC出力ポート切換制御装置

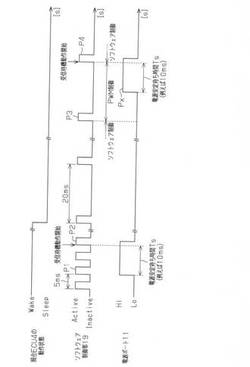

【課題】電源を省電力化することができるIC出力ポート制御装置を提供する。

【解決手段】ワイヤレスキーシステムの照合ECU4は、自身のメモリに記憶されたプログラムにて所定周期で動作するソフトウェア制御部19と、自身に元から備わるPWMリソースとを有する。照合ECU4のスリープ中、車両受信機が受信待機動作をとるパルスP4の1周期前のパルスP3で電源ポート11をソフトウェア制御からPWM制御に変更することにより、電源ポート11をPWM制御に切り換える。このため、PWM制御のパルスPxがHiレベルに立ち上がってからの時間が電源安定待ち時間Tsとして車両受信機に供給される。

(もっと読む)

半導体集積装置

【課題】SiPのチップ間を接続するための端子数が増加する。

【解決手段】パッケージ内部に第1の半導体チップと第2の半導体チップが集積される半導体集積回路であって、前記第1の半導体チップは、第1の通信部と、複数のアナログ回路とを備え、前記第2の半導体チップは、第2の通信部と、前記複数のアナログ回路の特性調整用データを格納するメモリ部とを備え、前記第1の通信部と前記第2の通信部とがシリアルデータ通信線で接続され、前記シリアルデータ線を経由して前記第1の半導体チップが備える複数のアナログ回路の特性調整用データをそれぞれ複数のアナログ回路に転送する半導体集積回路。

(もっと読む)

マイクロコンピュータ

【課題】CPUが、例え、低消費電力モード中に外来ノイズの影響を受けたとしても外部信号端子はハイインピーダンス状態となっているので、その端子によって外部デバイスが駆動されることはなく、信頼性を向上する。

【解決手段】端子制御手段は、CPUが低消費電力モードに移行する場合に出力するコマンドに応じて、外部信号端子42に接続される出力バッファ43Aをハイインピーダンス状態に設定するための信号を出力する。そして、前記出力信号は、前記CPUが動作している期間に前記外部信号端子42を制御するために出力されるポート制御信号と共に、論理ゲート41を介して前記出力バッファ43Aに与えられる。

(もっと読む)

集積回路における修復可能IO

半導体集積回路装置

【課題】外部のデバイスに接続される回路とLSI内部の回路との間におけるタイミング設計を不要とすること。

【解決手段】半導体集積回路装置は、外部デバイスに対して接続されるインタフェース回路であって第1のクロック信号が供給される第1の回路と、第1のクロック信号を分周した第2のクロック信号が供給される第2の回路と、第2のクロック信号を第1のクロック信号に基いて遅延させた送受信タイミング信号を生成するタイミング生成回路と、第2の回路から受信した信号を第1のクロック信号に同期してサンプリングする複数段のシフトレジスタと該複数段のシフトレジスタに対する入出力信号に含まれるハイレベルの信号とロウレベルの信号の多数決を送受信タイミング信号に同期して行うとともに多数決により決定された信号を第1の回路に出力する多数決回路とを有する第1の位相調整回路とを備えている。

(もっと読む)

マイクロコンピュータ

【課題】スタンバイモード時であってもIO出力を保持することができ、かつIOバッファのレイアウト、および電源/信号配線について制約の少ないマイクロコンピュータを提供すること

【解決手段】常時ON電源領域と電源遮断可能領域の周囲に、IO電源系で動作するIOバッファと、IOバッファの夫々を分離するカットセルと、を配置する。常時ON電源領域から出力されるIO出力保持を指示する信号をIOバッファとカットセルを周回させる。カットセルにはIO電源系で動作するレベルシフタを備え、IOバッファの電源系に合わせてIO出力保持を指示する信号をレベルシフトしてIOバッファに供給する。

(もっと読む)

マイクロコントローラ

【課題】従来の出力回路において、出力バッファの貫通電流に起因するノイズを低減するための遅延回路を出力回路に挿入しているので、出力回路の数が増加するほど回路面積が増加するという課題がある。

【解決手段】制御部2は、CPU1からの書き込み要求Qを受け付けて出力回路5に対するイネーブル信号Siを生成するとともに書き込みデータDwを一時的に保持し出力回路5へ転送する機能を有し、出力回路5は、複数の1ビット出力部51〜54をもち、個々の1ビット出力部は、制御部2から送られてくる書き込みデータDwをイネーブル信号Siのタイミングで書き込むためのレジスタRとレジスタのデータを外部へ出力するための出力バッファBとを備え、さらに、複数の1ビット出力部51〜54におけるデータ書き込みの実効的なタイミングをずらす機能を制御部2またはCPU1に持たせた構成としている。

(もっと読む)

半導体集積回路

【課題】従来の半導体集積回路は、電源ノイズが発生するためデータの送信を精度良く行うことができないという問題があった。

【解決手段】本発明にかかる半導体集積回路は、SoC回路100と、SoC回路100から送信されたデータを受信するSDRAM回路101と、を備え、SoC回路100は、送信データを出力するか、出力をハイインピーダンス状態にするか、が切り替わるデータ出力回路203と、データ出力回路203において、データ送信時には送信データを出力し、データ送信後にさらに別のデータを送信する場合には、先のデータ送信後から所定の期間、先のデータ送信時に最後に出力した送信データを出力し続けるように、データ出力回路203に対して制御信号230を出力する制御回路205と、を備える。このような回路構成により、データの送信を精度良く行うことができる。

(もっと読む)

マイクロコンピュータ及びマイクロコンピュータシステム

【課題】CPUのクロックが停止しているスリープモードにおいて出力端子のレベルを変える機能を有するマイクロコンピュータにおいて、出力端子のレベルを変えるまでの時間と出力端子のレベルを変えてからスリープモードを解除するまでの時間を自在に設定できるようにする。

【解決手段】CPUと、CPUのスリープモードの設定と解除を制御するスタンバイ制御部と、出力端子と、第1のタイマと、前記CPUがスリープモードのときに第1のタイマがあらかじめ定められた計時を行うと、スリープモードを保ったまま、出力端子のレベルを変える出力端子制御部と、スリープモードにおいて出力端子制御部が出力端子のレベルを変えるときに計時を開始する第2のタイマと、を備え、スタンバイ制御部は、第2のタイマが所定の計時を行うとCPUのスリープモードを解除する。

(もっと読む)

集積回路装置及び電子機器

【課題】I/Oセルを効率良く配置できる集積回路装置及び電子機器等を提供すること。

【解決手段】集積回路装置は、各I/OセルがI/O回路及びパッドで構成される複数のI/Oセルと、コア回路102とを含み、チップ外縁部101からコア回路102へ向かう方向を第1の方向とした場合に、複数のI/Oセルのうちの第1のI/Oセル10の第1のI/O回路11及び複数のI/Oセルのうちの第2のI/Oセル20の第2のI/O回路21は、第1の方向に沿って並んで配置され、第1の方向に直交する方向を第2の方向とした場合に、第1のI/Oセル10の第1のパッド12は、第1のI/O回路11の第2の方向に配置される。

(もっと読む)

表示部の制御装置

【課題】車両に搭載するマイクロコンピュータを備える表示部の制御装置を提案する。

【解決手段】異なる仕様ごとに固有の特性データを記憶しており、入力端子42〜46と出力端子61〜63を有するマイクロコンピュータ21と、入力端子42〜46に接続される仕様設定用制御回路41と、車両のインストルメントパネルに配設される操作スイッチ11〜16と、操作スイッチ11〜16の操作に応じて駆動状態が変更される被操作部材と、被操作部材の駆動状態を表示する表示部17〜19と、出力端子61〜63に接続される表示部用駆動回路31とを備え、マイクロコンピュータ21は、仕様設定用制御回路41からの入力信号に応じて特性データが設定され、設定された特性データに応じた信号を表示部用駆動回路31へ出力することにより、表示部17〜19の表示が切換わる。

(もっと読む)

マイクロコンピュータ

【課題】PWMパルス生成の信頼性の向上を図る。

【解決手段】CPU(16)とPWMタイマ(25)とを設ける。上記PWMタイマは、上記PWMパルスのデューティ値パターンをセット可能なRAMと(251)、PWMパルスの生成を可能とするPWMコントローラ(254,255)とを含む。上記PWMコントローラは、PWMカウンタを含み、上記PWMパルスの単位波形は、上記RAM内のデューティ値と上記PWMカウンタの出力値とのコンペアマッチにより生成され、上記コンペアマッチ毎に次のデューティ値が上記CPUの介在無しに上記RAMからロードされることで、上記PWMパルスのデューティ値の時系列変化が可能にされる。それによりPWMパルスの生成においてCPUのバストラフィックの混雑の影響を避け、CPUからの書込みの一時的なトラップの発生を回避する。

(もっと読む)

受領信号の形成装置

【課題】従来技術の欠点を低減するために受領信号を形成する装置および方法を提供することである。

【解決手段】受領信号の形成装置であって、プロセッサは、プロセッサクロック信号によりクロッキングされ、中断命令に基づいて静止状態からウェークアップされ、動作状態において前記中断命令を処理し、該中断命令の処理後または該中断命令の処理中に、プロセッサクロック信号に同期する受領信号を形成し、少なくとも1つの周辺機器は、前記プロセッサクロック信号には非同期で経過する周辺機器クロック信号によりクロッキングされ、前記中断命令を周辺機器クロック信号に同期して前記プロセッサに送信し、第1の論理回路は、プロセッサクロック信号に同期する受領信号から周辺機器クロック信号に同期する受領信号を形成し、該同期する受領信号により周辺機器に対して、中断命令が処理されたことが通知される、ことを特徴とする。

(もっと読む)

出力ポート、マイクロコンピュータ、及びデータ出力方法

【課題】割り込み処理の影響を受けずに、出力データをビット単位に切り替え可能なポート回路、マイクロコンピュータ、及びデータの出力方法を提供することにある。

【解決手段】本発明による出力ポート回路3は、複数の出力バッファ24への出力データを保持する複数の第1保持回路22と、複数の第1保持回路22へ出力すべきデータを保持する複数の第2保持回路20と、複数の第2保持回路20の出力データが複数の第1保持回路22に取り込まれるか否かを個別に設定するビットパタンデータを保持する複数の第3保持回路21とを具備する。複数の第2保持回路20へのデータ入力と複数の第3保持回路21へのデータ入力とは同一タイミングで制御される。

(もっと読む)

動作モード制御回路、及びマイクロコンピュータ

【課題】制御プログラムにより処理を行うマイクロコンピュータが複数の動作モードを有する入出力回路を内蔵する場合に、動作モードの意図しない再設定を抑止する。

【解決手段】少なくとも、制御信号発生部と、制御信号発生部からの第1の出力信号に応答して制御信号発生部からの第2の出力信号を保持し、保持した信号の論理値に応じた書込信号を発生する書込抑止回路と、書込信号に応答して制御信号発生部からの第3の出力信号を保持し、保持した信号の論理値に応じた制御信号を発生する制御回路とを備え、制御信号発生部からの第2の出力信号の論理値に応じた書込信号は、一方は論理値が固定した信号であり、他方は制御信号発生部からの第1の出力信号のバッファ信号であって、制御信号は、少なくともデータレジスタ回路を含む複数の信号発生回路の中から、外部へ信号を伝える信号発生回路を選択する選択回路へ供給されるようにする。

(もっと読む)

処理回路装置、プロセッサ及びプロセッサの処理方法

【課題】ECなどのプロセッサのポートピンを効率的に利用することができる処理回路装置、この処理回路装置に含まれるプロセッサ、及び処理方法を提供すること。

【解決手段】プレゼンス信号線2と、LED8の点灯制御線3とが共用線1により並列的に接続され、EC5は、共用ポート11及び共用線1を介して、プレゼンス信号を取得する。また、ECは、共用ポート11及び共用線1を介して、点灯制御線3にLED8の制御信号である第1の制御信号を出力することができる。これにより、ポートピンの枯渇を解消し、ポートピンを効率的に利用することができる。

(もっと読む)

マイクロコンピュータ

【課題】本発明は、自己の動作を確実に自己検証できるマイクロコンピュータチップを得ることを目的とする。

【解決手段】本発明によるマイクロコンピュータは、チップ(1)外部との信号授受のための複数のパッド(8、15、19)と、同一のパッド(8、15)に接続された出力バッファ(7、14)および入力バッファ(9、16)と、入力バッファ(9、16)の後段に設けられ、対応する出力バッファ(7、14)から出力される信号を入力バッファ(9、16)を介して受ける第1のラッチ(11、18)とを備え、第1のラッチ(11、18)は、複数のパッド(8、15、19)のうちの一のパッド(19)を介して外部より付与される書き込み信号に応答して、入力バッファ(9、16)を介して受ける信号をラッチし、第1のラッチ(11、18)にラッチされた信号を検証する検証機能を装備されたCPU(3)をさらに備える。

(もっと読む)

命令の追跡中に作られるデータ・ストリームの大きさの削減

【課題】データ処理装置が高速になるに従って命令の実行の追跡が複雑になることに対処して、追跡中に作られるデータ・ストリームの大きさを削減する方法を開示する。

【解決手段】追跡論理(40)は命令ストリーム内の命令の処理を検出する監視論理(42)を含み、命令ストリーム内の命令のどれが条件付き直接分岐命令か、条件付き間接分岐命令か、無条件間接分岐命令かを検出する。追跡論理(40)は更に圧縮論理(50)を含み、前記条件付き直接分岐命令、条件付き間接分岐命令、または間接分岐命令をマーカ命令に指定し、マーカ命令毎に、マーカ命令を実行したことを示す実行標識またはマーカ命令を実行しなかったことを示す不実行標識は出力し、処理したがマーカ命令でない命令に関するデータは出力しない。

(もっと読む)

半導体集積回路

【課題】早急なパルス出力の要求があった場合でも、パルス出力を精度よく行う。

【解決手段】マイクロコンピュータ(1)は、タイマ(2)と、タイマを制御するCPU(3)とを備える。タイマは、カウンタ(10)、コンペアレジスタ(11)、強制コンペアマッチ制御回路(12)、比較回路(13)及び出力制御回路(14)を有する。カウンタは、クロック信号をカウントする。コンペアレジスタは、CPUがアクセス可能であって、所定の設定値を保持する。比較回路は、カウンタのカウンタ値とレジスタの設定値とを比較する。強制コンペアマッチ制御回路は、CPUにより、強制コンペアマッチ要求フラグFGがセットされると、カウンタのカウンタ値をコンペアレジスタにロードすると共に、比較回路からタイマ出力信号をエッジ変化させるための一致信号(17)を出力させる。出力制御回路は、一致信号に応じてタイマ出力信号(20)をエッジ変化させる。

(もっと読む)

マイクロコンピュータ素子

【課題】外部から目視によるマイクロコンピュータ素子の動作確認を容易にする

こと。

【解決手段】データの読出しのみ可能なROM12、データの読出し及び書込の

可能なRAM13、演算を行うCPU11が形成されたマイクロコンピュータチ

ップ1をパッケージングしたマイクロコンピュータ素子において、パッケージン

グの外部に光を出力する発光素子32と、CPU11が動作中であることを検出

する検出手段と、検出手段によりCPUが動作中であるとことが検出された場合

には、発光素子から光を出力する発光素子制御手段とを設けた。これによりマイ

クロコンピュータ素子の外部からCPUが動作中か否かを容易に検出することが

できる。

(もっと読む)

1 - 20 / 25

[ Back to top ]