Fターム[5B079BC07]の内容

Fターム[5B079BC07]に分類される特許

1 - 20 / 60

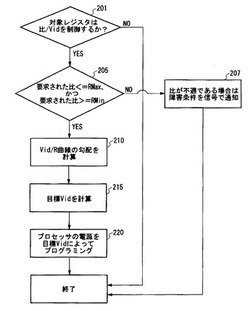

プロセッサ動作電圧の自動動的制御

【課題】プロセッサシステムは、動作電圧とコア/バス周波数との組み合わせによってはプロセッサの損傷あるいはプロセッサの動作の信頼性低下を引き起こすことを防止する。

【解決手段】1つのプロセッサの動作電圧を動的に調整する一方で、前記プロセッサが前記プロセッサの前記コア/バス周波数比との関係において有害である1つの動作電圧状態に1人のユーザによって置かれることを防止するための手法。より具体的には、プロセッサの動作電圧をプロセッサのバスおよび/あるいはコアクロック周波数の1つの関数として制御するための1つの手法に関する。

(もっと読む)

データ処理装置

【課題】処理するデータに応じた周波数のクロックを、CPUなどの処理制御部に与えることが可能な技術を開示する。

【解決手段】プリンタ1は、ネットワークを介してデータを受信するデータ通信部と、前記データ通信部が受信したデータを格納する受信バッファ41と、クロックジェネレータ23と、システム制御部22と、そのシステム制御部22が指定した指定クロックに基づき、受信バッファ41に格納されたデータに関する処理を制御するサブCPU21と、受信バッファ41に格納されているデータ量を検知するMAC25と、を備え、システム制御部22は、検知されたデータ量が多いほど、少ない場合に比べて、周波数が高いクロックを指定する。

(もっと読む)

クロック発生装置及びクロック信号生成方法

【課題】CPUに供給するクロック信号の周波数に関わらず、周辺回路に所定の周波数のクロック信号を供給することができるクロック信号生成回路及びクロック信号生成方法を提供する。

【解決手段】本発明にかかるクロック信号生成回路は、CPUに入力される第1クロック信号から、周辺回路に入力される所定の周波数を有する第2クロック信号を生成する。外部から入力される逓倍比及び分周比のうち少なくとも1に基づき、発振子が出力するクロック信号から入力される第1クロック信号を生成する第1クロック生成部と、第1クロック信号から第2クロックを作成するための基準値を算出する基準値算出部と、第1クロック信号のカウント値と基準値との比較結果に基づき、第2クロックを生成する第2クロック生成部とを有し、基準値算出部は、逓倍比及び分周比のうち少なくとも1つが変更され第1のクロック信号の周波数が変更されると、基準値を再度算出する。

(もっと読む)

中央処理ユニットをリアルタイムで監視するシステムおよび方法

1つまたは複数の中央処理ユニットをリアルタイムで監視する方法を開示する。本方法は、1つまたは複数のCPUに関連する状態データをリアルタイムで監視するステップと、状態データをフィルタ処理するステップと、フィルタ処理された状態データに少なくとも部分的に基づいて、1つまたは複数のシステム設定を選択的に変更するステップと含み得る。  (もっと読む)

(もっと読む)

仮想CPUベースの、周波数、及び電圧制御

【課題】仮想環境の各々の仮想プロセッサのために実行される周波数、及び電圧制御を統合して、性能を犠牲にせずにパワーセービングを達成する。

【解決手段】各々の仮想プロセッサによって実行されるワークロードの特徴は、動的にプロファイルが作られ、かつ制御アルゴリズム140a〜140nは、前記プロファイルが作られた特徴の関数として、その仮想プロセッサのための制御ファクタを決定する。プロファイルが作られた特徴は、実行されている前記ワークロードに関連づけられた、仮想化イベントを含んでもよく、加えて、特定の制御アルゴリズム、及びプロファイリング技術は、どの仮想プロセッサが現在動作しているかに基づいて選択されてもよい。

(もっと読む)

共振クロック分配ネットワークの周波数スケール調整された作動のためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。このアーキテクチャにより、選択的にイネーブルされるフリップフロップの導入によって、複数のクロック周波数での共振クロック分配ネットワークのエネルギ効率の良い作動が可能になる。提示されたアーキテクチャは、主として一体化インダクタを有する共振クロックネットワーク設計を目的としており、インダクタのオーバヘッドが出現しない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

電子回路

【課題】電子回路(例えば、マイクロコンピュータ)の動作モードに応じて、低周波数の発振器について適切な電源インピーダンスを設定することにより、前記発振器の誤動作を防止しながら、消費電力を適切に低減することができる。

【解決手段】システムクロックのクロック源として、高速発振器11、中速発振器12、低速発振器13が設けられる。また、時計用クロックを発生する水晶発振器30が設けられる。そして、高速発振器11が動作している時は、水晶発振器30の電源インピーダンスを低くして、耐ノイズ性を高める。一方、高速発振器11、中速発振器12、低速発振器13がすべて停止している待機時には、水晶発振器30の電源インピーダンスを高くして消費電力を抑える。

(もっと読む)

情報処理装置、バス制御装置

【課題】一番周波数の低い二次側接続装置に合わせることなく個々の二次側接続装置の最大動作周波数で動作可能な情報処理装置にする。

【解決手段】基準発振信号PCICLK_0を供給する主装置3Aを接続部20_0に接続する。二次側には、主装置3Aの指示に基づき情報処理を行なう二次側接続装置が装着される接続部20_@を設ける。接続回路10Aは、基準発振信号PCICLK_0の供給を受け、各二次側接続装置のそれぞれの動作可能周波数に対応する基準発振信号PCICLK_@を生成して各別の基準発振信号線22_@を介して出力する。接続回路10Aは、主装置3Aと各二次側接続装置の基準発振信号PCICLKの周波数の違いを吸収するので、各二次側接続装置の最大の周波数を使用することが可能となる。一番周波数の低い二次側接続装置に合わせることなく個々の二次側接続装置の最大動作周波数で動作可能になり生産性が向上する。

(もっと読む)

プロセッサシステム

【課題】 動作周波数を上限周波数までの範囲内で動的に切り替えることにより、省電力を図りながら処理効率を向上させることができるようにする。

【解決手段】 ハードウェア(HW)プロファイル保持部113は、プロセッサ101の定格周波数及び上限周波数を含むプロファイル情報を保持する。クロック周波数管理部102は、演算回路111での画像データの処理に際し、プロセッサ101の演算動作時間とアイドル時間とから該プロセッサ101の稼働率を検出し、該稼働率が100パーセントとなった時、HWプロファイル保持部113に保持された定格周波数と上限周波数に基づき、該プロセッサ101の動作周波数を、上限周波数の範囲内で、かつ、定格周波数よりも高い値に可変設定する。

(もっと読む)

情報処理装置及びそのクロック制御方法並びにクロック制御プログラム

【課題】ユーザの意図する処理が実行されるときだけオーバークロックを行って、処理の高速化と低消費電力化を両立させる。

【解決手段】メモリ部22にオーバークロック対象の情報処理が予め1以上登録される。登録判定部23は、情報処理の起動時に当該情報処理が登録されているか否かを判定する。登録されている場合には、クロック制御部24は、登録されている全ての情報処理に対する識別を確認する。実行中を示す識別が1つでも有るときには、クロック変更部25にクロック周波数のアップを指令する。登録判定部23は、情報処理の終了時にも、当該情報処理が登録されているか否かを判定する。登録されている場合には、クロック制御部24は、登録されている全ての情報処理に対する識別を確認する。実行中を示す識別が1つも無いときは、クロック変更部25にクロック周波数のダウンを指令する。

(もっと読む)

情報処理装置、情報処理方法、情報処理プログラム

【課題】情報処理装置の排気温度を予測することで、情報処理装置の発熱増加を極力抑制する情報処理装置を提供する。

【解決手段】情報処理装置に一つまたは複数搭載される処理ユニットに新たなプログラムを実行した場合の前記情報処理装置の温度を予測する予測ユニット1と、前記温度と所定の基準値を比較する温度判定ユニット2と、前記温度が前記所定の基準値を上回る場合、前記新たなプログラムと既に実行中の実行プログラムとの優先度を比較する優先度判定ユニット3と、前記新たなプログラムの優先度が前記実行プログラムの優先度を上回る場合、前記新たなプログラムを前記処理ユニットに実行させても前記温度が前記所定の基準値を上回らない動作クロックを前記処理ユニットに設定し、前記新たなプログラムを前記処理ユニットに実行させる動作クロック設定ユニット4と、を備える情報処理装置を提供する。

(もっと読む)

情報処理装置、情報処理方法、プログラム及び記録媒体

【課題】情報処理装置のデータ処理手段により、処理するデータに応じた電力モードでデータを処理して消費電力を低減する。

【解決手段】CPU21を有するASIC20のネットワークコントローラ40と、ネットワークとの接続部であるPHY15とを接続してパケットを送受信する。省電力モード時にパケットを受信したときには、ネットワークコントローラ40により、受信パケットの処理の要否を判定して、処理不要のときには受信パケットを破棄する。また、処理要のときには、クロックジェネレータ22によりクロック周波数を変更する等して、CPU21の電力モードを受信パケットに応じた電力モードに切り替え、受信パケットの処理等を実行させる。

(もっと読む)

仮想計算機システム及び同システムにおけるゲストOSスケジューリング方法

【課題】CPUの動作周波数が低下しても、ゲストOSのリアルタイム処理性能を維持できるようにする。

【解決手段】VMM(仮想計算機マネージャ)20は、CPU110を含むHW11を仮想化することによりVM(仮想計算機)30-0〜30-4を構築する。VM30-0〜30-4上ではゲストOS40-0〜40-4が実行される。CPU周波数変化検出部204はCPU110の動作周波数の変化を検出する。ゲストOSスケジューラ201は、上記動作周波数の変化が検出され、且つ当該動作周波数が規定動作周波数から低下した場合、ゲストOS40-0〜40-4のうちの特定ゲストOSが当該規定動作周波数での動作で必要とするCPU絶対処理量を維持するために、当該特定ゲストOSにCPU110が割り当てられるべき時間が増えるようにスケジューリングを行う。

(もっと読む)

半導体集積回路装置、データ処理装置及びマイクロコンピュータ

【課題】SDRAMの動作マージンを拡大させて直接にアクセスすることができる半導体集積回路装置を提供する。

【解決手段】中央処理装置、外部に接続されるメモリのインタフェース機能を有する制御回路、中央処理装置に対する第1クロック信号、外部に接続されるSDRAMに供給するための第2クロック信号を含む複数のクロック信号を形成可能なクロック発生回路、SDRAMのクロック端子に対し、第2クロック信号を供給するための第1端子、SDRAMに対するクロックイネーブル信号を出力するための第2端子、及びSDRAMに対し、セレクト信号を出力するための第3端子を有する。制御回路は、SDRAMに対し、第2クロック信号に同期して、第2端子を介して前記クロックイネーブル信号を出力し、第3端子を介してセレクト信号を出力する。

(もっと読む)

クロック生成制御回路

【課題】 CPUの負荷を軽減することが可能なクロック生成制御回路を提供する。

【解決手段】 本願発明は、発振回路が出力するクロック信号のパルス数を所定期間カウントし、所定期間及び周波数に応じた設定値と等しくなったときにカウント制御信号の出力レベルを切り替えるカウンタと、所定期間を示すタイミング信号とカウント制御信号とのタイミングの誤差を検出し、誤差検出信号を出力する誤差検出回路と、を備え、周波数制御回路は、誤差検出信号に基づいて制御信号を生成することで、上記課題を解決することができる。

(もっと読む)

データ処理装置

【課題】連続したデータを信号処理するためにかかる消費電力を削減することができるデータ処理装置を提供する。

【解決手段】第1のデータ格納部110に格納されたデータに複数の信号処理を施す第1の信号処理部120と、第1の信号処理部120によって処理されたデータを格納する第2のデータ格納部112と、第2のデータ格納部112に格納されたデータを実時間処理で読み出して信号処理を行う第2の信号処理部130と、データの特徴に基づいて各信号処理をパイプラインステージに割り振ったパイプライン構成で第1の信号処理部120にデータを処理させると共に、各信号処理を実時間処理より速い速度で行わせることで間欠動作させるよう第1の信号処理部120を制御する信号処理制御部150と、間欠動作の停止期間に第1の信号処理部120および信号処理制御部150に対するクロックや電源の供給を制限するクロック/電源制御部160とを備える。

(もっと読む)

半導体集積回路装置及びデューティ制御方法

【課題】動作速度を向上出来る半導体集積回路装置及びデューティ制御方法を提供すること。

【解決手段】第1クロックCLK1に同期して動作し、該第1クロックCLK1が“H”レベルでアクティブとなる第1クリティカルパス12と、“L”レベルでアクティブとなる第2クリティカルパス13とを含むプロセッサコア2と、第2クロックCLK2のデューティを制御して前記第1クロックCLK1を生成する第1クロック生成部3と、前記第1クロックCLK1と、前記第1クリティカルパス12で生じる遅延時間Δtd1だけ遅れた第3クロックCLK3との第1位相差UPと、前記第1クロックCLK1と、前記第2クリティカルパス13で生じる遅延時間Δtd2だけ遅れた第4クロックCLK4との第2位相差DNとが最小となるように前記デューティを制御するよう、前記第1クロック生成部3に命令する制御部4とを具備する。

(もっと読む)

クロック信号分配回路、情報処理装置及びクロック信号分配方法

【課題】集積回路に供給するクロック信号を分配するためのクロックツリーの構成に関し、最適なクロックツリーを容易に構成し得るクロック分配方法を提供することを目的とする。また、BIST回路を内蔵した評価用のLSIのテストを、短時間で実行できるようにしたクロックツリーのクロック分配方法を提供することを目的とする。

【解決手段】複数のセルに試験パターンを入力するステップと、第1のセルから第2のセルへデータ信号を転送させるステップと、第1のセル及び第2のセルへクロック信号を分配させ、データ信号の転送方向と同方向にクロック信号を転送させるステップと、転送されたクロック信号に基づき、試験パターンを複数のセルに入力し、複数のセルから出力される試験パターンの結果から、複数のセルの故障を検出させるステップとを有する情報処理装置のテスト方法。

(もっと読む)

フィールド機器

【課題】電力を供給する伝送線路に接続され、演算処理を実行し外部機器と通信を行うフィールド機器において、伝送線路から供給される電流と演算処理に対する動作クロック周波数を可変して、低消費電力用または高速演算処理用を1種類の構成で実現するフィールド機器を提供すること。

【解決手段】電力を供給する伝送線路に接続され、演算処理を実行し外部機器と通信を行うフィールド機器において、前記伝送線路から供給される電流と前記演算処理に対する動作クロック周波数を、少なくとも2段階に可変するための設定データを出力する設定部と、前記設定データに基づき前記伝送線路から供給される電流を可変する電流可変部と、前記設定データに基づき前記演算処理に対する動作クロック周波数を可変する周波数可変部を備えた、ことを特徴とするもの。

(もっと読む)

クロックゲーティング方式

【課題】クロックゲーティング用イネーブル信号のオン/オフを切り換えても、供給するクロックにジッタが生じることのないクロックゲーティング方式を提供する。

【解決手段】クロックに対するゲーティング適用回路100およびゲーティング非適用回路200へクロックを供給するクロックバッファ1の出力端に、ゲーティング適用回路100へ供給するゲーテッドクロックを生成するゲーティング用論理ゲート回路2と、ゲーティング用論理ゲート回路2と同一の構成を有する負荷調整用論理ゲート回路3とを並列に接続し、ゲーティング用論理ゲート回路2へはクロックゲーティング用イネーブル信号Eを入力し、負荷調整用論理ゲート回路3へはイネーブル信号Eをインバータ4で極性反転させた反転イネーブル信号EBを入力する。

(もっと読む)

1 - 20 / 60

[ Back to top ]