Fターム[5B079DD13]の内容

Fターム[5B079DD13]に分類される特許

1 - 20 / 162

電力の島を使用した集積回路での電力の管理

半導体装置

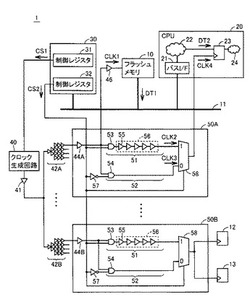

【課題】不揮発性メモリを備えた半導体装置において、高速動作の場合と低速動作の場合とに切替え可能にするとともに、低速動作時の消費電力を従来よりも削減する。

【解決手段】半導体装置1において、クロック生成回路40は、高周波モード時には低周波モード時よりも周波数の高いクロックを生成する。中央処理装置20は、データバス11を介して不揮発性メモリ10から読み出された読出データを取得する。クロック遅延部50Aは、縦続接続された複数段のバッファ55を介した第1の経路51と複数段のバッファ55を迂回した第2の経路52とを含む。クロック遅延部50Aは、高周波モード時には、クロック生成回路40からのクロックを第1の経路51を介して中央処理装置20に供給し、低周波モード時には、クロック生成回路40からのクロックを第2の経路52を介して中央処理装置20に供給する。

(もっと読む)

分周回路

【課題】分周回路の動作不良を抑制する。

【解決手段】第1又は第2のクロック信号に従って2×X個(Xは2以上の自然数)のパルス信号を生成して出力するシフトレジスタと、2×X個のパルス信号に従って、第1のクロック信号の周期のX倍の周期である第3のクロック信号となる信号を生成して出力する分周信号出力回路と、を具備し、分周信号出力回路は、ゲートのそれぞれに、2×X個のパルス信号における1個目乃至X個目のパルス信号のうち、互いに異なるパルス信号が入力され、第3のクロック信号となる信号の電圧を第1の電圧に設定するか否かを制御するX個の第1のトランジスタと、ゲートのそれぞれに、2×X個のパルス信号におけるX+1個目乃至2×X個目のパルス信号のうち、互いに異なるパルス信号が入力され、第3のクロック信号となる信号の電圧を第2の電圧に設定するか否かを制御するX個の第2のトランジスタと、を備える。

(もっと読む)

グリッチフリークロック信号マルチプレクサ回路および動作の方法

【課題】クロックマルチプレクサを駆動する第1のクロック入力から第2のクロック入力への切換えにおいて起こるグリッチを低減する。

【解決手段】クロックマルチプレクサ116は、第1のクロック入力を受信し、クロック出力118を提供し、第1のクロック出力における低フェーズ入力レベルに応答してクロック出力における低フェーズ出力レベルを判定する。限定された期間、低フェーズ出力レベルは、第1のクロック入力信号のフェーズレベルに関わらず維持される。クロックマルチプレクサ116は、第2のクロック入力を受信し、第2のクロック入力信号における低フェーズ入力レベルを判定する。第2のクロック入力に応答してクロック出力118を提供することへの切換えは、第2のクロック入力信号における低フェーズ入力レベルの間に起こる。その後、クロックマルチプレクサ116の出力は第2のクロック信号のフェーズレベルに従う。

(もっと読む)

半導体集積装置およびそれを備える表示装置

【課題】電磁波の不要輻射および伝送欠陥を低コストで低減することができる、半導体集積装置およびそれを備える表示装置を提供することを目的とする。

【解決手段】タイミングコントローラIC400が含む出力インターフェース回路420_1は、出力バッファ422と、出力バッファ422の後段に設けられた減衰部424とを有している。出力バッファ422は、正側画像信号DV1(+)および負側画像信号DV1(−)からなる差動信号を出力する。減衰部424は、1対のローパスフィルタ425Aおよび425Bを有している。ローパスフィルタ425Aおよび425Bにより高周波成分がそれぞれ減衰された正側画像信号DV1(+)および負側画像信号DV1(−)は、それぞれ伝送線路610Aおよび610Bに与えられる。

(もっと読む)

複数の回路における性能パラメータの整合

【課題】複数の回路の性能パラメータを整合するためのシステム及び方法を提供する。

【解決手段】複数のドメインにおいて性能パラメータを整合するシステム及び方法が開示される。方法は、第1ドメイン及び第2ドメインを含む電子回路の状態を切り換えるための要求を受け取り、第1ドメインに作用する第1回路の第1パラメータを、その要求に基づいて第1の変更パラメータへと変更させ、そして第2ドメインに作用する第2回路の第2パラメータを、その要求に基づいて第2の変更パラメータへと変更させることを含む。あるケースでは、パラメータは、クロック周波数を含む。他のケースでは、パラメータは、電圧を含む。ある実施形態では、システムは、ロジック回路及び/又はシステムオンチップ(SoC)として具現化される。

(もっと読む)

電力の島を使用した集積回路での電力の管理

【課題】集積回路において、消費電力を効率的に利用することを目的とする。

【解決手段】システム及び方法は、電力の島を使用して集積回路の電力を管理する。集積回路は、消費電力が電力の島のそれぞれで独立して制御される複数の電力の島を有する。電力マネージャは、電力の島のうち1つの目的の電力レベルを決定する。電力マネージャは、電力の島のうち1つの消費電力レベルを目的の電力レベルに変更する動作を決定する。電力マネージャは、電力の島のうち1つの消費電力レベルを目的の電力レベルに変更する動作を実行する。

(もっと読む)

集積回路、クロックゲート回路、および方法

【課題】本発明は、集積回路に渡ってクロック信号を分配する時に消費される、電力の量を減少するための技術に関する。

【解決手段】集積回路2は、動作クロック周波数を有する動作クロック信号に応じて作動するように配設される、機能回路4、6を備える。電力を節約するために、クロック信号は、動作クロック周波数よりも低い分配クロック周波数で、集積回路2に渡って分配される。クロック変換器10は、機能回路4、6の動作を制御するために、分配クロック信号を動作クロック信号に変換するように提供される。

(もっと読む)

プロセッサ、半導体集積回路装置及びプロセッサシステム

【課題】複数の周辺回路を備えたプロセッサ、半導体集積回路装置及びプロセッサシステムの処理能力を低下させることなく、消費電流を低減するプロセッサ、半導体集積回路装置及びプロセッサシステムを提供する。

【解決手段】プロセッサコア2と、プロセッサコア2からの命令に応答して所定の処理を実行する周辺回路3−1,3−2とを備えるプロセッサ7において、各周辺回路3−1,3−2は、プロセッサコア2からの命令に基づいて第1の全処理サイクル数を算出する算出部100と、比較部300からの分周比に基づいて、クロック信号を分周して出力するクロック発生部400と、第1の全処理サイクル数を、他の周辺回路の算出部100によって算出される上記他の周辺回路の第2の全処理サイクル数と比較して、当該比較結果に基づいて、当該周辺回路の処理終了時刻が上記他の周辺回路の処理終了時刻に近づくように上記分周比を発生する比較部300とを備えて構成される。

(もっと読む)

クロック分周回路

【課題】 複数のクロックの分周比を同時に切り替えることで、クロック分周回路が搭載されるシステムの性能を向上する。

【解決手段】 クロック分周回路は、クロックの分周比を外部より設定可能な複数の分周器、プリセットレジスタ群およびセレクタを有している。プリセットレジスタ群は、複数の分周器に設定する分周比を格納する。セレクタは、プリセットレジスタ群の内、1つのプリセットレジスタを選択し、選択したプリセットレジスタに格納されている分周比を複数の分周器に与える。セレクタの選択動作により複数のクロックの分周比を同時に切り替えることができ、クロック分周回路が供給される回路ブロックの動作効率を向上できる。

(もっと読む)

半導体集積回路のクロック遅延調整回路およびその制御方法

【課題】回路規模が増大する問題があった。

【解決手段】複数の回路ブロックと、入力するクロック信号を遅延制御信号に基づいて遅延したクロック信号を対応する前記複数の回路ブロックに供給する複数のクロック遅延回路と、前記複数の回路ブロックの遅延試験を行う制御回路と、前記遅延試験の結果に応じて、前記複数の回路ブロックのうち遅延処理が必要な回路ブロックの情報を記憶する救済グループ記憶回路と、前記遅延試験の結果に応じて、前記複数の回路ブロックのうち遅延処理が必要な回路ブロックの遅延値情報を記憶する、所定数の遅延設定回路と、前記救済グループ記憶回路が記憶した回路ブロックの情報に対応したクロック遅延回路に対し、前記遅延設定回路が記憶した遅延値情報に応じた前記遅延制御信号を割り当てる遅延設定割当制御回路と、を有する半導体集積回路のクロック信号調整回路。

(もっと読む)

プロセッサスリープ及びウェイクイベントに対するシステムのハードウェア自動性能状態移行

半導体装置

【課題】クロックや電源の制御を効率よく、且つ、確実に実行可能にして、消費電力を削減する。

【解決手段】本発明の半導体装置は、複数の回路ブロック2、12と、複数の回路ブロック2、12と電源9との間に設けられたスイッチ10と、複数の回路ブロック2、12に各別にクロック信号を出力する複数のクロック出力回路と、複数の回路ブロック2、12の中の少なくとも1個の回路ブロックへクロック信号が出力された時点で、スイッチ10をオンして有う複数の回路ブロック2、12の電源をすべてオンし、複数の回路ブロック2、12へのクロック信号がすべて停止された時点で、スイッチ10をオフして複数の回路ブロック2、12の電源をすべて遮断するように制御するブロック電源制御回路とを備えたものである。

(もっと読む)

集積回路のメモリインターフェースのためのデューティサイクル補正器回路

集積回路(IC)内のデューティサイクルの歪みを補正するための回路および方法が、開示される。ICは、クロック信号を受信するように連結されるスプリッタ回路を含む。クロック信号は、2つの異なるクロック信号に分割される。クロック信号のうちの1つは、他方の反転したバージョンである。遅延回路は、クロック信号の各々に連結される。遅延回路の各々は、対応するクロック信号の遅延したバージョンを発生させる。補正器回路は、クロック信号の遅延したバージョンの両方を受信するように連結される。補正器回路は、補正されたデューティサイクルを有するクロック出力信号を発生させる。  (もっと読む)

(もっと読む)

多相クロック間の相間スキュー検出回路、相間スキュー調整回路、および半導体集積回路

【課題】N相クロックの相間スキューの検出を行なうための基準クロックを半導体集積回路内で生成する。

【解決手段】分周回路14は、N相(4相)クロックCLK1/CLK2/CLK3/CLK4をN+1個(6個)の分周クロックA4(−1)/A1(0)/A2(0)/A3(0)/A4(0)/A1(+1)に分周し、位相比較対象クロック生成回路12は、分周クロックA1(0)/A2(0)/A3(0)/A4(0)から位相比較対象クロックB1/B2/B3/B4を生成する。位相比較基準クロック生成回路13は、分周クロックA4(−1)/A1(0)/・・・/A1(+1)から所定の組み合わせと演算規則に従いN個(4個)の基準クロックC1/C2/C3/C4を生成する。そして、位相比較対象クロックB1/B2/B3/B4と基準クロックC1/C2/C3/C4のそれぞれの位相差を検出する。

(もっと読む)

論理回路設計支援方法及び装置

【課題】 実動作において低消費電力化が図れるゲーティッドクロック設計が可能な論理回路設計支援方法を提供する。

【解決手段】 最適化対象論理回路の回路構造を記述した回路データD1に基づいて、最適化対象論理回路に入力する複数のイネーブル信号の情報D2を抽出する第1ステップS1と、最適化対象論理回路と抽出された複数のイネーブル信号の生成論理に対して実動作モードの論理シミュレーションを実行して、イネーブル信号毎の動作時におけるアクティブ状態と非アクティブ状態間の状態遷移に係る時系列情報D4を取得する第2ステップS2と、時系列情報D4に基づいて、最適化対象論理回路とクロックゲーティング回路の合計消費電力が、クロックゲーティング回路を挿入する前の最適化対象論理回路の消費電力より低減されるように、クロックゲーティング回路の挿入個数及び挿入箇所を最適化する第3ステップS3〜S5を有する。

(もっと読む)

ベクトル処理装置、ベクトル処理方法、およびプログラム

【課題】 ベクトル処理において、ベクトルマスク制御やベクトル長制御により、ベクトル命令で読み書きが行われない要素に対する制御で消費電力を低減する。

【解決手段】 同一要素番号を有する要素を要素単位でSRAMに格納する要素単位ベクトルレジスタと、要素単位ベクトルレジスタからの要素の読み出し、要素間の演算、および要素単位ベクトルレジスタへの演算の結果の書き込みを制御するベクトル演算処理部と、マスク制御またはベクトル長制御により読み書きが行われない要素単位で要素単位ベクトルレジスタのクロックを停止するクロック停止処理部と、を備える。

(もっと読む)

半導体集積回路

【課題】独立してクロック信号の供給と遮断が行われる領域を有する半導体集積回路において、クロックスキューを低減し、かつ、消費電力を低減すること

【解決手段】本発明にかかる半導体集積回路1は、クロック信号が供給される第1の配線と、第1の配線に供給されるクロック信号とは独立して供給と遮断とが切り替えられてクロック信号が供給される第2の配線と、第1の配線からクロック信号が供給される第1のメッシュ形状配線を有する第1の領域と、第2の配線からクロック信号が供給される第2のメッシュ形状配線を有する第2の領域と、第1のメッシュ形状配線と第2のメッシュ形状配線の間の信号の導通と遮断を切り替え可能な切り替え回路とを備える。

(もっと読む)

半導体集積回路およびパワーゲーティング制御方法

【課題】搭載される機能ブロックの個数によらず、一定数の少数の配線のみでパワーゲーティング制御を行うことのできる半導体集積回路およびパワーゲーティング制御方法を提供する。

【解決手段】パワーゲーティング制御情報生成部1が、機能ブロックBLK1〜BLK3に対するパワーゲーティング制御情報PGCを生成し、クロック信号制御部2が、クロック信号CK0にパワーゲーティング制御情報PGCを重畳し、機能ブロックBLK1〜BLK3へ供給するクロックとなるクロック信号CKを生成し、機能ブロックBLK1〜BLK3のそれぞれと一体に1個ずつ配置されたパワーゲーティング制御部31〜33が、クロック信号CKに重畳されたパワーゲーティング制御情報PGCを解読して、機能ブロックBLK1〜BLK3に対するパワーゲーティング制御信号PG1〜PG3をそれぞれ生成する。

(もっと読む)

回路設計方法、及び回路設計プログラム

【課題】論理合成済みの回路に対して容易かつ高精度にクロックゲーティングセルを挿入することができる回路設計方法、及び回路設計プログラムを提供することである。

【解決手段】本発明にかかる回路設計方法は、設計者の意図する論理に基づいて、クロックゲーティング条件を含まないRTL記述ファイルを作成する第1のステップ(ステップS1)と、論理合成ツールを用いて、RTL記述ファイルに基づき第1のネットリストを生成する第2のステップ(ステップS2)と、第1のネットリストにクロックゲーティングセルを挿入して第2のネットリストを生成する第3のステップ(ステップS3)と、自動レイアウトツールを用いて、第2のネットリストに含まれるセルの配置を決定する第4のステップ(ステップS4)と、を有する。

(もっと読む)

1 - 20 / 162

[ Back to top ]