Fターム[5B083CC06]の内容

計算機における入出力系RAS (2,172) | 手段(検出、診断、管理系) (296) | 比較照合 (87)

Fターム[5B083CC06]に分類される特許

1 - 20 / 87

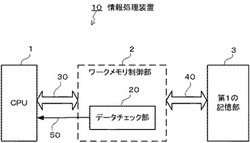

情報処理装置及び記憶部検査方法

【課題】CPUの運用中においても、記憶部の検査のためにCPUによるソフトウェアのデータ処理を一時停止させることがなく、記憶部の異常の有無をチェックすることができる情報処理装置及び記憶部検査方法を提供する。

【解決手段】CPU1とは独立に設置された記憶制御部2は、CPU1から書き込みようの処理データと書き込み先の記憶部3の指定アドレスを受け、検査用データを指定アドレスに書き込み、それを読み出す。記憶制御部2が備えるデータチェック部20は、検査用データと読み出されたデータとを比較し、一致するかどうかを判定する。一致しなければ指定アドレスに異常があると判定し、その旨をCPU1に通知し、一致すれば、記憶制御部は処理データを指定アドレスに書き込む。

(もっと読む)

バス診断機能を備えた制御装置

【課題】安全関連部と非安全関連部が混在している制御装置において、中央処理部が安全関連部にアクセスしたときのみ、データバス及びアドレスバス上の転送エラーを検知する制御装置を提供する。

【解決手段】制御装置の集積回路6a内に、CPU1aが安全関連レジスタにアクセスする際に、安全関連レジスタの値を格納するデータバス診断レジスタ12と、アドレスバスの値を格納するアドレスバス診断レジスタ13と、CPU1aが安全関連レジスタにアクセスする際にのみ、データバス診断レジスタ12に安全関連レジスタの値を、アドレスバス診断レジスタに13アドレスバスの値を夫々格納させるためのバス診断信号(CHKBUS)15を、データバス診断レジスタ12及びアドレスバス診断レジスタ13に供給するバス診断アドレス判定部14とを設ける。

(もっと読む)

1553バス動作の自己検査のためのシステムおよび方法

【課題】1553バス動作の自己検査のためのシステムおよび方法を提供する。

【解決手段】1553自己検査論理は、1553バストランシーバと自己検査プロセッサペアとのデータ通信を管理する。1553自己検査論理は、ロックステップで動作する一次論理および二次論理を含む。1553自己検査論理が1553バストランシーバにデータを書き込むとき、1553自己検査論理は、一次論理によって生成された第1の1553フォーマット済みメッセージを、二次論理によって生成された第2の1553フォーマット済みメッセージと比較し、第1の1553フォーマット済みメッセージが第2の1553フォーマット済みメッセージと一致しないときに、エラー表示を生成する。

(もっと読む)

異常検出回路及び回路の異常検出方法

【課題】回路面積の増大を抑制することができる異常検出回路及び回路の異常検出方法を提供すること

【解決手段】本発明にかかる異常検出回路4は、複数の入力信号に対応した複数の出力信号を出力するバッファ群3に設けられる。異常検出回路4は、複数の入力信号に基づく固有信号MISROUT1を生成するMISR回路5と、複数の出力信号に基づく固有信号MISROUT2を生成するMISR回路6と、両固有信号の不一致を検出して異常信号を特定する異常信号特定回路7を備える。異常信号特定回路7は、両固有信号の不一致を検出した場合、制御信号CAPTUREを生成し、MISR回路5、6は、当該制御信号に応じて、複数の入力信号、出力信号を異常信号特定回路7に順次出力する。異常信号特定回路7は、複数の入力及び出力信号との不一致を順次検出することによって、複数の入力及び出力信号における異常信号を特定する。

(もっと読む)

システム、ホスト装置及びエラー検出方法

【課題】端子の接触不良を検出する回路の故障を検出可能なシステム、ホスト装置及びエラー検出方法等を提供すること。

【解決手段】システムはホスト装置10と記憶装置20を含む。記憶装置20は、不揮発性の記憶部60と、不揮発性の記憶部60に対するアクセス制御を行うアクセス制御部36と、電源端子TV及びグランド端子TGの少なくとも一方のフローティング状態を検出する検出回路32と、を有する。ホスト装置10は、電源電圧VDD及びグランド電圧VSSのうちのフローティング状態が検出される検出対象電圧の供給・非供給を切り換える切り換え回路50と、検出対象電圧が非供給に設定された場合の記憶装置20からの信号に基づいて検出回路32が正常であるか非正常であるかを判定する判定部70と、を有する。

(もっと読む)

PCIバス制御システム

【課題】イニシエーターとターゲットとをPCIバスにより接続したPCIバス制御システムに関し、コマンドエラーを回避する。

【解決手段】

イニシエーター1とターゲット2−1,2−2との間をPCIバスにより接続したPCIバス制御システムであって、監視回路3と救済回路4とを設け、PCIバスによりイニシエーター1とターゲット2−1,2−2間を監視回路3と救済回路4とを介して接続すると共に、イニシエーター1と監視回路3と救済回路4との間を、コマンドCOMMとパリティPARとパリティエラーPERRとを転送するローカルバスにより接続し、監視回路3によりコマンドのパリティチェックを行って送出し、救済回路4は、PCIバスとローカルバスとを介してそれぞれ転送されたコマンドについて、正常な側を選択して、ターゲット2−1,2−2にコマンドを転送する構成を備えている。

(もっと読む)

電子端末装置及び電子連動装置

【課題】CPUから入出力のポートを指定する出力用アドレスバスと入力用アドレスバスのアドレスバスを共通化してアドレスバスのいずれかのビットに生じた固定故障を確実に検知する。

【解決手段】 出力用アドレスデコーダ13及びフィードバック用アドレスデコーダ14とCPU11との間を共通のアドレスバス18で接続し、出力用アドレスデコーダ13の制御出力端子を指定するアドレスとそれに対応するフィードバック用アドレスデコーダ14の制御出力端子を指定するアドレスはデコード順を逆に設定して、アドレスバス18のいずれかのビットが「0」又は「1」に固定故障すると正常と異なる入力ポート16をCPU11で読み取り、アドレスバス18の固定故障を確実に検知する。

(もっと読む)

情報処理装置及びその作動方法

【課題】モジュールと本体側コネクタ間の接続不良に起因してモジュールが動作不良と判断されてしまうおそれがある。

【解決手段】サーバー100は、複数の接点を介してメモリ装置10が接続され、複数の接点を介してメモリ装置10から複数ビットのデータが入力するコネクタ20と、コネクタ20を介して入力する複数ビットのデータに含まれるビットにエラーが生じているか否かを判断するビットエラー検出部41と、ビットエラー検出部41によりエラーが検出されたビットに対応する接点を含む第1配線と、ビットエラー検出部41によりエラーが検出されなかったビットに対応する接点を含む第2配線と、に対してテスト波形を入力し、このテスト波形に応じて第1及び第2配線夫々にて生じる反射波のレベル差を評価することで第1配線の状態を判定する接続確認回路50と、を備える。

(もっと読む)

マイコン、処理同期方法

【課題】一方のコアから他方のコアに割込みによりイベントを通知する際、イベントの誤通知を検知できるマイコンを提供すること。

【解決手段】第1のコア52と第2のコア53間で通信する通信手段43と、第1のコアと第2のコアが共有する共有メモリ51と、外部信号を取得して第1の処理を実行し、第1の処理毎に所定情報を共有メモリに書き込む第1の処理手段55と、通信手段を介して第2のコアに処理要求を出力する処理要求手段33と、処理要求をトリガーに第2の処理を実行する第2の処理手段56と、を有するマイコン100において、第2のコアは、処理要求を受け付けた場合、共有メモリから最新の所定情報と前回の所定情報を読み出し、最新の所定情報と前回の所定情報に規定された関係がある場合のみ、第2の処理手段に第2の処理の実行を許可する比較手段57、を有する。

(もっと読む)

バス接続回路及びバス接続方法

【課題】I2Cバス接続された周辺部品がBus-Busyとなった場合でも、システム全体が動作し続けることができるようにすること。

【解決手段】本発明のバス接続回路21は、周辺部品側のI2C端子レベルを検出するバッファ24と、周辺部品とシステム全体のI2Cバスとを切り離すSW25と、I2C故障検出制御モジュール26と、周辺部品側がHi-Z状態になっているかを確認するためのPull Up抵抗34と、Pull Down抵抗35と、を備える。I2C故障検出制御モジュール26は、バッファ24で受けた値が、Highレベルか、それともLowレベルであるかを判断するH/Lレベル検出部30と、Lowレベルの持続時間を測るLowレベル検出時間計測部31と、SW25をON/OFF制御するI2Cバス切断制御部32と、Pull抵抗制御部33と、を備える。

(もっと読む)

シリアル通信カード試験装置

【課題】大量の高速シリアルデータの送受信を複数回繰返す動作確認試験を試験員が手作業で行うことは長時間を要する。

【解決手段】一実施形態によれば、シリアル通信路と、基準シリアル通信カードと、被試験シリアル通信カードと、記憶部及びCPUを持つ第1の処理装置と、ネットワークと、記憶部及びCPUを持つ第2の処理装置と、これらの処理装置の各記憶部に各試験プログラムをロードし、操作指令を発行して各シリアル通信カード間の送受信を制御する制御装置とを備え、この制御装置は、各シリアル通信カードにシリアルデータの送受信を複数回繰返させ、送受信終了後、各記憶部からそれぞれ送受信データを収集し、データの相互比較により被試験シリアル通信カードの動作確認試験を行うシリアル通信カード試験装置が提供される。

(もっと読む)

情報処理装置及び方法、並びにプログラム

【課題】端末情報により特定される端末と、当該端末情報を登録している情報処理装置とを含むシステムにおいて、情報処理装置側でデータロストが発生した場合であっても、情報処理装置と端末との間で端末情報の整合性を保つこと。

【解決手段】端末情報受信部32は、DPF端末10から送信される端末固有IDと、端末固有IDに対応するメールアドレスとを含む端末情報の少なくとも一部、具体的には端末固有IDを受信する。登録有無検出部33は、端末情報受信部32により少なくとも一部取得された端末情報が、DB40に登録されているか否かを判定する。端末情報整合部34は、登録有無検出部33により端末情報が登録されていない場合、新たなメールアドレスを発行し、端末情報受信部32に受信された端末固有IDと対応付けて、新たな端末情報としてDB40に登録すると共に、新たなメールアドレスをDPF端末10に送信する。

(もっと読む)

入出力接続装置、情報処理装置及び入出力デバイス検査方法

【課題】入出力デバイス内部の異常を早期に検出する。

【解決手段】生成部11は、パケットを一意に識別するタグを付与した検査用パケットを生成し、送信部12は、検査用パケットを入出力デバイスへ送信する。受信部13は、パケットを受信し、第1判定部14は、受信部13によって受信された受信パケットのタグに基づいて、該受信パケットが、送信部12から送信された検査用パケットに対する応答パケットであるか否かを判定する。第2判定部15は、第1判定部14によって受信パケットが応答パケットであると判定された場合に、受信パケットを解析して、入出力デバイスが異常であるか否かを判定する。

(もっと読む)

インターフェース装置

【課題】有線で結ばれるホスト装置とクライアント装置といった通信装置の間でデータ転送を行うインターフェース装置において、ホスト装置からクライアント装置へのデータ転送中にデータ転送を中断することを可能とする。

【解決手段】ホストコントローラ102を、デジタル信号を送信手段200によりストローブ信号とデータ信号とに変換し、データ信号221を差動ラインドライバ202により一対の差動データ信号221aおよび221bに変換して一対の差動ラインDL1およびDL2に出力するよう構成し、しかも、クライアントコントローラでは、該差動ラインDL1およびDL2が形成する通信路のインピーダンスを変換するインピーダンス変換手段209を設け、ホストコントローラ102で、この通信路のインピーダンスの変化を検出するようにした。

(もっと読む)

ペリフェラル・コンポーネント・インターコネクト(PCI)エクスプレス・ネットワークにおける損失されたポステッド・ライト・パケットおよび順序の狂ったポステッド・ライト・パケットの検出

【課題】ペリフェラル・コンポーネント・インターコネクト(PCI)エクスプレス・ネットワークにおいて損失されたポステッド・ライト・パケットおよび順序の狂ったポステッド・ライト・パケットを検出する。

【解決手段】ペリフェラル・コンポーネント・インターコネクト・エクスプレス(PCIe)ネットワークにおいてパケットを処理する装置、方法およびコンピュータ・プログラムは、受信側デバイスにおいてPCIeポステッド・ライト・パケットを受信する手段を提供し、PCIeポステッド・ライト・パケットは、受信されるタグ識別子と、リクエスト側デバイスを識別するリクエスト側デバイス識別子とを含む。期待されるタグ識別子が、リクエスト側デバイスに関して判断される。受信されるタグ識別子が、期待されるタグ識別子と比較される。受信されるタグ識別子が期待されるタグ識別子と一致しなければ、エラー・フラグがセットされる。

(もっと読む)

CPUインターフェース回路及びCPUインターフェース回路の異常状態からの復帰方法

【課題】 CPUインターフェース回路内にステートアクセス数を保持したレジスタを持ち、レジスタの設定値によりCPUからの複数のステートアクセスに対応したCPUインターフェース回路において、動作途中にステートアクセス数を保持したレジスタ値が変化してしまった場合、速やかに所望のステートアクセスに復帰することを課題とする。

【解決手段】 現在のステートアクセス数を保持するレジスタと現在より前のステートアクセス数を保持するレジスタを持ち、比較回路により現在と現在より前のレジスタ値を比較し変化を検知したら、CPUに対して割込み信号を発生する。CPUは割込み信号を検知したらCPUインターフェースに対して復帰処理を行う。

(もっと読む)

インターフェース回路

【課題】データ量の増加を抑制しつつ、データに誤りがあるか否かを検出することが可能なインターフェース回路を提供する。

【解決手段】インターフェース回路は、記憶回路にアクセスするべく一方の論理レベルまたは他方の論理レベルに変化するアクセス信号が入力され、アクセス信号を記憶回路に出力する第1出力回路と、第1出力回路から出力されたアクセス信号を出力する第2出力回路と、アクセス信号の少なくとも一部が第1出力回路に入力された後、第1出力回路に入力されるアクセス信号の論理レベル及び第2出力回路から出力されるアクセス信号の論理レベルの変化の回数を比較し、第1出力回路に入力されるアクセス信号に基づく所定のアクセスがされたか否かを示す比較信号を出力する比較回路と、を備えることを特徴とする。

(もっと読む)

冗長化制御装置

【課題】 冗長化されたコントローラ間の診断通信に失敗が発生した場合に、故障箇所を特定することを可能とする冗長化制御制御装置を実現する。

【解決手段】 第1コントローラ及び第2コントローラが、シリアルバスを介して相互に通信すると共に、通信バスを介して上位装置と通信し、各コントローラは診断フレームを自側より相手側コントローラに送信するトランシーバーと相手側から送信された診断フレームを受信するレシーバーを具備する冗長化制御装置において、

前記第1コントローラ及び第2コントローラは、

自側トランシーバーの送信データのフィードバックチェック手段と、

相手側からの受信データに対する1ビット誤りまたは多ビット誤りを検出する、誤り検出手段と、

を備える。

(もっと読む)

シリアルバスシステム、ハングアップスレーブ特定方法及びハングアップスレーブ特定プログラム

【課題】ハングアップしたバススレーブ装置を特定することが可能なシリアルバスシステムを提供する。

【解決手段】シリアルデータ線2と、シリアルクロック線3と、それらに接続されるプルアップ抵抗4,5と、バスマスタ装置12と、バススレーブ装置141〜144とを備えたシリアルバスシステム10において、シリアルデータ線2とバススレーブ装置141〜144との間に駆動抵抗161〜164を接続し、検出用電源20を設ける。駆動抵抗161〜164の抵抗値は互いに異なる。検出用電源20は、バスマスタ装置12で検出されたシリアルデータ線2の電圧が0V近くになったとき、その電圧を引き上げる。バスマスタ装置12は、検出された電圧に基づいてハングアップしたバススレーブ装置を特定しかつリセットする。

(もっと読む)

集積回路

【課題】集積回路の実使用現場で発生するソフトウエアでは検知不可能な不具合を回避することを目的とする。

【解決手段】LSIの集積回路において、バス等の任意の一つ以上の信号の状態をモニタする監視手段と、プログラマブルに任意の値が設定可能な記憶手段と、前記モニタした信号の状態と前記記憶手段に設定した値を比較する比較手段と、比較判定手段の結果に応じて値が変わる信号を出力する出力手段から構成された不具合検出手段を備えたことを特徴とする集積回路等、を提供する。

(もっと読む)

1 - 20 / 87

[ Back to top ]