Fターム[5B125BA02]の内容

リードオンリーメモリ (43,397) | メモリ種別 (5,638) | EEPROM、フラッシュ (3,956) | スタックゲート型 (1,665)

Fターム[5B125BA02]に分類される特許

1 - 20 / 1,665

メモリシステム及びそれのブロック複写方法

暗号化演算装置を搭載する不揮発性半導体記憶装置

ホスト装置、装置、システム

不揮発性半導体メモリおよびそのデータの読出し方法

半導体記憶装置

半導体記憶装置

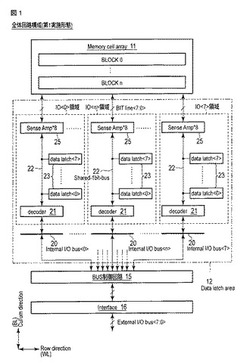

【課題】微細化に対して有利な半導体記憶装置を提供する。

【解決手段】実施形態によれば、半導体記憶装置は、複数のメモリセルが配置されるメモリセルアレイ11と、前記複数のメモリセルのデータをラッチし、前記メモリセルアレイのデータの入力または出力(I/O)ごとに分割して配置される複数のアドレス領域(IO<0>領域〜IO<7>領域)と、前記複数のアドレス領域に対応して配置され、それぞれが前記複数のアドレス領域と電気的に直列に接続される内部バス配線20と、前記内部バス配線のデータ転送を制御する制御回路15とを具備する。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置の回路面積を削減する。

【解決手段】半導体記憶装置10は、複数のメモリセルを有する第1のブロックを含むメモリセルアレイ11−1と、複数のメモリセルを有する第2のブロックを含むメモリセルアレイ11−2と、メモリセルアレイ11−1及び11−2に配設された複数のワード線と、複数のワード線のそれぞれに電圧を転送する複数の転送ゲートSWを有するロウデコーダ12とを含む。第1のブロックに配設された複数のワード線は、第1及び第2のグループを有し、第2のブロックに配設された複数のワード線は、第3及び第4のグループを有する。上記第1及び第3のグループは、転送ゲートSWを共有する。

(もっと読む)

電圧生成回路

【課題】回路面積を低減させることのできる電圧生成回路を提供する。

【解決手段】一の実施の形態に係る電圧生成回路は、第1の電圧値の第1電圧を発生させる第1の昇圧回路と、第2の電圧値の第2電圧を発生させる複数の第2の昇圧回路を含む第2昇圧回路群とを有する。複数の第2の昇圧回路は、第1の状態から第2の状態に移行する際に互いに直列に接続され第1昇圧回路とともに第1電圧を発生可能に構成されている。

(もっと読む)

半導体装置

【課題】メモリセルの動作を従来よりも高速化できる半導体装置を提供する。

【解決手段】フローティングゲートFGとコントロールゲートCG、第1導電型ソース13s及び第1導電型ドレイン13dを有する第1導電型MOSトランジスタ13と、前記フローティングゲートFGと前記コントロールゲートCG、第2導電型ソース14s及び第2導電型ドレイン14dを有する第2導電型MOSトランジスタ14と、前記第1導電型ドレイン13d及び前記第2導電型ドレイン14dに接続される第1のソース/ドレイン11bと、第2のソース/ドレイン11aと、ゲートを有する選択トランジスタ11と、前記第1導電型ソースに接続される第1電源線VpLと、前記第2導電型ソースに接続される第2電源線VnLと、前記選択トランジスタ11の第2のソース/ドレイン11aに接続されるビット線BLと、前記選択トランジスタ11のゲートに接続されるワード線WLと、を有する。

(もっと読む)

不揮発性メモリ装置及び不揮発性メモリ装置を制御するコントローラの動作方法

【課題】向上された動作速度を有する不揮発性メモリ装置及び不揮発性メモリ装置を制御するコントローラの動作方法を提供する。

【解決手段】本発明の不揮発性メモリ装置は、データのプログラム、読出し又は消去を遂行する第1プレーン、データのプログラム、読出し又は消去を遂行する第2プレーン、及び第1プレーン又は第2プレーンから共通バスを通じて伝送されるデータを外部へ出力し、外部から受信されるデータを、共通バスを通じて第1プレーン又は第2プレーンへ伝送するデータ入出力回路を含む。第1プレーンでプログラム、読出し又は消去が遂行される時、データ入出力回路は共通バスを通じて第2プレーンとデータを交換する。

(もっと読む)

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

半導体記憶装置

【課題】高速動作が可能な半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、制御可能な閾値に基づいてデータを記憶し、データの消去状態において正の閾値分布を有し、制御電極を有する複数のメモリセルを含む。複数のワード線(WL)は、複数のメモリセルの制御電極と選択的に電気的に接続され、メモリセルへのデータの書き込みに先立って特定の電位へと充電される。電圧生成回路(9)は、出力において電圧を出力し、出力の電位を放電する放電経路(DP2)を含む。接続回路(WF)は、電圧生成回路と特定のワード線とに選択的に接続され、接続されているワード線を特定の電位を供給する供給ノードに選択的に接続する。

(もっと読む)

不揮発性半導体記憶装置

【課題】低消費電流で正確なデータ読出を行なうことが可能な不揮発性半導体記憶装置を提供する。

【解決手段】このフラッシュメモリでは、4つのメモリマットMAT0〜MAT3の各々にセンスアンプSA0〜SAmを設け、通常の読出動作モードでは、全メモリマットMAT0〜MAT3のセンスアンプSA0〜SAmに参照電圧VRを供給し、低速読出モードでは、選択されたメモリマットMATのセンスアンプSA0〜SAmのみに参照電圧VRを供給する。したがって、低消費電力で正確なデータ読出を行なうことができる。

(もっと読む)

メモリシステム及びそれの動作方法

【課題】動作速度及び電力消耗を減らすことができるメモリシステム及びそれの動作方法が提供される。

【解決手段】本発明の実施形態によるメモリシステムは不揮発性メモリ装置と、前記不揮発性メモリ装置を制御するように構成されたメモリ制御器と、を含み、前記メモリ制御器は前記不揮発性メモリ装置から読み出されたデータのエラーの位置情報を含むエラーフラッグ情報を前記不揮発性メモリ装置へ提供する。

(もっと読む)

半導体記憶装置

【課題】動作の安定性を向上できる半導体記憶装置を提供する。

【解決手段】実施形態に係る半導体記憶装置は、複数のメモリセルと、複数のワード線と、複数のビット線と、複数の選択トランジスタと、配線層と、を備える。複数のメモリセルは、第1方向及び第1方向と直交する第2方向にそれぞれ配置される。複数のワード線は、それぞれ第1方向に延在して設けられる。複数のビット線は、それぞれ第2方向に延在し、第1方向及び第2方向と直交する第3方向に複数のワード線と離間して設けられる。複数の選択トランジスタは、複数のストリングにそれぞれ設けられる。配線層は、選択トランジスタのソースと同電位に設けられる。配線層は、第3方向にみて複数のワード線とそれぞれ重なる複数の第1重複部分を有する。配線層のパターンが繰り返される単位領域において、複数の第1重複部分のそれぞれの面積は同じである。

(もっと読む)

不揮発性半導体記憶装置

【課題】読出動作の精度を向上させた不揮発性半導体記憶装置を提供する。

【解決手段】メモリストリングは、半導体基板の上方に設けられ、複数のメモリセルを含む。制御回路は、複数のメモリセルのうち、選択メモリセルに保持されたデータを読み出す読出動作を実行する。メモリストリングは、半導体層、電荷蓄積層、及び導電層を有する。半導体層は、半導体基板に対して垂直方向に延びメモリセルのボディとして機能する。電荷蓄積層は、半導体層の側面に設けられ、電荷を蓄積可能とされる。導電層は、半導体層と共に電荷蓄積層を挟むよう設けられメモリセルのゲートとして機能する。制御回路は、読出動作の実行前に、選択メモリセル及び非選択メモリセルを導通状態としてメモリストリングの一端から他端へと電流を流すリフレッシュ動作を実行する。

(もっと読む)

不揮発性メモリ装置、不揮発性メモリ装置のプログラム方法、不揮発性メモリ装置を含むメモリシステム

【課題】向上された信頼性を有する不揮発性メモリ装置のプログラム方法が提供される。

【解決手段】本発明のプログラム方法は、第1メモリセルトランジスターの閾値電圧がプログラム状態から移動する傾向を判別する段階と、判別結果に応答して、複数の検証電圧の中で第1検証電圧を選択する段階と、第1メモリセルトランジスターの閾値電圧が変化するように第1メモリセルトランジスターをプログラムする段階と、で構成される。プログラムする段階は第1メモリセルトランジスターの閾値電圧が十分に変化されたかを第1検証電圧を利用して検証する段階を含む。判別する段階は第1メモリセルトランジスターの閾値電圧の第1範囲からの変化を判別する段階を含む。

(もっと読む)

半導体記憶装置

【課題】インタリーブ動作を実行可能に構成され且つLMアドレススキャン動作を実行する半導体記憶装置における消費電力の削減、及び動作の高速化を図る。

【解決手段】複数のカラムのうちの少なくとも1つは、複数ビットのデータの書き込み動作の進行状況を示すLMフラグデータを記憶するためのLMカラムである。カラム制御回路の各々は、対応するメモリコアにLMカラムが存在するか否かを確認するためのLMアドレススキャン動作をする。そのLMアドレススキャン動作の結果をレジスタに格納し、その後の各種動作においては、前記データラッチ回路に保持されたデータが第1のデータである場合、そのメモリコアにおいて前記LMカラムからLMフラグデータを読み出す動作を実行する一方、前記レジスタに保持されたデータが第2のデータである場合、そのメモリコアにおいて前記LMカラムからLMフラグデータを読み出す動作を実行しない。

(もっと読む)

不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置においてリーク電流を抑制し読み出し動作を正確に実行する。

【解決手段】この不揮発性半導体記憶装置は、1導電型の半導体層と、第1方向に並ぶように前記第1半導体層上に形成される複数の第2導電型のウエルを有する。この複数のウエルの各々に、メモリブロックが配列される。複数のメモリブロックは、それぞれ複数のメモリセル及び選択トランジスタを直列接続してなる複数のNANDセルユニットを配列してなる。複数のワード線が、1つのメモリブロック中の複数のNANDセルユニットに共通に接続される。複数のビット線は、第1方向に延びて複数のメモリブロックに存在するNANDセルユニットの一端に接続される。ソース線は、NANDセルユニットの他端に接続される。ウエルドライバは、第1電圧、又は第1電圧よりも大きい第2電圧を選択的に複数の前記ウエルの各々に与える制御を行う。

(もっと読む)

不揮発性半導体記憶装置

【課題】閾値電圧分布の広がりを抑制した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置は、メモリセル、ビット線、ワード線、及び制御回路を有する。メモリセルは、電気的にデータを書き換え可能に構成される。ビット線は、メモリセルの電流経路の一端に電気的に接続される。ワード線は、ビット線と交差する方向に配列されたメモリセルに共通に接続される。制御回路は、ワード線に書込電圧を印加してデータを書き込むべきメモリセルの閾値電圧を所定の閾値電圧以上になるまで移動させる書込動作を実行する。制御回路は、書込動作時に、ワード線に逐次上昇する書込電圧を印加しつつ、書き込むべきメモリセルの閾値電圧と書込電圧の印加回数との関係に基づいてビット線に印加する電圧を逐次変更する。

(もっと読む)

1 - 20 / 1,665

[ Back to top ]