Fターム[5B125EB02]の内容

リードオンリーメモリ (43,397) | EEPROMセルへの電荷注入、放出構成 (1,604) | アバランシェ注入 (265)

Fターム[5B125EB02]に分類される特許

1 - 20 / 265

不揮発性半導体メモリ素子、および不揮発性半導体メモリ装置

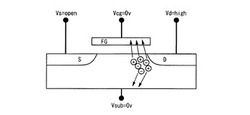

【課題】フローティングゲートへの電荷の蓄積と消去を容易に行え、またフローティングゲートの電荷を消去する場合にメモリセルの閾値を容易に制御できる、不揮発性半導体メモリ素子を提供する。

【解決手段】フローティングゲートへの電荷の蓄積時に、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットエレクトロンを半導体基板中に発生させ、フローティングゲートに電荷を注入する。また、フローティングゲートの電荷の消去時には、フローティングゲートとドレイン(またはソース)間に電圧を印加し、バンド・バンド間によるホットホールを発生させ、該ホットホールにより蓄積された電荷を消去する。また、フローティングゲートの電荷の消去時には、メモリセルのコントロールゲートとソース間の閾値が所望の値になるように制御しながら、電荷を消去する。

(もっと読む)

不揮発性メモリーセル

【課題】種々の回路ブロックを単一の集積回路(IC)に集約するために、不揮発性メモリーブロックをロジック機能ブロックにまとめる。

【解決手段】結合素子と第一のセレクトトランジスターを有している。結合素子は第一の伝導領域において形成されている。第一のセレクトトランジスターは、第一の浮遊ゲートトランジスターおよび第二のセレクトトランジスターに直列的に接続されており、それらは全て第二の伝導領域に形成されている。結合素子の電極および第一の浮遊ゲートトランジスターのゲートは、モノリシックに形成された浮遊ゲートである。第二の伝導領域は第一の伝導領域と第三の伝導領域の間に形成され、第一の伝導領域、第二の伝導領域、および第三の伝導領域は、ウェルである。

(もっと読む)

メモリのプログラミング方法及びメモリアレイ

【課題】クリティカル・ディメンションの変動に鈍感であり且つ高速なメモリプログラミング方法等を提供する。

【解決手段】メモリの複数のメモリセルの夫々は、ウェルと、ソース及びドレイン領域と、記憶レイヤと、ゲートとを有する。メモリセルはマトリクス状である。同じ列ドレイン領域は同じビットラインへ接続し、同じ行ゲートは同じワードラインへ接続し、同じ列ソース領域は同じソースラインへ接続する。メモリは、いずれかのメモリセルへ電気的に接続されたワードラインへ第1の電圧を印加し、そのメモリセルへ電気的に接続されたビットラインへ少なくともプログラミング閾値だけ第1の電圧と異なる第2の電圧を印加し、そのメモリセルへ電気的に接続されたソースラインへ少なくともプログラミング閾値だけ第1の電圧と異なる第3の電圧を印加し、複数のメモリセルへ基板電圧を印加することによって、プログラミングされる。

(もっと読む)

半導体記憶装置及び半導体記憶素子

【課題】素子の面積を増大させることなく、かつ、コントロールゲート電圧を制御しなくとも、低電圧で書き込み量を大幅に増やすことが可能であり、また、安定して十分な書き込みを行うことが可能である不揮発性半導体装置を提供すること。

【解決手段】ドレインアバランシェホットエレクトロンにより書き込みを行う半導体記憶素子であって、第1導電型の半導体基板に形成された第2導電型の第1の半導体層と、前記第1の半導体層上に絶縁膜を介して設けられたフローティングゲートと、前記フローティングゲート下部の前記第1の半導体層の表面に形成されたチャネル領域と、前記チャネル領域に接触するように前記第1の半導体層上に設けられた第1導電型のソース領域及びドレイン領域とを有するMOSトランジスタであって、前記チャネル領域が2種類以上のキャリア濃度の分布をもつ半導体記憶素子とした。

(もっと読む)

半導体装置

【課題】外部からの回路構成情報の呼び出し処理を不要にして、電源投入後すぐに動作できる半導体装置を提供する。

【解決手段】半導体装置は、ワード線とデータ線とが交差する位置にそれぞれ配置された複数の不揮発メモリセル1100を有する。不揮発メモリセル1100の出力にはインバータ回路が接続され、さらに不揮発メモリセルの出力とWBL(Write Bit Line)との間に第1トランジスタM1と、第1トランジスタよりも抵抗が低い第2トランジスタM2とを備える。インバータ回路の出力とRBL(Read Bit Line)との間にはトランスファーゲートを備える。

(もっと読む)

メモリ回路

【課題】電源投入時における誤書き込みが発生しにくいメモリ回路を提供する。

【解決手段】メモリ回路10は、書き込み時のみにソース・ドレイン間に電圧を印加されて書き込まれる、書き込み用のPチャネル型不揮発性メモリ素子15と、コントロールゲート及びフローティングゲートがPチャネル型不揮発性メモリ素子15のコントロールゲート及びフローティングゲートとそれぞれ共通にされ、読み出し時のみにソース・ドレイン間に電圧を印加されて読み出される、読み出し用のNチャネル型不揮発性メモリ素子16と、を備える。

(もっと読む)

バイト、ページおよびブロックに書き込むことができ、セルアレイ中で干渉を受けず分割が良好な特性を備え、新規のデコーダ設計とレイアウトの整合ユニットと技術を使用する単体式複合型不揮発メモリ

【課題】

バイト、ページおよびブロックで書き込むことができる新単体式複合型不揮発メモリを提供する。

【解決手段】

不揮発メモリアレイは、シングルトランジスタフラッシュメモリセルおよびダブルトランジスタEEPROMメモリセルを備え、同じ基板上に整合することができ、該不揮発メモリセルは低いカップリング係数の浮遊ゲートを備えて、メモリセル体積を減少でき、該浮遊ゲートをトンネル絶縁層の上に配置し、該浮遊ゲートは該ソース領域の辺縁および該ドレイン領域の辺縁に揃って、且つ該ソース領域辺縁および該ドレイン領域辺縁の幅に画定される幅を備え、該浮遊ゲートと該制御ゲートは50%より小さい相対的に小さなカップリング係数を備えて、該不揮発メモリセルを縮小できるようにし、該不揮発メモリセルのプログラムはチャネル熱電子方式で達成し、消去は高電圧でFNトンネル方式で達成する。

(もっと読む)

不揮発プログラマブルロジックスイッチ

【課題】 誤動作を防ぐとともに、サイズが小さい不揮発プログラマブルロジックスイッチを提供すること。

【解決手段】 本発明の実施形態による不揮発プログラマブルロジックスイッチは、制御ゲートが第1の配線に接続され、第1のソースドレイン端が第2の配線に接続され、電荷を蓄積する膜を有する第1のメモリセルトランジスタと、制御ゲートが前記第1の配線に接続され、第3のソースドレイン端が前記第1のメモリセルトランジスタの第2のソースドレイン端に接続され、第4のソースドレイン端が第3の配線に接続され、電荷を蓄積する膜を有する第2のメモリセルトランジスタと、前記第1のメモリセルトランジスタの前記第2のソースドレイン端と前記第2のメモリセルトランジスタの前記第3のソースドレイン端にゲート電極が接続されたパストランジスタと、前記パストランジスタのウェルに基板電圧を印加する第1の基板電極を有する。

(もっと読む)

半導体記憶装置へのデータの書込み方法及び半導体記憶装置

【課題】半導体記憶装置のメモリセルの参照セルとなる副記憶領域の読出し電流の変動を抑制して、メモリセルの読出し電流の判定時における誤判定を低減することができる半導体記憶装置へのデータの書込み方法及び半導体記憶装置を提供する。

【解決手段】メモリセルの第1不純物領域及び第2不純物領域に印加される電圧の大小関係が互いに異なる2つのデータ書込みステップによってメモリセルにデータの書込みをなす。

(もっと読む)

データ書き込み方法及び不揮発性半導体メモリ装置

【課題】高い読出し精度が得られるデータの書き込みを行う不揮発性半導体メモリ装置を提供する。

【解決手段】書き込み前に、メモリセル各々のドレイン側及びソース側の電荷蓄積部に各々対応してドレイン端子とソース端子との間に流れる電流値を第1初期電流値及び第2初期電流値として測定する第1電流測定ステップと、メモリセル毎に第1初期電流値と第2初期電流値とを大小比較する比較ステップと、第1初期電流値が第2初期電流値より大であるという比較ステップの比較結果が得られたとき第1初期電流値に対応したソース側の電荷蓄積部に電荷を注入して第1初期電流値を第2初期電流値に近づける第1電荷注入ステップと、第2初期電流値が第1初期電流値より大であるという比較ステップの比較結果が得られたとき第2初期電流値に対応したドレイン側の電荷蓄積部に電荷を注入して第2初期電流値を第1初期電流値に近づける第2電荷注入ステップと、を備える。

(もっと読む)

不揮発性半導体記憶装置及びその駆動方法

【課題】選択トランジスタの占有面積を縮小して、セルの配置効率を向上できるようにする。

【解決手段】ゲート電極が列方向に延伸する第1の選択ワード線23と接続され、ソースが第1の副ビット線20と接続され、ドレインが行方向に延伸する第1の主ビット線22と接続された第1の選択トランジスタ21と、ゲート電極が列方向に延伸する第2の選択ワード線33と接続され、ソースが第2の副ビット線30と接続され、ドレインが行方向に延伸する第2の主ビット線32と接続された第2の選択トランジスタ31とを有している。第1の副ビット線20は、第1の選択トランジスタ21により、同時に消去される複数のメモリセル1ごとに電気的に分離して制御される。一方、第2の副ビット線30は、第2の選択トランジスタ31により、別々に消去される複数のメモリセル1に共通に接続されている。

(もっと読む)

不揮発性半導体メモリ

【課題】データ書込み時における電流量の変化を抑制し、メモリセルへのデータ書込みを高精度に行うことができる不揮発性半導体メモリを提供する。

【解決手段】複数のメモリセルと、複数のメモリセルに接続されたワード線と、複数のメモリセルの各々に接続されたビット線と、を含み、ビット線から少なくとも2つを選択し、選択されたビット線に接続されたメモリセルに対して、電源供給ラインから同時に電流を供給してデータを書込む不揮発性半導体メモリであって、複数のメモリセルの各々に蓄積された電荷量を測定する電荷量測定部と、ビット線の各々に接続された電流路切替回路と、を有し、選択されたビット線に接続された電流路切替回路は、電荷量測定部による電荷量の測定値に応じて、メモリセル又は所定端子のいずれかに対して選択的に電源供給ラインから電流を供給すること。

(もっと読む)

不揮発性半導体記憶装置、不揮発性半導体記憶装置の動作方法

【課題】チップ面積の増大を抑制しつつ、安定的に動作するスプリットゲート型不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体メモリのベリファイステップを以下の手順で実行する。(a)通常読み出し動作のワードゲート電圧よりも低いベリファイ電圧を、ワードゲートに供給する。(b)通常読み出し動作のコントロールゲート電圧を、コントロールゲートに供給する。(c)そのベリファイ電圧とそのコントロールゲート電圧とに応じて流れる電流が、通常読み出し動作のときの参照電流に一致するか否かを判定する。TwinMONOSセルの消去ベリファイ時に、ワードゲートの電圧を低くすることで、コントロールゲートの負電圧を利用せずに消去ベリファイを可能にする。

(もっと読む)

半導体メモリ

【課題】 低消費電力、高集積化を図ることができる不揮発性メモリ装置を提供する。

【解決手段】 行列状に配置されたメモリセルを含み、メモリセルのゲートにワード線が接続され、ドレインにローカルビット線LBLdが接続され、ソースに第1または第2のローカルビット線LBLSが接続される。メモリセルMC12、MC19の読み出しを行うとき、ビット線選択トランジスタTRd1、TRd5によって選択されたローカルビット線LBLd1、LBLd5に読出し電圧Vreadを印加し、第1の選択トランジスタTRs0、TRs2によって選択された第1のローカルビット線LBLs0、LBLs2に0vを印加する。隣接するメモリセルMC13、MC18のソースは、第2の選択トランジスタTRs4、TRs5によって一定電位にクランプされ、隣接するメモリセルMC11、MC1Aのソースは、ビット線選択トランジスタTRd0、TRd5によって0vに印加される。

(もっと読む)

不揮発性半導体メモリ、及び不揮発性半導体メモリへの書込み方法

【課題】不揮発性半導体メモリの周辺回路を小さくし、集積回路の縮小化に寄与する。

【解決手段】p型基板10に形成され、ソース線430と接続するn型拡散層50と、p型基板10上に設けられ、ワード線400と接続するワード電極200と、p型基板10とワード電極200の間に設けられたワード絶縁層と、n型拡散層50上、及びワード電極200の側壁に設けられたトンネル絶縁層と、トンネル絶縁層上に設けられた電荷蓄積層と、電荷蓄積層上に設けられたコントロール絶縁層と、コントロール絶縁層上に設けられ、コントロール線420と接続するコントロール電極300と、を備え、制御部は、メモリ素子600に書込みを行うときに、ソース線430に正電圧を印加し、ワード線400に負電圧を印加し、かつコントロール線420に正電圧を印加する不揮発性半導体メモリ。

(もっと読む)

不揮発性半導体記憶装置およびその読み書き制御方法

【課題】 ソース−ドレイン間の電位差を小さくしてメモリセルのゲート長を短くすることができるようにするとともに、メモリセルに対してビットデータの書き込み(プログラム)を行った後、そのベリファイを行う際に比較的大きな電荷の充放電が生じるという問題を解消してデータの読み書きの高速化および低消費電力化を図った不揮発性半導体記憶装置およびその読み書き制御方法を提供する。

【解決手段】 プログラム動作時のt7で、選択メモリセルのセルウェルに4V、ドレインに0V、ゲートに10V、ソースにVCCをそれぞれ印加し、続くベリファイ時のt13において、セルウェルの電圧を4Vにしたまま、選択ワード線WLを−5Vにする。また、このときWLは通常の読み出し時の電圧より絶対値が高い電圧(−5V)に設定しておく。

(もっと読む)

チャネル熱電子注入プログラミング方法及び関連する装置

【課題】 本発明は、チャネル熱電子注入プログラミング方法及び関連する装置を提供する。

【解決手段】 プログラミング電流を低減し、信頼性を向上させる不揮発性メモリ素子は、メモリ・セル・アレイ、書き込み回路、及び検証回路を有する。メモリ・セル・アレイは、メモリ・セル・アレイのビット線とワード線のマトリックスの交点に配置されたメモリ・セルを有する。書き込み回路は、プログラミングのために各ワード線に複数の可変パルスを提供する。複数の可変パルスは、プログラミング動作中の伝導電流を低減しながら、ゲート注入電流をほぼ最大値に維持するため所定の大きさを有している。検証回路は、プログラミング動作中の伝導電流の変化を検知し、該検知されたプログラミング動作中の伝導電流が所定値に達した場合に、前記プログラミング動作を停止する。

(もっと読む)

半導体メモリ

【課題】 低消費電力、高集積化を図ることができる不揮発性メモリ装置を提供する。

【解決手段】 行列状に配置されたメモリセルを含み、メモリセルのゲートにワード線が接続され、ドレインにローカルビット線LBLdが接続され、ソースに第1または第2のローカルビット線LBLSが接続される。メモリセルMC2の読み出しを行うとき、ビット線選択トランジスタTRd1によって選択されたローカルビット線LBLd1に読出し電圧Vreadを印加し、第1の選択トランジスタTRs0によって選択された第1のローカルビット線LBLs0に0vを印加する。隣接するメモリセルMC3のソースは、第2の選択トランジスタTRs4によって一定電位にクランプされ、隣接するメモリセルMC1のソースは、ビット線選択トランジスタTRd0によって0vに印加される。

(もっと読む)

不揮発性記憶装置、集積回路装置及び電子機器

【課題】過消去ビットの発生を抑制してエンデュランス特性等を向上させることができる不揮発性記憶装置、集積回路装置及び電子機器等を提供すること。

【解決手段】不揮発性記憶装置は、電気的に書き換え及び消去可能な複数の不揮発性メモリーセルM11〜M44を有するメモリーセルアレイと、複数の不揮発性メモリーセルのうちの消去対象メモリーセルに対する消去動作の制御を行う消去制御回路ERCNとを含む。消去制御回路ERCNは、消去対象メモリーセルが多い場合には、消去対象メモリーセルに対応するビット線BL1〜BL4がフローティング状態に設定される第1の消去動作制御を行う。消去対象メモリーセルが少ない場合には、消去対象メモリーセルに対応するビット線BL1〜BL4が低電位電源電圧VSSに設定される第2の消去動作制御を行う。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の動作方法

【課題】不揮発性半導体メモリの保持特性の悪化を抑制しつつ、消去動作に要する時間を短縮する。

【解決手段】(a)メモリセルアレイのデータ消去対象領域に消去パルスを印加するステップと、(b)データ消去対象領域に配置されたメモリセルの閾値電圧が消去レベルに達したか否かを判定するステップと、(c)ベリファイ結果に基づいて、新たな消去パルスを印加するか、待機状態に移行するかを決定するステップとを具備する方法で、不揮発性半導体メモリの消去動作を実行する。(b)ステップは、消去パルスの印加が行われた印加期間が経過した後、待機状態に移行する前に閾値電圧が消去レベルに達したか否かを判定する。(c)ステップは、閾値電圧が消去レベルに達していないとき、データ消去対象領域に新たな消去パルスを印加するステップと、閾値電圧が消去レベルに達しているとき、新たな消去パルスの印加を禁止するステップとを含む。

(もっと読む)

1 - 20 / 265

[ Back to top ]