Fターム[5B125EF04]の内容

リードオンリーメモリ (43,397) | その他の周辺回路 (1,179) | 1ビットデータと多ビットデータの変換回路 (42)

Fターム[5B125EF04]に分類される特許

1 - 20 / 42

不揮発性メモリ素子を含む多値論理装置

【課題】不揮発性メモリ素子を含む多値論理装置を提供する。

【解決手段】信頼性が改善された多値論理装置に係り、マルチレベル信号を、複数の部分信号に変換するように構成された変換ユニット、及び複数の部分信号をそれぞれ保存する複数の不揮発性メモリ素子を含み、不揮発性メモリ素子それぞれに保存された複数の部分信号それぞれのビット数は、マルチレベル信号のビット数より少ないことを特徴とする多値論理装置である。

(もっと読む)

メモリシステム及びそれの動作方法

【課題】動作速度及び電力消耗を減らすことができるメモリシステム及びそれの動作方法が提供される。

【解決手段】本発明の実施形態によるメモリシステムは不揮発性メモリ装置と、前記不揮発性メモリ装置を制御するように構成されたメモリ制御器と、を含み、前記メモリ制御器は前記不揮発性メモリ装置から読み出されたデータのエラーの位置情報を含むエラーフラッグ情報を前記不揮発性メモリ装置へ提供する。

(もっと読む)

半導体記憶装置及びその制御方法

【課題】カラムブロックのデータラッチに対するデータの高速転送を可能にする。

【解決手段】半導体記憶装置1は、メモリセルアレイ2と、データバスDBと、転送制御部TC0〜TC2と、複数のカラムブロックC(0+4×i)〜C(3+4×i)と、カラムセレクタCSとを含む。カラムブロックおよびカラムセレクタはメモリセルアレイより下に形成される。データバスDBは複数のステージS0〜S3に分割される。転送制御部は複数のステージのそれぞれにデータが割り当てられるようにデータをシリアル転送する。カラムブロックは選択された場合にデータを一次記憶する。カラムセレクタCSはカラムブロックの中から、ステージごとにいずれかのカラムブロックを選択し、ステージごとに選択されたカラムブロックとの間でデータをパラレル転送する。データバスDBはカラムブロックの配列方向の一方の端側から他方の端側へ向かい、他方の端側で折り返す。

(もっと読む)

ページ内・ページ間オンチップデータ擬似ランダム化のための不揮発性メモリおよび方法

【課題】集積回路メモリチップ内の機構により、不揮発性メモリセルアレイに蓄積されるデータのスクランブリングまたはランダム化を可能にする。

【解決手段】一実施形態において、検知中のソース負荷誤差と近傍セルのフローティングゲート間結合を抑制するため、ページ内ランダム化を役立てる。ページ単位ランダム化は、特定のデータパターンが繰り返し長期間にわたり蓄積されることから生じるプログラムディスターブ、ユーザリードディスターブ、フローティングゲート間結合を抑えるのに役立つ。別の実施形態では、ページ内ランダム化とページ単位ランダム化の両方を実施する。実施形態によってはスクランブリングまたはランダム化が予め決定されるか、あるいは符号生成擬似ランダム化となるか、あるいはユーザ主導ランダム化となる。これらの機構は、集積回路メモリチップの限られたリソースおよびバジェットの中で達成される。

(もっと読む)

半導体記憶装置

【課題】チップ面積を縮小する。

【解決手段】半導体記憶装置は、メモリ10と、メモリ10との間のデータ転送を行い、第1のビット幅でデータを転送する第1のモードと、第2のビット幅でデータを転送する第2のモードとを有するデータ転送部17とを含む。データ転送部17は、メモリ10から読み出された第1のデータを保持する第1のラッチ回路70と、第1のモードにおいて、第1のデータのうち第1のビット幅を有する第2のデータを保持し、第2のモードにおいて、第1のデータのうち第2のビット幅を有する第3のデータを保持する第2のラッチ回路71と、第1のラッチ回路70と第2のラッチ回路71とを接続し、第1及び第2のモードで共有されるデータバスとを含む。

(もっと読む)

多値不揮発性半導体メモリシステム

【課題】コントローラから不揮発性半導体メモリへのデータ転送時間を短縮する。

【解決手段】実施形態に係わるメモリシステムは、x(xは3以上の整数)ビットを記憶する複数のメモリセルを有し、2x個の閾値分布にビット割り付けが行われるメモリセルアレイ11を備える不揮発性半導体メモリ1と、書き込み時に不揮発性半導体メモリ1の動作を制御するコントローラ2とを備える。コントローラ2は、第1、第2及び第3ステップにより書き込みを実行し、第1ステップにより2y個(yは整数、かつ、y<x)の閾値分布を生成し、第2及び第3ステップにより2x個の閾値分布を生成し、第1ステップ時にxビットに基づいて2y個の閾値分布を生成するためのyビットを生成するデータ変換回路22を備え、第1ステップ時にyビットを不揮発性半導体メモリ1に転送する。

(もっと読む)

半導体記憶装置

【課題】 閾値レベルに対応した読み出し電圧を発生するためのパラメータの数を大幅に削減することが困難であった。

【解決手段】 半導体記憶装置は、メモリセルアレイと、制御回路とを含んでいる。メモリセルアレイは、ワード線、及びビット線に接続された複数のメモリセルがマトリックス状に配置されている。制御回路はワード線、及びビット線の電位を制御する。制御回路は、メモリセルからデータを読み出す読み出し動作時に、ワード線のうち選択されたワード線に隣接する非選択ワード線を立ち上げた後、選択ワード線を立ち上げる。

(もっと読む)

半導体記憶装置

【課題】 多値領域よりも少ないビットを記憶する領域の記憶容量を増大することなく、高速な書き込みが可能であるとともに、製品の寿命を延ばすことが可能な半導体記憶装置を提供する。

【解決手段】 本半導体記憶装置は、1セルにnビット(nは2以上の自然数)のデータを記憶する複数のメモリセルから構成される。複数のメモリセルの内、第1領域MLBのメモリMLCには、h(h<=n)ビットのデータが記憶され、第2領域SLBのメモリSLCには、i(i<h)ビットのデータが記憶され、第2領域SLBのメモリセルの書き換え回数が規定値に達した場合、第2領域SLBのメモリセルに書き込まず、第1領域MLBのメモリに、iビットのデータを記憶する。

(もっと読む)

フラッシュメモリ

【課題】多値技術を用いたメモリにおいて、複数ページにわたるデータを短時間に転送するフラッシュメモリを提供する。

【解決手段】フラッシュメモリは、各々がnビット(nは2以上の整数)のデータを記憶する複数のメモリセルを含むメモリセルアレイと、メモリセルのゲートに接続された複数のワード線と、メモリセルに接続された複数のビット線と、ビット線を介してメモリセルに記憶されたデータを検出するセンスアンプと、或るワード線に接続されたm個(mは2以上の整数)のメモリセルのそれぞれに格納されたnビットデータを保存するm×nビットのデータラッチと、データラッチから外部へ2ビット以上のデータを同時に転送可能な多値レベルインタフェースとを備えている。

(もっと読む)

不揮発性メモリ装置内におけるバイナリ形式で記憶されたデータの多状態形式への折り畳み

多状態不揮発性メモリにおいてデータを読み書きする技術を開示する。データはバイナリ形式でメモリに書き込まれ、メモリ上でデータレジスタに読み込まれ、レジスタ内で「折り畳まれ」、その後、多状態形式でメモリに書き直される。折り畳み動作中、単一ワード線からのバイナリデータは多状態形式に折り畳まれ、多状態形式で書き換えられるとき、別のワード線の一部分にしか書き込まれない。データが「広げられる」対応する読み出し技術も開示されている。これらの技術は、バイナリ形式で書き込むべきデータをメモリに転送する前に、最終多状態記憶を考慮に入れ、コントローラ上でデータを誤り訂正符号(ECC)と共に符号化することをさらに可能にする。このような「折り畳み」動作を可能にするレジスタ構造も示されている。一連の実施形態は、異なる読み出し/書き込みスタックのレジスタ間でデータの転送を可能にする局所内部データバスを含み、内部バスを内部データ折り畳み処理に用いることができる。  (もっと読む)

(もっと読む)

半導体メモリー装置

【課題】高速に情報を入力することを可能とする半導体メモリー装置を提供する。

【解決手段】半導体メモリー装置1は、アドレス線に入力される信号によって指定される複数のメモリセルにデータ線を介して複数のデータを入力する。高速入力処理部530が、予め定められる複数の閾値電圧で分割される複数の電圧範囲を定め、外部から入力される多値の論理信号を該電圧範囲ごとに定められた多値の論理信号に対応する複数桁の2進数に変換する。

(もっと読む)

データ記憶装置

【課題】不揮発性メモリセルに対する書き込み動作を高速化する。

【解決手段】半導体集積回路は、電気的消去及び書込み可能な不揮発性メモリセルを複数個備え、第1のしきい値電圧を持つ前記不揮発性メモリセルのしきい値電圧が第2のしきい値電圧に変化されるまで不揮発性メモリセルにパルス状電圧を与えるための制御手段を含む。このとき、前記制御手段は、前記第2のしきい値電圧を、電源電圧よりも低くかつ電源電圧の半分以上の範囲の電圧に制御する。これにより、半導体集積回路は、粗い書込みだけを書込みモードとして持つことができる。メモリセルのしきい値電圧を変化させるのに必要なパルスの数は、粗い書込みモードの方が少ないから、これによって書込み動作が高速化される。

(もっと読む)

ハイブリッドメモリ管理

シングルレベルおよびマルチレベルのメモリセルを利用するハイブリッドメモリデバイスにおけるデータ格納を管理するための、方法および装置である。論理アドレスは、実行される書き込み動作の頻度に基づいて、シングルレベルおよびマルチレベルのメモリセルの間に分散できる。メモリ内の論理アドレスに対応するデータの初期の格納は、最初に全てのデータをシングルレベルメモリへ書き込む、または、最初に全てのデータをマルチレベルメモリへ書き込むことを含む、種々の方法によって決定できる。他の方法では、ホストは、予想される使用に基づき、論理アドレスの書き込みを、シングルレベルまたはマルチレベルメモリセルへ方向付けることができる。  (もっと読む)

(もっと読む)

パイプラインメモリのための効率的な読出し、書込み方法

【課題】効率的にデータを書き込み、多状態メモリセルデータを読み出す方法および装置を提供する。

【解決手段】メモリシステムは、第1の記憶素子、データソース、第1のエレメント、第2のエレメントおよびリップルクロックを備える。上記データソースは、第1の記憶素子に格納する複数のビットを出力し、上記第1のエレメントは上記データソースから第1のビットを受け取り、さらに、第1のビットの計時も行って第2のバッファ用エレメントの中へ入れる。次いで、上記第1のエレメントは、第1のビットが第1のエレメントの中へ格納されているのとほぼ同じ間、複数のビットからなる第2のビットをデータソースから受け取る。上記リップルクロックにより、第1のエレメントと第2のエレメントへのアクセスが可能となり、これによって第1のビットと第2のビットのパイプライン化が可能となる。

(もっと読む)

不揮発性半導体記憶装置

【課題】 選択ワード線の印加電圧を制御して記憶状態を読み出す読み出し処理の高速化を図ることができる不揮発性半導体記憶装置を提供する。

【解決手段】 4以上の記憶状態を有するメモリセルトランジスタ(MTr)を備え、記憶状態の夫々が、リファレンス電流に等しいリード電流を流すときのMTrの第1電圧差が判定電圧より大きい第1記憶状態群と小さい第2記憶状態群に分類され、選択ワード線に判定電圧を印加し、センスアンプ回路によりリード電流とリファレンス電流を比較して第1比較結果を出力して、処理対象メモリセルの記憶状態が第1及び第2記憶状態群の何れに属するかを判定する第1読み出し処理と、第1比較結果に応じて設定した電圧変化方向に選択ワード線の印加電圧を単調変化させ、処理対象メモリセルの記憶状態が、第1読み出し処理で判定された記憶状態群に含まれる複数の記憶状態の何れであるかを判定する第2読み出し処理を実行する。

(もっと読む)

半導体記憶装置

【課題】2値データを格納する不揮発性メモリ装置を利用して、3値以上の多値データを記憶する多値半導体記憶装置を実現する。

【解決手段】選択ワード線に伝達される電圧(VBOOST)を分圧し、分圧電圧に従って参照セル(RCA−RCC)を導通状態に設定する。参照セルを流れる電流に従って基準電圧(VREF−VREF2)を生成し、この基準電圧を用いてメモリセルデータを検出する。

【選択図】図54  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置及びその自動テスト方法

【課題】 多値データを記憶可能なメモリセルの不良ビット検出をチップ内部で行うこと

が可能な不揮発性半導体記憶装置及びその自動テスト方法を提供する。

【解決手段】 多値データ記憶が可能なメモリセルを複数配列して構成され、複数のメモ

リセルのドレイン領域に共通接続されるビット線を有するメモリセルアレイと、複数のセ

ンスアンプを有し、各々のセンスアンプが所定の参照電位に対するビット線電位の高低を

2値データとして出力するセンスアンプ回路と、センスアンプ回路から出力された複数の

2値データに基づき、メモリセルに記憶された多値データを生成する多値化回路と、セン

スアンプ回路から出力される2値データまたは多値化回路から出力される多値データのい

ずれか一方を選択する選択回路と、2値データまたは多値データと期待値との比較判定を

行うベリファイ回路と、ベリファイ回路に保持される期待値を設定する内部制御回路と、

を具備する。

(もっと読む)

不揮発性メモリ

【課題】 回路の規模の増大を最少に抑え、かつ短時間で高精度の書込み、読み出し、消去動作を実現可能な多値記憶型不揮発性記憶装置を提供する。

【解決手段】 複数の不揮発性メモリセルを含むメモリアレイと、第1データレジスタと第2データレジスタとを有し、前記複数の不揮発性メモリセルのそれぞれは、しきい値電圧の状態に応じて2ビットのデータを格納可能であり、前記不揮発性メモリセルへデータを格納する書込動作において、前記不揮発性メモリセルに格納されるデータがビット毎に前記第1データレジスタと前記第2データレジスタに入力され、前記第1データレジスタから供給された1ビットのデータと前記第2データレジスタから供給された1ビットのデータとに基づいて変換された前記2ビットのデータが前記不揮発性メモリセルに格納されるようにした。

(もっと読む)

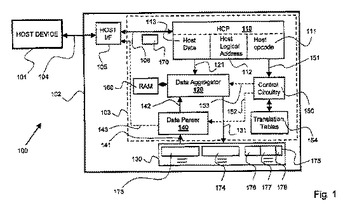

1セル当り単一ビットNANDフラッシュメモリをエミュレートする1セル当り多ビットNANDフラッシュメモリ用コントローラ

1セル当り単一ビットNANDフラッシュメモリデバイスをエミュレートする1セル当り多ビットNANDフラッシュメモリデバイスのコントローラを開示する。コントローラは、NANDホストデバイスからホストデータを受信するホストNANDインターフェイスと、ホストデータに補足データを統合することによりNANDフラッシュメモリデバイスのNANDフラッシュメモリセルアレイのデバイスページに記憶可能なデバイスデータを作成するデータ統合部とを含む。コントローラはデバイスデータを作成した後にNANDフラッシュメモリセルのデバイスページにデバイスデータを書き込む。コントローラはまた、データ読み出し操作を実行するときにデバイスデータからホストデータを解析するデータ解析部を含む。コントローラは、データ書き込み操作を実行するときに、必要に応じて、データ解析部を使用してデバイスデータから補足データを解析しデバイスデータを作成する。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置およびデータ記憶システム

【課題】大容量であって、高信頼性かつ高速動作を確保できる不揮発性半導体記憶装置およびデータ記憶システムを提供する。

【解決手段】本発明の実施の形態によるフラッシュメモリは、不揮発性メモリセルを含むメモリセルアレイMA、MBと、多値フラグ部15A、15Bと、メモリセルアレイおよび多値フラグ部に対するデータの書込み、読出し、消去を制御する制御用CPU16とを備える。多値フラグ部は、メモリセルに書込んだデータが2値データであるか多値データであるかを示す値を記憶する。多値フラグ部の値により、2値データについては、2値用の読出シーケンスで、多値データについては、多値用の読出シーケンスでデータを読出すことができる。

(もっと読む)

1 - 20 / 42

[ Back to top ]