Fターム[5B125EF09]の内容

リードオンリーメモリ (43,397) | その他の周辺回路 (1,179) | アドレス設定回路 (377) | ブロック、バンクを選択 (216)

Fターム[5B125EF09]に分類される特許

1 - 20 / 216

ホスト装置、装置、システム

不揮発性半導体記憶装置およびそのベリファイ制御方法

【課題】ベリファイに要する時間の短縮を図る。

【解決手段】ワード線WLとローカルビット線BLに接続された電気的に書き換え可能な複数のメモリセルMCを含むメモリセルアレイと、前記ローカルビット線に接続され前記各メモリセルのデータを反転してグローバルビット線GBLに出力する複数のローカルセンスアンプLSAと、前記複数のローカルセンスアンプの出力の論理和を演算するグローバルセンスアンプGBSAと、前記複数のローカルセンスアンプを動作させて該複数のローカルセンスアンプに接続された複数のメモリセルのデータを同時にベリファイする第1ベリファイと,前記複数のローカルセンスアンプを停止させて,該各ローカルセンスアンプに接続された前記ローカルビット線と前記グローバルビット線を直結して該複数のローカルセンスアンプに接続された複数のメモリセルのデータを同時にベリファイする第2ベリファイとを切り替えるアドレスデコーダと、を有する。

(もっと読む)

半導体記憶装置及び半導体集積回路

【課題】メモリセルの誤読み出しを抑制する。

【解決手段】内部アドレス生成部14が、連続する第1の外部アドレスと第2の外部アドレスを受信すると、第1の外部アドレスに応じて選択されるメモリセルに接続されるビット線及びワード線以外のビット線及びワード線に接続されるメモリセルの何れかを選択する内部アドレスを第2の外部アドレスから生成することで、連続する外部アドレスを受信したとき、続けて同じビット線及びワード線に接続されたメモリセルが選択されなくなり、非選択状態のメモリセルの値が書き変わることによる誤読み出しが抑制される。

(もっと読む)

半導体記憶装置及びその制御方法

【課題】カラムブロックのデータラッチに対するデータの高速転送を可能にする。

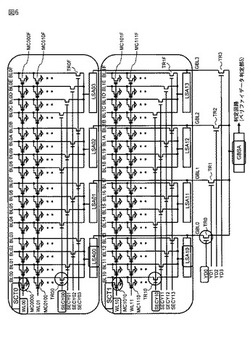

【解決手段】半導体記憶装置1は、メモリセルアレイ2と、データバスDBと、転送制御部TC0〜TC2と、複数のカラムブロックC(0+4×i)〜C(3+4×i)と、カラムセレクタCSとを含む。カラムブロックおよびカラムセレクタはメモリセルアレイより下に形成される。データバスDBは複数のステージS0〜S3に分割される。転送制御部は複数のステージのそれぞれにデータが割り当てられるようにデータをシリアル転送する。カラムブロックは選択された場合にデータを一次記憶する。カラムセレクタCSはカラムブロックの中から、ステージごとにいずれかのカラムブロックを選択し、ステージごとに選択されたカラムブロックとの間でデータをパラレル転送する。データバスDBはカラムブロックの配列方向の一方の端側から他方の端側へ向かい、他方の端側で折り返す。

(もっと読む)

半導体記憶装置

【課題】インタリーブ動作を実行可能に構成された半導体記憶装置における更なる動作の高速化を図る。

【解決手段】複数のアドレス変換回路151a〜151dが、メモリコア11a〜11dの各々にそれぞれ設けられ、外部から供給される論理アドレスデータを物理アドレスデータに変換する。アドレス変換回路は、インタリーブ動作において第1のメモリコアが第2のメモリコアより先にアクセスされる場合には、論理アドレスデータを変換せず物理アドレスとして出力する一方、第2のメモリコアが第1のメモリコアより先にアクセスされる場合には、論理アドレスデータに所定値を加算したアドレスデータに対応する物理アドレスデータとして出力する。

(もっと読む)

半導体記憶装置

【課題】低消費電力化に有利な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを備えるメモリセルアレイと、メモリセルの入力データまたは出力データをセンスするセンスアンプS/A0〜S/A7と、偶数側(Even Side)センスアンプと奇数側(Odd Side)センスアンプの間に、これらを電気的に分離するように配置されるラッチ回路22と、偶数側、奇数側センスアンプのいずれか一方に電気的に接続されるキャッシュメモリ23と、これらを制御する制御回路とを具備し、前記入力データの入力動作の際に、制御回路は、ラッチ回路の入力データを偶数側、奇数側センスアンプのいずれかへ転送させると共に、メモリの入力データを奇数側、偶数側センスアンプのいずれかへ転送させる。

(もっと読む)

不揮発性半導体記憶装置

【課題】電源電圧の供給停止を検出せずに、かつメモリセルからデータを読み出すことなく、書き換え動作中の電源遮断が容易に検出できる不揮発性半導体記憶装置を提供する。

【解決手段】行列上にフラッシュメモリセルが配置されたメモリアレイ99は、メモリブロック8_0〜8_3に分割される。メモリブロック8_0〜8_3は、データを記憶するノーマルメモリセルNCと、消去動作の完了の有無表わすためのフラグメモリセルFCを含む。制御回路6は、メモリブロックの消去動作が終了後に、フラグメモリセルFCを書込状態に設定する。

(もっと読む)

不揮発性記憶装置

【課題】電源投入時やリセット時に行われる不揮発性記憶装置の初期化動作において、初期化動作と外部アクセス動作とを好適に制御すると共に動作情報の読み出しを効率的に行うことにより、不揮発性記憶装置に対する読出しアクセス動作を、初期化動作の開始から短時間で可能とすること。

【解決手段】不揮発性記憶装置の各種の動作条件を設定する動作情報がメモリセルアレイに格納されている。書換えアクセス動作を制御する自動書換え制御回路を備え、自動書換え制御回路は、初期化動作時、動作情報の読み出し制御を行う際、ベリファイ増幅器ではなく読出し増幅器を活性化して動作情報を読み出す

(もっと読む)

不揮発性半導体記憶装置

【課題】 BiCSメモリのような積層型メモリの書き込み動作を高速化することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】 積層型のメモリセル構造を有する不揮発性半導体記憶装置であって、半導体基板上に、複数のメモリセルを積層してなるストリングを複数個配置したメモリセルアレイ11と、メモリセルアレイ11の任意のストリングをサンプルストリングとして選択し、該選択したサンプルストリングに対してデータの書き込みを行う回路12,14,16,30と、サンプルストリングの各メモリセルに対する書き込み回数をレイヤー毎に保持する書き込み回数記憶部31と、記憶部31に記憶されたレイヤー毎の書き込みパルス数を同一レイヤーの他のストリングのメモリセルの書き込み電圧の初期値に反映させる回路33とを備えている。

(もっと読む)

フラッシュメモリの優先順位付き消去のためのデバイスおよび方法

【課題】優先順位付き消去機能を持つ記憶デバイスおよび方法を得る。

【解決手段】記憶メモリは、少なくとも一つのフラッシュ・ユニットを持ち、各フラッシュ・ユニットは、複数のブロックを持つ。コントローラは、複数のブロック内へデータを書き込むよう、各ブロックへ、データの消去優先度と相互に関連する消去優先度を指定するよう、そして緊急消去コマンドを受信すると即座に、各ブロックの消去優先度に従って各ブロック内のデータを消去するよう構成される。コントローラは、第一のフラッシュ・ユニット内で任意の順序で複数のブロック内へ、データの書き込みを実行するよう構成されることが好ましい。そして以降のフラッシュ・ユニットへの書き込みは、第一のフラッシュ・ユニット内の順序に相関性を持って実行される。消去は、複数のブロックの少なくともいくつかに対して、消去を完了する前に消去をアボートすることを含むことが好ましい。

(もっと読む)

半導体メモリ

【課題】メモリの動作特性の向上を図る。

【解決手段】半導体メモリは、ロウ方向及びカラム方向に沿って配列され、複数のしきい値にそれぞれ対応するデータを記憶する複数のメモリセルを含むメモリセルアレイ1と、メモリセルアレイ1のロウを制御するロウ制御回路2と、外部からのアドレス信号に対応するポインタPTに基づいてメモリセルアレイ1のカラムを制御するための信号CNTを生成する制御ユニット70を有するカラム制御回路3と、を含む。

(もっと読む)

半導体装置

【課題】

実施形態は、ベリファイ動作の誤判定を低減可能な半導体装置を提供する。

【解決手段】

本実施形態の半導体装置は、偶数番目のワード線に接続された偶数メモリセルと、奇数番目のワード線に接続された奇数メモリセルと、前記偶数番目のワード線に接続された偶数コントロールゲート線と、前記奇数番目のワード線に接続された奇数コントロールゲート線と、前記偶数メモリセル及び前記奇数メモリセルに対して交互にベリファイ動作を行う制御部と、複数の前記偶数コントロールゲート線は相互に隣接し、複数の前記奇数コントロールゲート線は相互に隣接し、前記偶数コントロールゲート線に第1の電圧が供給され、前記奇数コントロールゲート線に第2の電圧が供給されることを特徴とする。

(もっと読む)

半導体メモリおよびシステム

【課題】 1つをメモリブロックの書き込み動作中に、別のメモリブロックの読み出し動作を実行することで、アクセス効率を向上する。

【解決手段】 半導体メモリは、複数ビットの書き込みデータおよび書き込みデータのパリティデータをビット毎に保持する複数のメモリ領域を有する複数のメモリブロックを有している。書き込みコマンドに応答して、メモリブロックの1つである書き込みメモリブロックのメモリ領域に、書き込みデータおよびパリティデータが順に書き込まれる。読み出しコマンドに応答して、書き込みメモリブロックを除くメモリブロックの1つにおいて、書き込みデータおよびパリティデータが供給されていないデータ線に対応するメモリ領域からデータが読み出され、書き込み動作により読み出させないデータが再生される。これにより、書き込み動作と並行して読み出し動作を実行できる。

(もっと読む)

半導体記憶装置

【課題】 データの読出しをフレキシブルにかつ高速に行うことができる半導体記憶装置を提供することを目的とする。

【解決手段】 本発明の半導体記憶装置は、同時にアクセス可能な2つのメモリバンクを有するメモリアレイ100と、行アドレス情報に基づきワード線を選択するワード線選択回路150と、受け取られた命令に基づきワード線選択回路150を制御するコントローラ140とを有する。コントローラ140は、第1の読み出し命令に応じてワード線選択回路150に第1の読出し動作を実行させ、第2の読出し命令に応じてワード線選択回路150に第2の読出し動作を実行させる。第1の読出し動作は、一方のメモリバンクのn番目のワード線を選択し、かつ他方のメモリバンクのn+1またはn−1番目のワード線を選択し、第2の読出し動作は、一方のメモリバンクのn番目のワード線を選択し、かつ他方のメモリバンクのn番目のワード線を選択する。

(もっと読む)

半導体記憶システム

【課題】 複数のチップを実装した場合において、消費電流の増加を抑制することが可能な半導体記憶システムを提供する。

【解決手段】 半導体記憶システムは、第1の半導体記憶装置71aと、第2の半導体記憶装置71bと、配線83とを有している。配線83は、第1の半導体記憶装置71aと第2の半導体記憶装置間71bに接続されている。第1、第2の半導体記憶装置71a,71bの一方が電荷を放電するとき、第1、第2の半導体記憶装置71a,71bの他方は、配線83を介して放電された電荷を受ける。

(もっと読む)

半導体記憶装置

【課題】動作速度を向上出来る半導体記憶装置を提供すること。

【解決手段】動作がプロセッサ2の制御によって自動で行われる半導体記憶装置1であって、不揮発性のメモリセルMCを備えたメモリセルアレイと、第1レジスタを保持し、電圧を発生する電源回路11と、第2レジスタを保持し、前記メモリセルからデータを読み出し増幅するセンスアンプ7と、第3レジスタ30を保持し、前記電源回路11と前記センスアンプ7の動作を制御する制御回路12と、前記第1乃至第3レジスタに命令を与えることにより、前記電源回路11、前記センスアンプ7、及び前記制御回路12の動作を制御する前記プロセッサ2とを具備し、前記制御回路12は、前記第3レジスタ30で受け取った前記命令をデコードして、デコード結果に基づいて前記電源回路11及び前記センスアンプ7を直接制御可能である。

(もっと読む)

半導体記憶装置、及び記憶媒体

【課題】ガベージコレクション処理による処理負荷を軽減し、ガベージコレクション処理の処理時間を短縮する。

【解決手段】フラッシュメモリ10は、予め定められたデータサイズ領域を示すページ単位でデータを書き込み可能な不揮発性記憶部11と、不揮発性記憶部11の指定された領域であって、複数のページを含む該指定された領域における有効データを一時記憶する記憶部12と、不揮発性記憶部11のページに有効なデータがあるか否かを示すアドレスマップ情報に基づいて、指定された領域における有効データを記憶部12に記憶させた後に、記憶部12に記憶された有効データを連続したページに書き込むガベージコレクション処理、及びガベージコレクション処理によって変更されたアドレスマップ情報を出力する処理を実行するコントロールロジック部13とを備える。

(もっと読む)

不揮発性半導体メモリ

【課題】 読み出し動作を高速に実行し、読み出しマージンを向上する。

【解決手段】 複数の不揮発性のレギュラーメモリセルにそれぞれ接続された所定数のレギュラービット線および所定数のレギュラーワード線とを各々含む一対のメモリ領域を有するレギュラーセクタと、一対のメインビット線と、一対のメモリ領域の間に配置され、一方および他方のメモリ領域のレギュラービット線を一方および他方のメインビット線にそれぞれ接続するスイッチと、リファレンスメモリセル、リファレンスビット線、リファレンスワード線を有するリファレンスセクタと、読み出し動作時に、リファレンスビット線を、データが読み出されるレギュラーメモリセルに接続されるメインビット線と異なるメインビット線に接続するリファレンススイッチと、メインビット線の電圧差を差動増幅するレギュラーセンスアンプとを有している。

(もっと読む)

不揮発性半導体記憶装置

【課題】オープンビット線が存在していても消去ベリファイをパスする消去ベリファイを実行できる不揮発性半導体記憶装置を提供することにある。

【解決手段】不揮発性のメモリセルが配置された第1のメモリセルブロックと、第1のメモリセルブロックにおける欠陥ビット線と置換する冗長ビット線を備える不良置換回路と、ビット線毎に設けられ、ワード線により選択された当該メモリセルに書き込むデータまたはメモリセルから読み出したデータを記憶するラッチを含むページバッファと、ベリファイ処理において、ビット線から読み出し、ページバッファのラッチに書き込まれたデータを、複数のビット線単位で一括判定する一括判定回路と、不揮発性のメモリセルが配置され、欠陥ビット線に対応するページバッファにおけるラッチにベリファイ処理において書き込まれる疑似データを記憶する、第2のメモリセルブロックと、を有する。

(もっと読む)

半導体メモリ

【課題】ビット線間の寄生容量による影響を低減することにより、高精度のデータの読出しを可能にする半導体メモリを提供する。

【解決手段】1つの主ビット線に互いに異なるタイミングでオン駆動するセレクタ素子及び当該セレクタ素子のそれぞれに接続された副ビット線を介して当該副ビット線のそれぞれにメモリセルが接続され、当該主ビット線に並置されるとともに固定電位に接続された固定電位線が設けられていること。

(もっと読む)

1 - 20 / 216

[ Back to top ]