Fターム[5C024GX05]の内容

光信号から電気信号への変換 (72,976) | 撮像素子の細部(構造) (7,971) | セル構造 (7,384) | 受光素子 (4,937) | 光導電体 (579)

Fターム[5C024GX05]の下位に属するFターム

Fターム[5C024GX05]に分類される特許

1 - 20 / 58

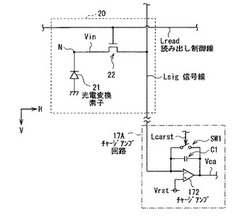

撮像装置および撮像表示システム

【課題】撮像画像の高画質化を実現することが可能な撮像装置、およびそのような撮像装置を備えた撮像表示システムを提供する。

【解決手段】撮像装置は、各々が光電変換素子を含む複数の画素を有する撮像部と、画素内に蓄積された信号電荷の読み出し駆動およびリセット駆動を行う駆動部とを備える。駆動部は、読み出された信号電荷を電圧に変換するチャージアンプ回路を有し、リセット駆動を1フレーム期間内で間欠的に複数回行い、かつ1フレーム期間内の各リセット駆動を、チャージアンプ回路におけるチャージアンプの帰還または仮想短絡現象を利用して行う。各画素において光電変換がなされ、信号電荷の読み出し駆動およびリセット駆動がなされ、入射光に基づく撮像画像が得られる。読み出し後の信号電荷の残留に起因するノイズを低減することができる。

(もっと読む)

多層型撮像素子

【課題】色再現性に優れる多層型撮像素子を提供する。

【解決手段】第1透明電極に積層される第1層間絶縁膜と、第1層間絶縁膜の上に配設される第2の信号読み出し部と、第2の信号読み出し部の上に配設され、光の3原色のうち第2の波長の光に感度を有する第2光電変換膜と、第2光電変換膜に積層される第2透明電極と、第2透明電極に積層される第2層間絶縁膜と、第2層間絶縁膜の上に配設される第3の信号読み出し部と、第3の信号読み出し部の上に配設され、光の3原色のうち第3の波長の光に感度を有する第3光電変換膜と、第3光電変換膜に積層される第3透明電極と、第1光電変換膜、第2光電変換膜、及び第3光電変換膜を画素毎に隔離する第1隔壁とを備え、前記第1の信号読み出し部、前記第2の信号読み出し部、及び前記第3の信号読み出し部は、それぞれ複数の画素が2次元方向に配置された画素アレイの各画素の信号読み出し部を形成している。

(もっと読む)

固体撮像素子および製造方法、並びに電子機器

【課題】光電変換効率の向上を図る裏面照射型のCMOSセンサを提供する。

【解決手段】撮像素子11は、半導体基板31に対して光が入射する側に積層される有機光電変換層33を備えており、有機光電変換層33に有機光電変換膜43が配置され、半導体基板31に2つのPD41、42が配置されている。そして、有機光電変換層33では、有機光電変換膜43を挟み込むように1対の透明電極54−1,54−2が設けられており、半導体基板31側の透明電極54−1が、光が入射する側に突出する曲面を有して形成され、有機光電変換膜43が、この透明電極54−1が有する曲面に倣って曲面形状を有するように形成される。

(もっと読む)

固体撮像素子、固体撮像素子の駆動方法、撮像装置

【課題】高画質化、多画素化、低コスト化、低消費電力化が可能な固体撮像素子の提供。

【解決手段】基板10上方に形成された有機材料を含む光電変換層22と、基板10に形成され光電変換層22で発生した電荷に応じた信号を読みだす信号読出し回路Sを有する固体撮像素子100は、読出し回路Sが、光電変換層22よって発生した電荷を蓄積する蓄積部11と、蓄積部11に蓄積された電荷が転送されるFD13と、蓄積部11の電荷をFD13に転送する転送トランジスタ(Tr)30と、FD13の電位をリセットするリセットTr31と、FD13の電位に応じた信号を出力する出力Tr32を含み、リセットTr31に供給するリセット電圧を制御して、当該リセット電圧を供給する電源から蓄積部11に電荷を注入し、その後、当該リセット電圧を制御して、蓄積部11に注入した電荷の一部を前記電源に排出させる駆動をフレーム毎に行う制御部104を備える。

(もっと読む)

固体撮像装置

【課題】 チップ面積を大きくすること無く、偽信号の発生を抑制することが可能な個体撮像装置を提供する。

【解決手段】 本発明は、複数の光電変換部が配された第1の基板と、読み出し回路及び並列処理回路が配された第2の基板とを有する固体撮像装置であって、前記複数の並列処理回路に直流電圧を供給する直流電圧供給配線を有し、該直流電圧供給配線は、第1の基板に配された第1の導電パターンと、前記第2の基板に配された第2の導電パターンとを、電気的に接続することにより構成されることを特徴とする。

(もっと読む)

固体撮像素子及び撮像装置

【課題】高感度かつ広ダイナミックレンジを実現することのできる固体撮像素子を提供する。

【解決手段】基板101上方に形成された光電変換層と、光電変換層で発生した正孔に応じた信号を読み出す読出し回路116とを有する。読出し回路116は、光電変換層と電気的に接続されたフローティングディフュージョンFDと、FDの電位をリセット電位にリセットするリセットトランジスタ204と、FDの電位に応じた信号を出力する出力トランジスタ205とを含む。トランジスタ204,205はnMOS型である。全ての電位の基準となる電位をGNDとし、MOSトランジスタ回路の電源電圧をVddとし、リセット電位をVsとし、リセットトランジスタ204がオン状態でのFD電位とリセットトランジスタ204がオン状態からオフ状態になった直後のFD電位との差をΔV2としたとき、GND<Vs<GND+ΔV2+(Vdd/5)の関係が成り立つ。

(もっと読む)

固体撮像装置及びその製造方法

【課題】いずれの波長の光においても、十分な感度を得ることのできる固体撮像装置を提供する。

【解決手段】本発明に係る固体撮像装置100は、半導体基板101と、半導体基板の上に形成された配線層と、配線層の上に形成された、複数の画素に対応する複数の下部電極層104b及び104gと、複数の下部電極層104b及び104g上に形成された有機光電変換膜106と、有機光電変換膜106上に形成された上部電極層107と、上部電極層107の上に形成された、複数の画素に対応する複数のカラーフィルタとを備え、複数のカラーフィルタは、主に第1の波長の光を透過するカラーフィルタ108gと、主に第1の波長よりも短い第2の波長の光を透過するカラーフィルタ108bとを含み、カラーフィルタ108bの下方に位置する有機光電変換膜106の厚さは、第1のカラーフィルタの下方に位置する有機光電変換膜106の厚さより厚い。

(もっと読む)

マルチスペクトル感光部材

シリコンP又はNベース層において、2つ、3つ、又は4つの上下に設置される多層複合感光画素は、それぞれ可視光又は可視光および赤外線スペクトル範囲内で直交又は相補されるスペクトルを感応するマルチ感光部材、およびその単一面加工又は両面加工などの方式。複合感光画素において、異なる層上の基本画素は異なるカラー又はスペクトルを感応するようにデザインすることができ、1つ以上の複合感応画素を重複に配列させて、マクロユニットを構成させることによって、マルチ感光チップが得られる。また、本発明には、新しい多層感光画素のデザインとそれを単一面2層、両面2層、両面3層、両面4層、単一面混合2層、および両面混合2層又は多層のマルチスペクトル感光部材の実例も含まれる。本発明のマルチスペクトル感光部材は、もっと優れたカラー感光性能とカラー感光および赤外線感光の集積および簡単な加工プロセスを持っている。  (もっと読む)

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、固体撮像装置の駆動方法、及び電子機器

【課題】有機材料又は無機材料からなる光電変換膜を一対の電極で挟んで構成された光電変換素子を基板上部に備える固体撮像装置において、電荷蓄積時における暗電流の発生を抑制することができる固体撮像装置を提供する。また、その固体撮像装置の製造方法、駆動方法、及びその固体撮像装置を用いた電気機器を提供する。

【解決手段】有機材料又は無機材料からなる光電変換膜19を第1の電極18及び第2の電極20で挟んで構成された光電変換素子21を基板13上部に備える固体撮像装置において、第1の電極18をアンプトランジスタTr1のアンプゲート電極24にのみ接続する。そして、画素信号の読み出しは、第1の電極18側から行い、リセット動作は、第2の電極20側から信号電荷を排出することで行う。

(もっと読む)

固体撮像素子、固体撮像素子の駆動方法及び撮像装置

【課題】高電圧の供給が可能で、電源ノイズに起因する画質の劣化を抑制することができ、固体撮像素子を備えるICチップの小型化を図ることが可能な固体撮像素子、固体撮像素子の駆動方法及び撮像装置を提供する。

【解決手段】固体撮像素子30は、基板1上に、下部電極14と、下部電極14の上に設けられた光電変換層15と、該光電変換層15上に設けられた上部電極16とを備え、基板1内に形成され、上部電極16と下部電極14との間に電界を生じさせるための電源電圧を供給する昇圧手段と、昇圧手段の出力と上部電極16とを電気接続させる配線部M4と、昇圧手段の出力に接続され、配線部M4の少なくとも一部によって形成された抵抗を含むローパスフィルタ40とを備える。

(もっと読む)

固体撮像装置および固体撮像装置の駆動方法

【課題】非常に光量が多い環境下でも、十分なダイナミックレンジを確保する。

【解決手段】画素アレイ部31の各画素311から読み出される信号を記憶する記憶手段34が、画素アレイ部31の画素311の数よりも多い画素数分だけ画素情報を記憶可能な容量を持ち、演算手段334において記憶手段34に格納されている各画素311の信号と画素アレイ部31から読み出される各画素311の信号とを加算または加算・平均化する前に、時間的に前の画像に対する後の画像の動きベクトルを検出する動きベクトル検出手段38の検出結果に基づいて、画素アレイ部31から読み出された各画素311の信号を記憶手段34に格納するアドレスの補正が行われ、アドレスを補正した後の各画素311の信号が、記憶手段34の対応する画素311の記憶領域に記憶される固体撮像装置10Bを構成する。

(もっと読む)

光電変換素子及び撮像素子

【課題】キャリアの湧き出しを抑制することで、暗電流を低下させることができる光電変換素子及び撮像素子を提供する。

【解決手段】一対の電極と、一対の電極の間に挟まれ、n型有機半導体を含む光電変換層と、一対の電極の少なくとも一方と光電変換層との間に設けられ、単層又は複数層からなる電荷ブロッキング層とを備え、

(a)光電変換層と隣接する電荷ブロッキング層のイオン化ポテンシャルIpとn型有機半導体の電子親和力Eaとの差(Δ1)が1eV以上、

(b)電荷ブロッキング層の総厚が20nm以上、である光電変換素子。

(もっと読む)

撮像装置及び撮像方法

【課題】本発明は、光電変換膜のハイライトキズの発生を効果的に抑制し、安定して撮像を行うことができる撮像装置及び撮像方法を提供することを目的とする。

【解決手段】撮像面に入射した光Lを電荷に変換するとともに、該電荷をアバランシェ増倍作用により増加させる光電変換膜23を有し、該光電変換膜に蓄積された電荷を読み取ることにより撮像を行う撮像装置100、100a〜100cであって、

前記撮像を行う前に、前記光電変換膜の前記撮像面に紫外線を照射する紫外線照射手段50を有することを特徴とする。

(もっと読む)

半導体装置の駆動方法

【課題】信号書き込み時間が長くなることを防ぎながら、信号振幅値が大きく、かつ、入出力関係が線形で動作する範囲を大きくすることが出来る半導体装置およびその駆動方法を提供する。

【解決手段】増幅用トランジスタ及びバイアス用トランジスタを有する半導体装置において、放電用トランジスタを設けて、プリ放電を行う。または、増幅用トランジスタ及びバイアス用トランジスタを有する半導体装置において、バイアス用トランジスタに接続されたバイアス側電源線の電位を、増幅用トランジスタに接続された増幅側電源線の電位に近づけることにより、プリ放電を行う。

(もっと読む)

固体撮像素子及び撮像装置

【課題】FGを有する固体撮像素子であって、高速連写や滑らかな動画撮像を行うことが可能な固体撮像素子を低コストで提供する。

【解決手段】光電変換部17と、光電変換部17で発生した電荷を蓄積するためのフローティングゲート(FG)16を含むトランジスタ13とを有する固体撮像素子10であって、フローティングゲート16に蓄積された電荷を引き抜いて消去するための電荷消去用電極(EG)15を備える。

(もっと読む)

積層型固体撮像装置

【課題】本発明は、高画質な出力を得られる積層型固体撮像装置を提供することを目的とする。

【解決手段】2次元状に配列された画素100毎に設けられた画素トランジスタ30と、

該画素トランジスタの一方の拡散層に接続された画素電極31の上に積層され、該画素電極側と反対側に位置する受光面で受光した光を光電変換して、信号電荷を発生させる光電変換膜10と、

該光電変換膜の前記受光面上に設けられた透明電極20と、

読み出し対象となる前記画素を、前記画素トランジスタをオンとして選択するともに、前記画素電極から所定の固定電位を供給して前記光電変換膜を初期バイアス状態に戻す固体駆動部80と、

前記透明電極に接続され、前記光電変換膜が前記初期バイアス状態に戻るときに、前記光電変換膜を流れる前記信号電荷に対応する電流を検出し、光電変換膜で発生した前記信号電荷を読み出す読み出し回路130と、を有することを特徴とする。

(もっと読む)

撮像装置

【課題】アンプへのノイズによる画質低下を低減させることができる撮像装置を提供することを目的とする。

【解決手段】コントローラは取り出し動作制御の機能を備え、その取り出し動作制御の機能は、電荷電圧変換アンプのサンプルホールドで保持された電圧値を取り出す取り出し動作を、電荷電圧変換アンプ中のアンプをリセットするアンプリセット中に行うように制御するので、取り出し動作を行う素子であるスイッチング素子を駆動させることによるノイズが混入してもリセットされて、アンプへのノイズによる画質低下を低減させることができる。このとき、好ましくは、A/D変換もアンプリセット中に行うように制御すると、A/D変換器を駆動させることによるノイズが混入してもリセットされて、アンプへのノイズによる画質低下をより一層低減させることができる。

(もっと読む)

撮像装置及び固体撮像素子の駆動方法

【課題】半導体基板上方の光電変換素子で発生した電荷を読み出す際、光電変換素子と半導体基板との接続部に電荷が残留してしまうのを防ぐ。

【解決手段】基板1上方に積層された一対の電極14,16とこれに挟まれる光電変換層15とを含む光電変換素子Pをそれぞれ有する複数の画素を含む固体撮像素子30と、固体撮像素子30を駆動する駆動部35とを備える撮像装置であって、該画素が、基板1内に設けられ電極14と電気的に接続される接続部3と、接続部3に隣接して設けられ該接続部3の電位に対して電位障壁となる電位障壁部7と、電位障壁部7に隣接して設けられ光電変換層15で発生した電荷が接続部3及び電位障壁部7を介して蓄積される第一の電荷蓄積部4と、第一の電荷蓄積部4に蓄積された電荷に応じた信号を出力する信号出力回路とを含み、駆動部35は、接続部3に電荷を注入して、接続部3と電位障壁部7を同電位にする駆動を行う。

(もっと読む)

画像検出装置

【課題】基板製造時の静電気不良を防ぐ一方で、駆動時のリーク電流による信号値の変動を抑制することができる画像検出装置を提供する。

【解決手段】検出対象とする画像を示す電磁波が照射されることにより当該画像を示す状態で電荷が蓄積される複数の電荷蓄積容量5、各々複数の電荷蓄積容量5に個別に接続された複数のデータ配線3、過大電圧から回路を保護するため回路を保護するための共通配線110A、110B、共通配線110Aにアノードが接続され、各々前記複数のデータ配線3にカソードが接続された複数のダイオード32A、及び共通配線110Bにカソードが接続され、各々複数のデータ配線3にアノードが接続された複数のダイオード32Bを有するアクティブマトリクス基板10を備える。

(もっと読む)

放射線画像検出器

【課題】電圧が印加される電圧印加電極と、放射線の照射を受けて電荷を発生する半導体層とが積層された放射線画像検出器において、画像領域を狭くすることなく、電圧印加電極から半導体層への電荷の注入を抑制するとともに、電圧印加電極の端部における放電破壊を防止する。

【解決手段】電圧印加電極1の少なくとも端部を覆うように電荷注入阻止層11を設け、電荷注入阻止層11の上面に、電圧印加電極1の端部1aの側端面1bよりも外側に一方の側端面12aが位置するとともに、他方の側端面12bが電圧印加電極1の端部1aの側端面1bの位置またはその側端面1bの位置よりも内側に位置するように張出電極12を設ける。

(もっと読む)

1 - 20 / 58

[ Back to top ]