Fターム[5C024HX15]の内容

光信号から電気信号への変換 (72,976) | 回路構成 (15,472) | タイミング補正、位相調整 (157)

Fターム[5C024HX15]に分類される特許

1 - 20 / 157

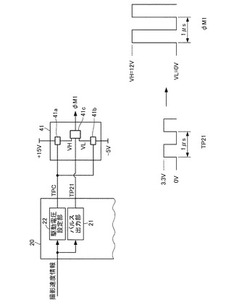

駆動装置及び駆動方法並びに駆動装置を備えた撮像装置

【課題】高速駆動時のダイナミックレンジを従来よりも拡大することができる駆動装置を提供する。

【解決手段】駆動装置は、FPGA20及び第1蓄積転送パルス出力部41を備え、FPGA20は、撮影速度が、撮影速度閾値未満のときローレベルの制御信号、撮影速度閾値以上のときハイレベルの制御信号を出力する駆動電圧設定部22を備え、第1蓄積転送パルス出力部41は、ローレベルの制御信号を入力したときVH=12Vを出力し、ハイレベルの制御信号を入力したときVH=13.5Vを出力する電圧変換素子41aと、ローレベルの制御信号を入力したときVL=0Vを出力し、ハイレベルの制御信号を入力したときVL=−1.5Vを出力する電圧変換素子41bと、VH及びVLに基づいて撮影速度に応じた周波数を有する蓄積転送パルスφM1を出力するドライバ素子41cと、を備える。

(もっと読む)

撮像装置及び電子機器

【課題】 静止画モード時にA/D変換時のセトリング期間を確保でき、画像信号の劣化を抑制できる撮像装置及び電子機器を提供する。

【解決手段】 撮像装置は、入射光を信号電荷に変換する光電変換部を有する複数の画素部と、前記信号電荷を蓄積し、信号電圧に変換するフローティングディフュージョン部と、前記信号電圧をデジタル信号に変換するアナログ・デジタル変換部と、リセットパルスが入力されることで、前記フローティングディフュージョン部に蓄積された信号電荷を破棄するリセット部と、前記画素部の信号電荷をそれぞれ信号電圧に変換する第1モードの場合、第1のLowレベルを有する第1のリセットパルスを生成し、前記複数の画素の信号電荷を加算して前記信号電圧に変換する第2モードの場合、前記第1のLowレベルより低い第2のLowレベルを有する第2のリセットパルスを生成して、前記リセット部に供給するリセットパルス生成部とを備える。

(もっと読む)

データ転送回路、固体撮像素子、およびカメラシステム

【課題】データ出力部への転送線上の配線遅延による影響を低減でき、データ出力部におけるデータの取り込みを的確かつ高精度に行うことが可能で、ひいては走査の高速化を図ることが可能なデータ転送回路、固体撮像素子、およびカメラシステムを提供する。

【解決手段】基本的に、列走査回路13は、クロック供給回路21から供給されるマスタクロックMCKを所定の配線を通してシフトレジスタ131を構成するラッチ131−0〜131−nに、たとえば最遠端側のラッチ131−0から順番に供給し、データ出力回路17−0〜17−nは、マスタクロックMCKを基準とするクロックが位相調整された取り込みクロックSACKによりセンスアンプ回路171−0〜171−nの出力データを取り込む。

(もっと読む)

画像処理装置

【課題】撮影における要求に応じて、最適な広ダイナミックレンジ映像を得ることを可能とする画像処理装置を提供すること。

【解決手段】実施形態によれば、画像処理装置である画像処理回路20は、ライン露光選択部24及び画像合成部25を有する。ライン露光選択部24は、画素アレイのラインごとに、第1の露光時間及び第2の露光時間のいずれを適用するかを選択する。第2の露光時間は、第1の露光時間より短い。画像合成部25は、飽和画素の信号値を、第2の画素の信号値を使用して補間する。第2の画素は、第2の露光時間が適用される画素である。ライン露光選択部24は、第1の露光時間及び第2の露光時間を選択するパターンを切り換え可能とする。ライン露光選択部24は、合成画像に要求されるフレームレートと、合成画像に要求される画像サイズとの少なくとも一方に応じて、パターンを切り換える。

(もっと読む)

固体撮像装置

【課題】画素数の増大に伴うバッファの数の増大、微細化に伴うプロセスばらつきの増大により、このクロック信号のデューティ比の崩れを抑制する。

【解決手段】固体撮像装置1は、複数の画素10がアレイ状に配置された画素部20と、少なくとも一つのアナログデジタル変換部30を含む第1グループおよび第2グループを有する変換部と、直列に接続された第1のクロックバッファおよび第2のクロックバッファを有するクロック供給部とを含み、第1グループおよび第2グループのアナログデジタル変換部のそれぞれは、比較部およびカウンタ部を有し、第1のクロックバッファは、補正されたクロック信号を偶数段のCMOSインバータ回路を介して、第1グループのカウンタ部のそれぞれと第2のクロックバッファに出力し、第2のクロックバッファは、補正されたクロック信号を偶数段のCMOSインバータ回路を介して第2グループのカウンタ部のそれぞれに出力する。

(もっと読む)

電子内視鏡装置

【課題】撮像と表示との同期を確保することができる電子内視鏡装置を提供する。

【解決手段】位相制御部111は、表示同期信号110と、撮像クロック生成部106が生成したクロック信号107から生成されたクロック信号113との位相を比較し、比較結果に基づいて撮像クロック生成部106の発振を制御する。駆動信号生成部125は、クロック信号107に同期した逓倍クロック信号120に基づいて、CMOSセンサ122を駆動する駆動信号121を生成する。

(もっと読む)

固体撮像装置及び固体撮像装置の駆動方法

【課題】 画素列に設けられた増幅回路において簡易な構成で高ゲインの増幅が行うことが可能となる構成を提供する。

【解決手段】 半導体基板に、複数の画素列を有する撮像領域と、各画素列ごともしくは複数の画素列ごとに設けられた、複数の列増幅回路が配された固体撮像装置であって、前記各列増幅回路は少なくとも2段の増幅回路を含んで構成され、前段の増幅回路は、ゲイン可変の増幅回路であり、且つ前記切り換え可能なゲインは1以上のゲインを複数含んでおり、後段の増幅回路は、前記前段の増幅回路において前記1以上のゲインで増幅された信号を更に1以上のゲインで増幅可能な構成であることを特徴とする。

(もっと読む)

固体撮像装置およびカメラシステム

【課題】画素信号を加算して読み出す場合において、カラム処理の回数を減らすことが可能となり、その結果として、回路の低消費電力化や更なる高速撮像を実現することが可能な固体撮像装置およびカメラシステムを提供する。

【解決手段】画素配列の1列に対して複数の列信号線が配線され、複数の列信号線に画素の位置する行に応じて規則的に接続さている画素アレイ部と、画素アレイ部から複数の画素単位で画素信号の読み出しを行い、読み出し信号に対してカラム単位でカラム処理を行うカラム処理部を含む画素信号読み出し部とを有し、画素信号読み出し部は1つのカラム処理部の入力に対して、並列に接続された複数のキャパシタを介してカラムに対応する列に配線された1または複数の列信号線を接続可能なカラム入力部を含み、カラム入力部は複数のキャパシタとカラムに対応する複数の列信号線との接続状態を変更可能なスイッチを含む。

(もっと読む)

イメージセンサ通信装置と方法

【課題】通信データの高速化、小型化、低消費電力化を図り、座標補正等を行うことを不要とする装置の提供。

【解決手段】画素回路11と電荷を蓄積保持する第1の保持回路12と第1の保持回路と第1の出力信号線41間に接続され、第1の制御信号S−Ccsにより、第1の保持回路に保持された電荷に対応する信号を前記第1の出力信号線41に通信用として出力する第1のスイッチ33と第2の制御信号S−Dtにより制御される第2のスイッチ32を介して第1の保持回路12の出力に接続され、第1の保持回路12の電荷を蓄積保持する第2の保持回路13と第2の保持回路13と第1の出力信号線41間に接続され、第3の制御信号S−Vrsにより制御され、第2の保持回路13に保持された電荷に対応する信号を第1の出力信号線41に撮像用として出力する第3のスイッチ34と、を含む。

(もっと読む)

部品実装装置における画像読取装置および画像読取方法

【課題】画像信号へのノイズの混入を生じることなく画像信号の出力を効率化して、部品の画像読取りの高速化を実現することができる部品実装装置における画像読取装置および画像読取方法を提供する。

【解決手段】ラインセンサから出力された画像信号をAD変換処理後に画像形成部に出力するに際し、AD変換処理後の画像信号30a1についてAD変換処理に伴って生じる応答遅れに相当する画像信号30a*を、直後にAD変換処理される後続の画像信号30a2に時系列を合致させて結合して画像形成部に対して出力する画像調整処理を実行する。これにより、ラインセンサにおいて電荷の転送を行っている間にもAD変換処理部を継続して駆動させることが可能となり、AD変換処理の中断に起因する画像信号へのノイズの混入を防止しながら画像信号の出力を効率化して部品の画像読取りの高速化を実現することができる。

(もっと読む)

画像理装置および方法、並びにプログラム

【課題】より簡単かつ高精度に欠陥画素を検出できるようにする。

【解決手段】近傍領域抽出部は、画像上の注目画素近傍の領域を注目近傍領域として抽出する。テクスチャ方向判定部は、注目近傍領域について、注目画素と同じ色の画素の画素値の変化の小さい方向をテクスチャ方向として特定する。欠陥画素検出部は、注目画素を中心とし、テクスチャ方向に連続して並ぶいくつかの画素を用いて、ラプラシアンを算出するとともに、異なる画素の組ごとに算出した複数のラプラシアンを閾値と比較して、注目画素が欠陥画素であるかを特定する。このように複数のラプラシアンを用いることで、注目画素が単独欠陥画素であるか、連続欠陥画素であるかによらず、簡単かつ高精度に欠陥画素を検出することができる。本発明は、画像処理装置に適用することができる。

(もっと読む)

撮像装置、及びその制御方法、プログラム

【課題】ローリングシャッタ問題による歪みを補正する場合の補正残り、あるいは過補正を低減する。

【解決手段】ローリングシャッタ方式で駆動する撮像素子を用いて画像を撮像する場合に、当該撮像素子の露光期間における撮像装置の振動を検出し、検出された振動の時間特性を取得する。振動の時間特性について、振動に起因して画像に生じる被写体像の歪み量の周波数分布を解析し、当該周波数分布から歪み量が極大となる周波数を、歪み量の中心周波数として決定する。そして少なくとも中心周波数について、振動の時間特性を取得した際に生じた位相ズレがなくなるように、振動の時間特性を補償し、補償後の振動の時間特性から算出された補正量を用いて、撮像素子のラインごとに振動に起因して生じた被写体像の歪みを補正する。

(もっと読む)

撮像装置、及びその制御方法、プログラム

【課題】ローリングシャッタ問題による歪みを補正する場合の補正残り、あるいは過補正を低減する。

【解決手段】ローリングシャッタ方式で駆動する撮像素子を用いて画像を撮像する場合に、当該撮像素子の露光期間における撮像装置の振動を検出し、検出された振動の時間特性を取得する。振動の時間特性を、振動の周波数について複数の帯域に分離し、振動に起因して画像に生じる被写体像の歪み量の周波数特性を、各帯域について算出し、当該歪み量の周波数特性が極大となる帯域を、歪み量の中心周波数が含まれる帯域として決定する。そして、少なくとも中心周波数が含まれる帯域の1つの周波数について、振動の時間特性を取得する際に生じた位相ズレがなくなるように振動の時間特性を補償する。さらに補償後の振動の時間特性から算出された補正量を用いて、撮像素子のラインごとに振動に起因して生じた被写体像の歪みを補正する。

(もっと読む)

撮像装置

【課題】ベイヤ配列の撮像信号を、混色させること無く、解像度の低下を最小限に、撮像装置の感度を大きくする。

【解決手段】注目画素を中心とする5×5画素の領域内に位置し、第1の色成分の光を検出する第1種の画素の画素値だけを加重加算して第1の色成分(R)値を生成し、同様に注目画素を中心とする5×5画素の領域内に位置し、第3の色成分(B)の光を検出する画素の画素値だけを加重加算して第3の色成分(B)値を生成する。注目画素を中心とした3×3画素の領域内に位置し、第2の色成分(G)の光を検出する画素の画素値だけを加重加算して第2の色成分(G)値を生成する。

(もっと読む)

固体撮像装置

【課題】ダミー画素領域の増大を抑えつつ、非直線性ばらつきを除去するための補正式を算出することができる固体撮像装置を提供する。

【解決手段】画素アレイ3において、有効画素1は、少なくとも、入射光量に基づく画素信号を出力し、ダミー画素2は、与えられた基準電圧の電圧値に基づく画素信号を出力する。制御回路8は、ダミー画素2に、少なくとも、第1の基準電圧を与えてiフレーム分のダミー画素2の画素信号を読み出し、第2の基準電圧を与えてjフレーム分のダミー画素2の画素信号を読み出す制御を行う。補正式算出回路9は、少なくとも、第1の基準電圧が与えられたときに読み出されたiフレーム分のダミー画素2の画素信号をアナログ・デジタル変換した値と、第2の基準電圧が与えられたときに読み出されたjフレーム分のダミー画素2の画素信号をアナログ・デジタル変換した値とから、A/D変換器6の非直線性を補正する補正式を算出する。

(もっと読む)

固体撮像装置

【課題】固体撮像装置を大型化させることなく、A/D変換回路の動作に起因する入力およびGNDの電圧レベルの変動を低減し、出力するデジタル値の変動(誤差)を低減することができる固体撮像装置を提供する。

【解決手段】光電変換素子のリセット信号と画素信号とを出力する画素が二次元の行列状に複数配置された画素部と、所定の1つの画素からのリセット信号および画素信号が順次入力される第1の容量と、画素信号とリセット信号との差を保持する第2の容量とを具備し、差分信号を出力するアナログ信号処理部と、差分信号の大きさに応じた遅延時間でパルス信号を遅延させる遅延素子がリング状に複数段接続された遅延回路と、パルス信号の遅延回路内の伝播を検出した結果に基づいたデジタル信号を生成するアナログ・デジタル変換器と、アナログ信号処理期間とサンプリング期間とで第1の容量の接続を切り替える切り替え回路と、を備える。

(もっと読む)

撮像装置および撮像装置の制御プログラム

【課題】最適な駆動周波数で撮像素子を駆動した場合、設定された動画像のフレームレートとの差により、一定のフレーム間隔ごとに、同一フレームを連続させる重複処理などを行わなければならず、画質の劣化を招いていた。

【解決手段】上記課題を解決するために、撮像装置は、被写体像を光電変換してフレーム画像信号を出力する撮像部と、フレーム画像信号が順次書き込まれ、かつ、順次読み出される記憶部と、記憶部におけるフレーム画像信号の読み書き状況を監視する監視部と、監視部が監視する読み書き状況に基づいて、撮像部からフレーム画像信号を出力させるタイミングを規定する垂直同期信号の間隔を変化させる制御部とを備える。

(もっと読む)

手振れ補正機構を備えた撮影装置

【課題】手振れ補正動作処理を行う間、姿勢変化に関係なく、高画質の画像を得る。

【解決手段】カラムA/D変換器を組み込んだCMOSセンサを備えたデジタルカメラにおいて、CMOSセンサを支持し、ボイスコイルをCMOSセンサの傍に配置させた移動ステージと、ボイスコイルと対向するように永久磁石を取り付けた固定ステージによって構成される手振れ補正機構を設ける。そして、カメラの姿勢変化に応じて移動ステージを固定部に対して相対移動させ、手振れ補正動作処理を所定時間間隔で実行する。このとき、ボイスコイルへ送るパルス駆動信号PSのONタイミング、OFFタイミングを画素信号読み出し用の水平同期信号HDに同期させる。

(もっと読む)

撮像装置及び撮像装置の制御方法

【課題】IRカットフィルタが脱着できる撮像装置にて、IRカットフィルタを抜いたときの赤外成分によるOB部への光漏れによる影響を抑制できるようにする。

【解決手段】有効画素部とOB部とを備えた撮像素子と、撮像素子に入射される光の赤外成分を遮断するIRカットフィルタとを有し、OBクランプ領域からの出力を用いて撮像素子の出力に係る黒レベルを決定するOBクランプ回路と、IRカットフィルタの脱着に応じてOB部におけるOBクランプ領域を設定するクランプ領域制御回路とを有し、IRカットフィルタが抜かれている場合には、通常時と比較して有効画素部から離れた位置にOBクランプ領域を設定する。

(もっと読む)

電荷結合素子の駆動装置、空間情報検出装置

【課題】複数の電極に跨る領域に形成したポテンシャル井戸からそれより少数の電極に対応して形成したポテンシャル井戸に電荷を移動させるのに要する時間を短縮する。

【解決手段】駆動装置は、クロック信号を発生させるクロック生成部と、電極10のうち隣接する電極10に制御電圧を印加するタイミングを制御することにより素子形成層13の表面に沿った面内でのポテンシャル井戸11の面積を変化させる印加電圧制御部とを備える。印加電圧制御部は、電極10への制御電圧の印加により素子形成層13に形成されるポテンシャル井戸11を制御して素子形成層13の電荷12の移動を制御する。また、印加電圧制御部は、基準タイミング信号を遅延させることにより隣接する電極10に異なるタイミングで印加する制御電圧を生成し、各電極10に印加する制御電圧を遅延させる時間はクロック信号の周期よりも短い時間とする。

(もっと読む)

1 - 20 / 157

[ Back to top ]