Fターム[5E346AA45]の内容

多層プリント配線板の製造 (97,916) | 多層の形状、構造 (21,562) | クリアランスホールの形状、構造が特定されたもの (86)

Fターム[5E346AA45]に分類される特許

1 - 20 / 86

配線基板及びその製造方法

【課題】熱膨張率の差によるスルーホールビアのクラックを防止する。

【解決手段】配線基板は、カーボン繊維を含む板状の基材と、前記基材の表面に形成された配線層と、前記基材を貫通する第1の貫通孔と、前記第1の貫通孔の内壁に形成され第2の貫通孔を有する第1の樹脂層と、前記第2の貫通孔の内壁に形成された第1の導電層とを有する第1のビアと、前記基材を貫通する第3の貫通孔と、前記第3の貫通孔の内壁に形成された第2の導電層とを有する第2のビアとを含み、前記第3の貫通孔の内径は、前記第2の貫通孔の内径より大きい。

(もっと読む)

プリント基板および樹脂封止モジュールの製造方法

【課題】プリント基板に実装された電子部品を樹脂封止する際、型締め圧力によるプリント基板の変形を防ぐことの可能なプリント基板、および樹脂封止モジュールの製造方法を提供する。

【解決手段】本発明の一実施形態によるプリント基板は、一対のモールド金型によりプリント基板10の厚さ方向に印加される型締め圧力を受ける耐圧部材20を備え、

耐圧部材20は、プリント基板10を厚さ方向に貫通し且つ厚さ方向で孔径の変化する多段貫通孔に配設され、プリント基板10よりも圧縮強度の高い材料からなることを特徴とする。

(もっと読む)

多層基板

【課題】ノイズ成分に対して効果的に対策された多層基板の提供を目的とする。

【解決手段】導電パターンが形成された第一の表面層及び第二の表面層と、前記第一及び第二の表面層の間に設けられたグランド層と、前記第一及び第二の表面層の間に設けられた電源層と、を備えて構成される多層基板において、前記第一の表面層に形成された導電パターンと前記第二の表面層に形成された導電パターンとの間を貫通するよう形成されたビアホールと、前記第一の表面層又は前記第二の表面層のいずれかにおいて、前記ビアホールと接続するよう形成された導体パッドと、を有し、前記導体パッドが、3PFから5PFの容量を備える。

(もっと読む)

回路基板

【課題】簡単な構成で、パターン重複部分での特性インピーダンスの整合を容易に実現することが可能な回路基板を提供する。

【解決手段】電気的絶縁層5を介して順に積層配置された、グランド層2と、信号伝送配線3と、グランドパターン4とを備えた回路基板1である。グランド層2の、信号伝送配線3とグランドパターン4との重複部分をグランド層2に正射影したときの射影領域を少なくとも含む部分6が除去されている。

(もっと読む)

多層配線基板、部品内蔵基板、および多層配線基板の製造方法

【課題】配線基板と電気絶縁層を積層して一体化した多層配線基板において、電気絶縁層に形成されたビアと、配線基板に形成されたビアランド間の接続信頼性を向上させる。

【解決手段】貫通するビアホールに導電性ペーストが充填されて形成されたビア202を有する電気絶縁層201の表裏の、ビアに対応する位置に、ビアの、電気絶縁層の面方向の断面積より大きいビアランド207が形成された多層配線基板251、252が積層して一体化され、少なくとも一方の多層配線基板には、電気絶縁層に埋め込まれた電子部品が実装されている。ビアとビアランドとの間には、一部隙間205が形成されており、ビアと接触するビアランドの接触面積は、ビアの断面積の20%以上75%以下である。

(もっと読む)

多層基板及び多層基板の製造方法

【課題】多層基板の内層と外層とを接続する貫通ビアホールのインピーダンスを制御する。

【解決手段】一方の基板表面の導体層に形成された外層パターンと内層パターンとの間に、内層パターンを非貫通であって、グランドに接続されるベリードビアホール、ベリードビアホールの内側に形成された管状の絶縁体、及び、管状絶縁体の管内面に形成され、外層パターンと内層パターンとを少なくとも接続する貫通ビアホールを設ける。

(もっと読む)

配線基板

【課題】半導体集積回路素子に対して十分な電源供給を行なって半導体集積回路素子を良好に作動させることが可能な配線基板を提供すること。

【解決手段】接地用のスルーホール導体5Gおよびこれに接続される接地用の外部接続パッド8Gと電源用のスルーホール導体5Pおよびこれに接続された電源用の外部接続パット8Pとが互いに隣接して配置されており、接地用のスルーホール導体5Gと接地用の外部接続パッド8Gとをそれぞれ2箇所ずつで接続する接地用のビア接続経路6Gbおよび電源用のスルーホール導体5Pとの電源用の外部接続パッド8Pとをそれぞれ2箇所ずつで接続する電源用のビア接続経路6Pbと、を有する配線基板であって、接地用のビア接続経路6Gbと電源用のビア接続経路6Pbとは、互いに向き合う方向に片寄って配置されている。

(もっと読む)

半導体パッケージ基板の検査方法、半導体パッケージ基板の製造方法、半導体パッケージ基板

【課題】コンデンサ実装後に半導体パッケージ基板出荷する場合の電気検査において、コンデンサを破壊することなく絶縁性を保証でき、検査工程を増やすことがない検査方法、半導体パッケージ基板を提供する。

【解決手段】フリップチップBGAパッケージ用基板1上にコンデンサ13を実装するための1対の金属バンプ15のうち、少なくとも一方に接続する金属配線5の一部が検査用プローブB−1、B−2との接触のためソルダーレジスト4’から露出され、露出されているパッド部10がコンデンサ13と導通するパッド部10a、コンデンサ13と導通しないパッド部10bとに分離されていて、パッド部10a、10bのそれぞれに検査用プローブB−1、B−2を接触させて電気検査を行う。

(もっと読む)

プリント配線板及びプリント配線板の製造方法

【課題】芯材を備えない層間絶縁層をコア基板に積層しても反りの生じないプリント配線板を提供する。

【解決手段】ガラスクロスの芯材にガラスエポキシ樹脂を含浸させたコア基板30に無機粒子を添加して、熱膨張係数(CTE)を20〜40ppmまで低下させている。そして、コア基板30の厚みaを0.2mmに、上面側の第1層間絶縁層50Aの厚みbを0.1mmに、下面側の第2層間絶縁層50Bの厚みcを0.1mmに設定してある。これにより、薄いコア基板30と、芯材を備えない層間絶縁層50A、50Bとを用いて、プリント配線板に反りを発生させない。

(もっと読む)

配線基板

【課題】絶縁層の上下面の複数の配線導体を電気的に接続する貫通導体が貫通孔の内側面から剥がれることを抑制することが可能な配線基板を提供する。

【解決手段】セラミック焼結体からなり、厚み方向に貫通する貫通孔3を有する絶縁板1と、貫通孔3内に充填された貫通導体2とを備える配線基板であって、貫通孔3の内側面と貫通導体2の側面との間に、内部に空隙4aを含んだ焼結体からなる緩衝層4が介在している配線基板である。貫通導体2の熱膨張を、空隙4aを含んだ緩衝層4の変形によって吸収することができるため、貫通導体2の長さ方向の膨張を抑制して、貫通導体2の絶縁板1からの突出を抑制できる。

(もっと読む)

機能素子内蔵基板

【課題】本発明は、補強層に設けた開口部に機能素子を内蔵する場合に、応力の局所的な集中を緩和し、かつ応力の発生を低減できる機能素子内蔵基板を提供することを目的とする。

【解決手段】本発明は、電極端子を有する機能素子と、該機能素子が配置され、かつ該機能素子の角部と対向する部分が湾曲形状となっている開口部を有する補強層と、前記開口部に配置される前記機能素子と前記補強層との間に配置される充填樹脂と、前記充填樹脂に形成される応力緩和ビアと、前記機能素子の前記電極端子が配置されている面側に該電極端子と電気的に接続される第1の配線層と、を有することを特徴とする機能素子内蔵基板である。

(もっと読む)

配線基板

【課題】反りを低減可能であると共に、高密度化にも対応可能な配線基板を提供すること。

【解決手段】複数の配線層と、同一組成の絶縁性樹脂から構成された複数の絶縁層とが交互に積層され、第1の主面及びその反対面である第2の主面を有する配線基板であって、前記第1の主面に最も近い第1の絶縁層から露出する第1のピッチで配置された第1の電極パッドと、前記第2の主面に最も近い第2の絶縁層に隣接する第3の絶縁層上に設けられ、前記第2の絶縁層の開口部から露出する、前記第1のピッチよりも広い第2のピッチで配置された第2の電極パッドと、前記第3の絶縁層に設けられ、前記第2の電極パッドと前記第3の絶縁層が被覆する配線層とを電気的に接続する導体が形成された貫通孔と、を有し、前記貫通孔の前記第2の電極パッド側の径は、前記貫通孔の前記第3の絶縁層が被覆する配線層側の径よりも大きく、前記第2の絶縁層は、補強部材を備えている。

(もっと読む)

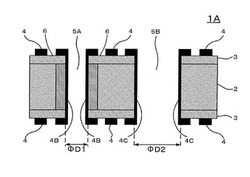

積層回路基板および基板製造方法

【課題】接着層の絶縁性が劣化することを防止するとともに、接合の信頼性が低下することを防止することを課題とする。

【解決手段】積層回路基板1は、基板10Aおよび基板10Bの接続ランド12同士が導電材料13により接合され、複数の配線パターン11が電気的に結合された多層構造のプリント配線基板である。また、積層回路基板1は、基板10Aと基板10Bとの間に、ランド12同士を接合するための貫通孔31が形成されたプレート30を有する。プレート30は、導電材料13を形成する位置に対応する貫通孔31があり、貫通孔31の径の大きさが導電材料13の充填径よりも大きい。

(もっと読む)

多層フレキシブルプリント配線板及びその製造方法

【課題】小径のステップビア構造を有する多層フレキシブルプリント配線板を安価に且つ安定的に製造する方法を提供する。

【解決手段】可撓性の絶縁ベース材11と、接着剤層24を介して絶縁ベース材11の裏面に積層された絶縁ベース材21と、絶縁ベース材11を貫通する上穴26、及び接着剤層24及び可撓性絶縁ベース材21を貫通し、底面にランド部31が露出した下穴27を有するステップビアホール25と、絶縁ベース材11の表面に形成されたランド部30と、絶縁ベース材11の裏面に形成されたランド部17bと、ランド部30とランド部17bを接続する層間導電路29a、及びランド部31とランド部17bを接続する層間導電路29bを有するステップビア29とを備える。出発材料の可撓性ベース材料のロール方向に対する上穴26と下穴27の径の差が、前記ロール方向と垂直な方向に対する上穴26と下穴27の径の差よりも大きい。

(もっと読む)

配線基板

【課題】電源ビアの抵抗を上げることなく、配線の設計自由度が高く、インピーダンスマッチングを良好に取ることが可能な配線基板を提供する。

【解決手段】配線基板1は、少なくとも1つの信号層10Sと、少なくとも1つのグランド層10Gと、少なくとも1つの電源層10Vと、半導体素子チップが実装される一方の基板面21上の配線31と他方の基板面22上の配線32と電源層10Vとを電気的に導通する少なくとも1つの電源ビア40Vと、複数の半導体素子チップ間の信号伝送がなされる信号配線とを備え、電源層10Vが信号配線より一方の基板面21側に設けられたものである。電源ビア40Vは、一方の基板面21から電源層10Vまで形成された相対的に孔径の大きい大孔径部41Vと、電源層10Vから他方の基板面22まで形成された相対的に孔径の小さい小孔径部42Vとからなる。

(もっと読む)

多層セラミック基板及びその製造方法

【課題】層間接続導体部の近傍にクラックが発生することを抑制し、基板の破壊を防止して、突出部材の接合強度を高めることができる多層セラミック基板及びその製造方法を提供する。

【解決手段】スタッド23の底面の外周におけるロウ材層59の外接円と、最表面の低温焼成セラミック層において表面金属層57の周りに配置されるビア55の面積中心との間の距離Zが2.5mm以上、スタッド23の底面の面積中心を中心にして、表面金属層57の半径方向の長さMLと、ロウ材層59の底面の同じ半径方向の長さRLとの差(ML−RL)がスタッド23の外周の全周にわたり0.65mm以上、スタッド23の底面の面積中心を中心にして、スタッド23に最も近いビア55の面積中心までの半径方向における長さVLとスタッド23の底面の同じ半径方向における長さSLとの比(VL/SL)が1.6〜2.0である。

(もっと読む)

配線基板

【課題】信号配線に例えば2.5GHzを超える高速信号を低損失で良好に伝送させることが可能であるとともに、良好な電源供給が可能な配線基板を提供すること。

【解決手段】外周部および中央部に多数のスルーホール5を有するコア基板1の上下面にビルドアップ絶縁層2を介して信号配線および接地配線および電源配線を含むビルドアップ配線層3を積層してなる配線基板であって、前記外周部に小径スルーホール5Sを第1の隣接間隔で配列するとともに前記中央部に大径スルーホール5Lを前記第1の隣接間隔以下の第2の隣接間隔で配置し、小径スルーホール5Sに信号線を接続するとともに大径スルーホール5Lに接地配線および電源配線を接続した。

(もっと読む)

回路基板の製造方法

【課題】高密度な配線パターンを形成して、確実に導電性ペーストによる層間接続を行うことができる回路基板の製造方法を提供する。

【解決手段】基板11の一方の側の銅箔12の表面にマスキングテープ15を貼り付ける。マスキングテープ15及び銅箔12に開口部15a,12aを形成し、開口部12aに連通して、基板11にビアホール16を形成する。ビアホール16内に導電性ペースト18を充填し、マスキングテープ15を剥離して、導電性ペースト18を熱プレスする。ビアホール16の導電性ペースト18を押圧してリベット状に形成し、表面にエッチングレジスト19aを設ける。ビアホール16上のエッチングレジスト19aの大きさを、銅箔12による所望のランド部20の大きさよりも小さく形成する。エッチング時に、ビアホール16周辺の広がり部18aについて、その周縁部をエッチングにより除去するとともに、一部を残してエッチングを終了する。

(もっと読む)

積層型電子部品

【課題】直流抵抗を下げつつも、接続導体がコイルの内周側の領域に入り込むことを抑制し、信頼性が向上された積層型電子部品を提供する。

【解決手段】引出導体用スルーホール導体71に比して、第一並列接続用スルーホール導体65の直径を大きくすることで、第一並列接続用スルーホール導体65を、積層圧着時に引出導体用スルーホール導体71の食い込みを受け止める支持部材として機能させる。これによって、第一接続導体21の導体端部21b及び第二接続導体23の導体端部23bの沈みを抑制する。更に、第一並列接続用スルーホール導体65が第二接続導体23の導体端部23bに対して当接する部分の面積を大きくすることによって導体端部23bに作用する圧力を分散させる。従って、第二接続導体23の導体端部23bに対する第一並列接続用スルーホール導体65の食い込み量を低減する。

(もっと読む)

コア基板のキャビティ加工方法

【課題】コア基板のキャビティ加工方法を提供する。

【解決手段】本発明に係るコア基板のキャビティ加工方法は、コア基板の一面に回路パターンにより区画される第1加工領域を形成する工程と、コア基板の他面に回路パターンにより区画される第2加工領域を形成する工程と、コア基板の一面から第1加工領域を全て除去してキャビティを加工する工程と、を含む。

(もっと読む)

1 - 20 / 86

[ Back to top ]