Fターム[5E346FF01]の内容

多層プリント配線板の製造 (97,916) | 導体層間接続の方法 (9,115) | 孔あけによるもの(スルーホール等) (5,634)

Fターム[5E346FF01]の下位に属するFターム

Fターム[5E346FF01]に分類される特許

801 - 812 / 812

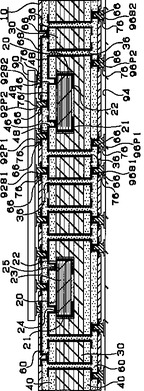

プリント配線板及びプリント配線板の製造方法

【課題】 ループインダクタンスを低減できるプリント配線板及び該プリント配線板の製造方法を提供する。

【解決手段】 プリント配線板10内にチップコンデンサ20を配置するため、ICチップ90とチップコンデンサ20との距離が短くなり、ループインダクタンスを低減することができる。また、厚いコア基板30内にチップコンデンサ20を収容するためプリント配線板を厚くすることがない。

(もっと読む)

プリント配線板及びプリント配線板の製造方法

【課題】 ループインダクタンスを低減できるプリント配線板及び該プリント配線板の製造方法を提供する。

【解決手段】 プリント配線板10内にチップコンデンサ20を配置するため、ICチップ90とチップコンデンサ20との距離が短くなり、ループインダクタンスを低減することができる。また、厚いコア基板30内にチップコンデンサ20を収容するためプリント配線板を厚くすることがない。

(もっと読む)

プリント配線板及びプリント配線板の製造方法

【課題】 ループインダクタンスを低減できるプリント配線板及びプリント配線板の製造方法を提供する。

【解決手段】 プリント配線板10内にチップコンデンサ20Aを配置するため、ICチップ90とチップコンデンサ20Aとの距離が短くなり、ループインダクタンスを低減することができる。また、厚いコア基板30内にチップコンデンサ20A、チップ抵抗20Bを収容するためプリント配線板を厚くすることがない。コア基板30内にチップ抵抗20Bを収容するため、プリント配線板の高集積化を実現できる。

(もっと読む)

プリント配線板及びプリント配線板の製造方法

【課題】 ループインダクタンスを低減できるプリント配線板及びプリント配線板の製造方法を提供する。

【解決手段】 プリント配線板10内にチップコンデンサ20Aを配置するため、ICチップ90とチップコンデンサ20Aとの距離が短くなり、ループインダクタンスを低減することができる。また、厚いコア基板30内にチップコンデンサ20A、チップ抵抗20B、チップコイル20Cを収容するためプリント配線板を厚くすることがない。コア基板30内にチップ抵抗20B、チップコイル20Cを収容するため、プリント配線板の高集積化を実現できる。

(もっと読む)

多層プリント基板

【課題】プリント基板内の電源層及びグラウンド層間で生じる共振の抑制、さらに該共振に起因する放射ノイズを低減することが可能な多層プリント基板を提供する。

【解決手段】 本発明に係る多層プリント基板は、電源層1c、該電源層1cと通電し得るグラウンド層1b及び信号ライン層1a及び1dから構成され、前記信号ライン層1d上に形成された信号ライン3に接続されるドライバ側回路素子あるいはレシーバ側回路素子の少なくともいずれかの回路素子2を搭載したものであって、前記電源層1cの少なくともその一部は網目状のパターンで構成されることを特徴とする。また、前記回路素子2の電源端子は、EMIフィルタを介して前記電源層1cに接続されることを特徴とする。

(もっと読む)

高周波半導体装置及びその装置を用いた無線装置

【課題】 フリップチップ実装した高周波回路チップの特性劣化を防止すると共に、低損失を実現できる高周波半導体装置及びその装置を用いた無線装置を提供する。

【解決手段】シリコン基板11上に誘電体薄膜層13を積層してなる実装基板10を設ける。前記実装基板10のシリコン基板11にエッチング孔部18を設ける。前記シリコン基板11に接する誘電体薄膜層13に接地用導体層12を形成する。前記誘電体薄膜層13の上面にマイクロストリップ線路部(伝送線路部)14を形成する。前記マイクロストリップ線路部14上にバンプ16を介してフリップチップ実装し、エッチング孔部18に対応する位置に高周波回路チップ15を配置した。

(もっと読む)

多層プリント配線板及び多層プリント配線板の製造方法

【課題】 スルーホールの配設密度を高め得ると共に、厚みを薄くできる多層プリント配線板及び該多層プリント配線板の製造方法を提供する。

【解決手段】 コア基板30に形成されたスルーホール36は、第1電解めっき層24と、無電解めっき膜26と、第2電解めっき層28とからなる。スルーホール36をめっき充填により形成するため、コア基板30の強度が高まり、反りが発生し難くなる。このため、コア基板を薄く形成でき、多層プリント配線板の放熱性を高めることが可能となる。

(もっと読む)

多層プリント配線板およびその放熱構造

【課題】 集積回路からの熱を空気中に放熱する熱伝導経路を確保する。

【解決手段】 集積回路1と表面面状導体8との間に熱伝導性介在物10を注入して充填するための1つ以上の注入穴3と、注入穴3から注入された熱伝導性介在物10が必要な領域に拡がっていることを確認する充填状態確認穴4と、集積回路1から表面面状導体8に伝導された熱を内層面状導体17に伝導するスルーホール7とを備え、さらに、集積回路1を実装する箇所とは別の箇所の外層に配置され、熱を空気中に放熱する放熱用面状導体20と、放熱用面状導体20と内層面状導体17とを熱的に接続するスルーホール19とを備え、集積回路1の実装後に、熱伝導性介在物10を、集積回路1との隙間に充填することができると共に、集積回路1からの熱を内層面状導体17に伝熱することができる。

(もっと読む)

差動平衡信号伝送基板

【課題】 接地用配線や電源用配線と、信号線との物理的な配置を考慮することにより、クロストークが抑制されると共に、インピーダンスが所定の範囲に制御された差動平衡信号伝送基板を提供する。

【解決手段】 +線102aおよび−線102bによって構成される差動平衡信号線対同士の間に、接地用配線103を配置する。

(もっと読む)

プリント配線板及びその製造方法並びにプリント配線板におけるコネクタインダクタンス要因の波形歪み低減法

【課題】 低コストにて高周波特性の改善を実現することの可能なスルーホール構造を有するプリント配線板を提供し、プリント配線板と接続されるコネクタのインダクタンス要因により伝送信号に発生する波形歪みをプリント配線板において低減する方法を提供する。

【解決手段】 基板6にグランド配線5と信号配線4とが形成され、信号配線4には信号配線用スルーホール2が接続され、信号配線用スルーホール2の周囲には信号配線用スルーホール2と平行に配列された複数のグランド配線用スルーホール1が形成され、グランド配線用スルーホール1はグランド配線5と接続されている。グランド配線用スルーホール1の数を増減することにより信号配線用スルーホール2とグランド配線用スルーホール1との間に形成される容量の値を調整し、コネクタ7とプリント配線板との間のインピーダンス整合をとる。

(もっと読む)

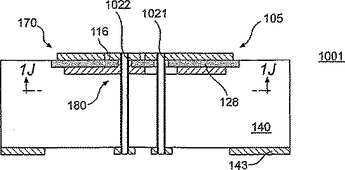

低インダクタンス埋め込みキャパシタを有するプリント配線板およびその製造方法

プリント配線板(PWB)は、受動回路素子(105)からなる積み重ねられた中間層パネル(1001、1002、1003、...)を有する。受動素子(105)は、電極終端がキャパシタ電極(170、180)のフットプリント内に位置付けられるキャパシタを含むことができる。したがってキャパシタ終端が、狭い間隔で離間して配置されるため、中間層内のループ・インダクタンスに対するキャパシタの寄与が減る。また電極フットプリント内にキャパシタ終端があることによって、キャパシタを形成する際に用いられるPWBボード表面積が減る。キャパシタ終端は、回路導体(1021、1022)によって接続される。  (もっと読む)

(もっと読む)

積層型ビア構造体

【課題】 高速信号の搬送や高密度電流の伝達に適合した積層型ビア構造体を提供する。

【解決手段】 電子装置キァリアの導電層を通して高周波信号または高密度電流を伝送しうるように適合した積層型ビア構造体(200)を開示する。この積層型ビア構造体はz軸を基準にして位置合わせされ誘電体層(120)によって分離された隣接する3つの導電層(110a、110b、110c)に属す少なくとも3つの導電路(205a、205b、205c)を備えている。これら導電路間の接続は各導電層間に配置された少なくとも2つのビア(210、215)を用いて行なわれている。導電路の一側に接続されたビアは反対側に接続されたビアとはz軸を基準にして位置合わせされない状態で配置されている。好適な実施形態では、これら位置合わせされた導電路の形状はディスクまたは環状リングのように見える。4つのビアを用いて隣接する2つの導電層を接続している。これら4つのビアは前記導電路の各々に対称的に配置されている。隣接する第1の導電層と第2の導電層との間に設けられたビアの位置と、隣接する第2の導電層と第3の導電層との間に設けられたビアの位置とはz軸を基準にして45°の角度をなしている。

(もっと読む)

801 - 812 / 812

[ Back to top ]