Fターム[5F003AP04]の内容

バイポーラトランジスタ (11,930) | 目的 (494) | 誤動作、寄生効果、表面リークの防止 (62)

Fターム[5F003AP04]に分類される特許

1 - 20 / 62

電子装置

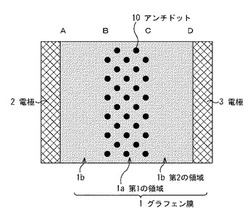

【課題】カーボンによるバンドギャップ・エンジニアリングを可能とし、カーボン原子に基づく多彩なエレクトロニクスを達成して、信頼性の高い電子装置を実現する。

【解決手段】電子装置は、単層のグラフェン膜1と、グラフェン膜1上の両端に設けられた一対の電極2,3とを有しており、グラフェン膜1では、電極2,3間の領域において、中央部位のBC間が複数のアンチドット10が形成されてなる第1の領域1aとされており、第1の領域1aの両側におけるAB間及びCD間がアンチドットの形成されていない第2の領域1bとされている。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】コレクタメサ表面で発生するコレクタリーク電流を抑制し、微細なHBTのコレクタ耐圧特性を改善する。

【解決手段】第2サブコレクタ層103は、第1サブコレクタ層102より平面視で小さい面積に形成されている。また、コレクタ層104は、第2サブコレクタ層103を構成している半導体層132より平面視で大きい面積に形成されている。また、ベース層105は、コレクタ層104より平面視で小さい面積に形成されている。また、エミッタ層106は、ベース層105より平面視で小さい面積に形成されている。加えて、第2サブコレクタ層103を構成している半導体層132およびベース層105は、平面視でコレクタ層104の内側の領域に形成されている。

(もっと読む)

トランジスタ素子

【課題】n型不純物としてTeを用いたノンアロイ層を有していても、ベース電流、コレクタ電流のリーク電流が少ないトランジスタ素子を提供する。

【解決手段】基板11と、基板11上に設けられた高電子移動度トランジスタ構造層28と、高電子移動度トランジスタ構造層28上に設けられたヘテロバイポーラトランジスタ構造層29とを備えたトランジスタ素子10において、ヘテロバイポーラトランジスタ構造層29のノンアロイ層26,27は、n型不純物としてTeがドーピングされており、n型不純物濃度が1.0×1019cm-3以上2.0×1019cm-3以下にされているものである。

(もっと読む)

電流値依存性の少ない増幅率を有する半導体デバイス

【課題】本発明は、数桁のレベルで変化する電流を、複雑な回路を使わないで一定の増幅率で増幅することを課題とする。

【解決手段】本発明ではこの課題を解決するために、第1導電形の第1半導体領域と、該第1半導体領域に接して設けられた逆導電形の第2半導体領域と、該第2表面で該第2半導体領域と接して設けられた第1導電形の第3半導体領域とを有する半導体デバイスにおいて、該第2半導体と接して該第3半導体領域を離間して囲む該第2半導体領域より高不純物濃度の

第4半導体領域を更に設ける。

(もっと読む)

半導体装置及び電力増幅器

【課題】トランジスタの占有面積をほとんど増やすことなく、かつ、HBTとHFETとを接続する配線による悪影響を受けないBi−HFET(半導体装置)を提供する。

【解決手段】基板101上に形成されたHFET160と、HFET160上に形成されたHBT170とを備え、HFET160は、チャネル層102と、コンタクト層104とを有し、HBT170は、HFET160のコンタクト層104と接続、又は、一体化されたサブコレクタ層107と、コレクタ層108と、ベース層109と、エミッタ層110と、エミッタキャップ層111と、エミッタコンタクト層112とを有し、コレクタ層108、ベース層109及びエミッタ層110は、メサ形状の構造体であるベースメサ領域830を構成し、ゲート電極202は、第一のコレクタ電極203とベースメサ領域830との平面的な間に設けられたリセス領域820内に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】埋め込み絶縁層により活性層と支持基板とが電気的に絶縁された半導体基板において、支持基板の電位を活性層の表面から取り出すための基板コンタクトの低抵抗化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】活性層16に素子領域4およびコンタクト領域5が形成された厚膜SOI基板2において、CMOSトランジスタ7のB/L層29およびL/I層37、npnバイポーラトランジスタ8のコレクタ層49と同一層に、n型基板コンタクト12の貫通コンタクト58を取り囲むn型コンタクト埋め込み層57を形成する。

(もっと読む)

半導体装置

【課題】デバイスサイズの縮小、シリーズ抵抗の低減、及びリーク電流の抑制を可能とする半導体装置を提供することを目的とする。

【解決手段】本発明は、デバイス動作にとって、本来は不要な電位段差を発生させる層をデバイスの構造内にあえて挿入したものである。この電位段差は、バンドギャップの小さな半導体がメサ側面に露出しても、その部分の電位降下量を抑制し、デバイス動作に不都合なリーク電流を低減できる、という機能をもたらす。この効果は、ヘテロ構造バイポーラトランジスタ、フォトダイオード、及び電界吸収形光変調器などに共通して得られる。また、フォトダイオードにおいては、リーク電流が緩和されるのでデバイスのサイズを縮小することが可能となり、シリーズ抵抗の低減による動作速度の改善のみならず、デバイスを高密度にアレイ状に配置できるという利点も生まれる。

(もっと読む)

バイポーラ半導体素子

【課題】表面欠陥を低減でき、オン電圧ドリフトを抑制できるバイポーラ半導体素子を提供する。

【解決手段】このSiC GTOによれば、メサ状のp型アノードエミッタ層5の長側面5Bが延在している方向を、〈11−20〉方向としたオフ方向から角度φ=60°だけ傾斜させた方向とした。これにより、長側面5Bは、{01−10}面となり、{11−20}面である短側面5Cに比べて、表面欠陥が入りにくくなる。また、長側面5Bの延在方向を、上記オフ方向から角度φ=60°だけ傾斜させたことで、長側面5Bの延在方向とオフ方向とが一致している場合(φ=0°)に比べて、メサ状のp型アノードエミッタ層5の長側面5Bに現れる{0001}面の層の数を減らすことができて、{0001}面の層内に入る表面欠陥を減少できる。

(もっと読む)

バイポーラ半導体素子

【課題】ドリフト層とドリフト層に隣接する層との界面の応力を低減して、順方向電圧を低く抑えることができるバイポーラ半導体素子を提供する。

【解決手段】このpinダイオード20は、n型SiCドリフト層23の膜厚の各範囲(300μm以下200μm超),(200μm以下100μm超),(100μm以下50μm超)に対応して、n型SiCバッファ層22の不純物濃度の各上限値(5×1017cm−3),(7×1017cm−3),(10×1017cm−3)が設定されている。これにより、n型SiCドリフト層23とn型SiCバッファ層22との界面の応力を低減でき、順方向電圧を低減できる。

(もっと読む)

半導体装置

【課題】支持基板に接地電極を備えることなく、第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供する。

【解決手段】支持基板10を、第1導電型領域10aと第2導電型領域10bとを有し、第1素子形成領域20にノイズが印加されてノイズが伝播されたときの当該ノイズの伝播経路中に、第1、第2導電型領域10a、10bで構成されるPNP接合またはNPN接合を有するものとする。このような半導体装置では、PNP接合またはNPN接合の間に構成される空乏層により、第1、第2素子形成領域20、30の間でノイズが伝播することを抑制することができる。

(もっと読む)

バイポーラ半導体素子

【課題】高温や電流密度が高い条件下でも基板へ少数キャリアが到達するのを防いで、順方向電圧の増大を防ぐことができるバイポーラ半導体素子を提供する。

【解決手段】このSiC pinダイオード20では、n型SiC基板21とn型のドリフト層23との間に形成されている厚さを20μmとしたn型のバッファ層22が、p型のアノード層24,25からの正孔のトラップとして働いて、正孔(少数キャリア)がn型SiC基板21へ到達することを防ぐ。これにより、正孔(少数キャリア)がn型SiC基板21へ到達することを防いで、n型SiC基板21から積層欠陥が拡大するのを防いで、順方向電圧の増大を防止できる。

(もっと読む)

半導体装置

【課題】III-V族窒化物半導体に設けるオーミック電極のコンタクト抵抗を低減しながらデバイスの特性を向上できるようにする。

【解決手段】半導体装置(HFET)は、SiC基板11上にバッファ層12を介在させて形成された第1の窒化物半導体層13と、該第1の窒化物半導体層13の上に形成され、該第1の窒化物半導体層13の上部に2次元電子ガス層を生成する第2の窒化物半導体層14と、該第2の窒化物半導体層14の上に選択的に形成されたオーム性を持つ電極16、17とを有している。第2の窒化物半導体層14は、底面又は壁面が基板面に対して傾斜した傾斜部を持つ断面凹状のコンタクト部14aを有し、オーム性を持つ電極16、17はコンタクト部14aに形成されている。

(もっと読む)

バイポーラトランジスタおよびその製造方法

【課題】HBTの高速性および信頼性が向上できるようにする。

【解決手段】エミッタメサの部分の側面およびレッジ構造部105aの表面には、これらを被覆するように、窒化シリコン(SiN)からなる第1絶縁層108が形成されている。また、第1絶縁層108の周囲からベース電極111の上面にかけて(渡って)窒化シリコンからなる第2絶縁層109が形成されている。第2絶縁層109は、第1絶縁層108の側面、レッジ構造部105aとベース電極111との間のベース層104の上、およびベース電極111の上面を覆うように形成されている。基板101の平面方向において、レッジ構造部105aの外形は第1絶縁層108の外形と同じに形成されている。また、エミッタメサより離れる方向のベース電極111の外周部分が、第1絶縁層108の外周部分に重なって形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】結晶欠陥による接合リークを防止しながら、バイポーラトランジスタの面積を縮小し、コレクタ容量の低減によってトランジスタ特性を向上できるようにした半導体装置及びその製造方法を提供する。

【解決手段】活性領域1からSTI4上にかけて連続して形成したSiGe膜は、半導体基板3上ではSiGeエピ膜6となり、STI4上ではSiGeポリ膜7となる。半導体基板3とSTI4の境界はSiGe−HBT形成工程以前の洗浄工程によって段差15が生じており、SiGeエピ膜6及び半導体基板3には、上記境界を基点とした結晶欠陥が応力によって発生する可能性がある。この境界に第1のP型不純物層8及び第2のP型不純物層9を設けることで、結晶欠陥をこれらP型不純物層8、9に内包し、接合リークの発生を抑制する。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSプロセスへの導入が容易で、エミッタ−ベース間のリーク電流(電界強度)を低減し、ノイズやサージ電圧の影響を受けにくい高性能な半導体装置とその製造方法の提供。

【解決手段】導電膜をマスクとして、2回のイオン注入を行ってエミッタを形成する。第2エミッタ領域111bは、低濃度の不純物イオン注入によって形成し、第1エミッタ領域111aは、高濃度の不純物イオン注入によって形成する。その結果、エミッタの周縁部に低濃度の第2エミッタ領域が形成され、電界が緩和され、リーク電流が低減する。また、導電膜とエミッタ電極116とが接続され、ノイズの影響を受けにくくなる。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製法

【課題】高い電流増幅率を有し、高周波特性および素子寿命に優れたヘテロ接合バイポーラトランジスタおよびその製法を提供すること。

【解決手段】半絶縁性基板1上に、n型半導体より成る真性エミッタ層16と、p型ドーパントを高濃度でドーピングされ、真性エミッタ層16よりも狭いバンドギャップを有する半導体より成るベース層9と、ベース層9と同じ半導体より成るコレクタ層10とを、この順序で積層して成るへテロ接合バイポーラトランジスタにおいて、真性エミッタ層16の周囲に、高抵抗領域15が設けられ、高抵抗領域15と真性エミッタ層16との間に、真性エミッタ層16の半導体と同じ半導体から成るガードリング領域17が設けられ、真性エミッタ層16とベース層9との接合面が、ガードリング領域17の上面よりも下に位置することを特徴とするヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

半導体基板、電子デバイス、半導体基板の製造方法及び電子デバイスの製造方法

【課題】半導体基板、電子デバイス、半導体基板の製造方法及び電子デバイスの製造方法を提供する。

【解決手段】シリコンに不純物原子が導入された不純物領域104を有するベース基板102と、不純物領域104に接して設けられている複数のシード体112と、複数のシード体112の各々に接して設けられ、複数のシード体112の各々とそれぞれ格子整合または擬格子整合する複数の化合物半導体114とを備える半導体基板100。当該半導体基板100は、ベース基板102上に設けられ、不純物領域104の少なくとも一部を露出する複数の開口が設けられた阻害体をさらに備えてもよい。

(もっと読む)

半導体基板、半導体基板の製造方法、および電子デバイス

【課題】同一基板に形成されるHBTとFETとの相互影響を低減する。

【解決手段】第1半導体と、第1半導体の上方に形成された第2半導体とを備え、第2半導体は、P型の伝導型を示す不純物またはN型の伝導型を示す第1不純物原子と、第2半導体が第1不純物原子を有する場合のフェルミ準位を、第2半導体が第1不純物原子を有しない場合のフェルミ準位に近づける第2不純物原子とを有する半導体基板を提供する。一例として、当該第2半導体の多数キャリアは電子であり、第2不純物原子は、第1不純物原子を有する第2半導体のフェルミ準位を下降させる。第2半導体は3−5族化合物半導体であり、第2不純物原子が、ベリリウム、ボロン、炭素、マグネシウム、および亜鉛からなる群から選択された少なくとも1つであってもよい。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】エミッタ電子輸送特性やエミッタ注入効率を劣化させることなく、レッジ部を薄層化することが容易で、微細化に適したヘテロ接合バイポーラトランジスタを提供すること。

【解決手段】エミッタ層は、第1の半導体層11と、第2の半導体層12と、第3の半導体層13との積層構造からなり、第3の半導体層13は、第2の半導体層12に対してウェット・エッチングにより選択的に除去でき、第2の半導体層12は、第1の半導体層11に対してウェット・エッチングにより選択的に除去でき、第1の半導体層11と第3の半導体層13のバンドギャップはベース層4のバンドギャップよりも大きく、第2の半導体層12は不純物添加によって縮退しており、第3の半導体層13は不純物添加によって中性領域を形成しているヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】単一半導体基板上にHBTおよびFETのような複数異なる種類のデバイスを形成するに適した半導体基板を製造する方法を提供する。

【解決手段】半導体を結晶成長させる反応容器内に第1不純物原子を構成要素として有する単体または化合物を含む第1不純物ガスを導入する段階を含む複数の段階を繰り返して、複数の半導体基板を製造する方法であって、第1不純物ガスを導入する段階の後に、製造された半導体基板を取り出す段階と、反応容器内に第1半導体を設置する段階と、反応容器内に、第1半導体内で第1不純物原子と反対の伝導型を示す第2不純物原子を構成要素として有する単体または化合物を含む第2不純物ガスを導入する段階と、第1半導体を第2不純物ガスの雰囲気中で加熱する段階と、加熱した前記第1半導体上に第2半導体を結晶成長させる段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

1 - 20 / 62

[ Back to top ]