Fターム[5F003BB05]の内容

バイポーラトランジスタ (11,930) | ベース (1,440) | ベース抵抗 (264)

Fターム[5F003BB05]の下位に属するFターム

グラフトベース (114)

Fターム[5F003BB05]に分類される特許

1 - 20 / 150

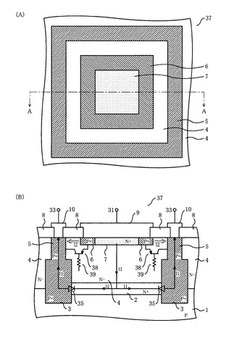

半導体装置

【課題】所望のブレークダウン電圧が確保でき、大きな放電電流を流すことが可能なESD保護特性のすぐれたESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3でPN接合ダイオード35を形成する。P+型埋め込み層3はP+型引き出し層5と一体となりN−型エピタキシャル層4を貫通させアノード電極10と接続される。P+型埋め込み層3等で囲まれたN−型エピタキシャル層4にN+型拡散層7と該N+型拡散層7と接続され、これを取り囲むP+型拡散層6を形成する。N+型拡散層7、P+型拡散層6はカソード電極9に接続される。P+型拡散層6をエミッタ、N−型エピタキシャル層4をベース、P+型引き出し層5等をコレクタとする寄生PNPバイポーラトランジスタ38とPN接合ダイオード35でESD保護素子を構成する。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3で形成するPN接合ダイオード35と、P型拡散層6と接続するP+型埋め込み層3aをエミッタ、N−型エピタキシャル層4をベース、P+型埋め込み層3をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構築する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それを取り囲むN+型拡散層7はカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、その放電電流I1によりP+型埋め込み層3よりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし大きな放電電流I2が流れる。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3からなるPN接合ダイオード35と、P+型拡散層6と繋がるP+型引き出し層5aをエミッタ、N−型エピタキシャル層4をベース、P型半導体基板1をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構成する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それと接続され、取り囲むN+型拡散層7とはカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、そのときの放電電流I1によりP+型引き出し層5aよりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし、大きな放電電流I2が流れる。

(もっと読む)

半導体素子の製造方法、ESD保護素子の製造方法

【課題】半導体ウエハに厚みばらつきがある前提で、コストアップをすることなく高品質の半導体素子を提供すること。

【解決手段】第1導電型の活性層の下に第1導電型の埋込拡散層を有する半導体基板を準備するステップと、活性層と埋込拡散層の総厚を測定し、測定した総厚から前記活性層の厚さを求めるステップと、活性層に、埋込拡散層との間で電流が流れる第1導電型のコレクタ領域をイオン注入によって形成するステップと、活性層に、埋込拡散層との間で電流が流れる第2導電型のベース領域をイオン注入によって形成するステップと、ベース領域内に、ベース領域との間で電流が流れる第1導電型のエミッタ領域をイオン注入によって形成するステップとを備え、ベース領域を形成するステップは、活性層の厚さに応じてイオン加速エネルギーを変化させるステップであることを特徴とする。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】GaAsSb系の化合物半導体のベース層を有するInP系HBTで、大きな電流利得が得られるようにする。

【解決手段】コレクタ層102の上に形成されてGa,As,およびSbから構成された化合物半導体からなるベース層103と、ベース層103の上に接して形成されたスペーサ層104と、スペーサ層104の上に接して形成されてInおよびPから構成された化合物半導体からなるエミッタ層105とを備える。スペーサ層104は、ベース層103の伝導帯端のエネルギー準位よりも低く、エミッタ層105の伝導帯端よりも高い伝導帯端のエネルギー準位を有し、ベース層103の価電子帯端のエネルギー準位よりも低く、エミッタ層105の価電子帯端よりも高い価電子帯端のエネルギー準位を有した状態で、ベース層103およびエミッタ層105に接して形成されている。

(もっと読む)

半導体装置

【課題】ホールド電圧を変化させずに、トリガー電圧のみを調節することができるようにする。

【解決手段】本実施形態における保護素子10は、低濃度コレクタ層102、シンカー層110、高濃度コレクタ層112、エミッタ層130、高濃度ベース層122、ベース層120、第1導電型層140、及び第2導電型層150を有している。第2導電型層150は低濃度コレクタ層102に形成されており、ベース層120と第1導電型層140の間に位置している。第2導電型層150は低濃度コレクタ層102よりも不純物濃度が高い。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を増加させることなく、ESD保護素子としてのLDMOSトランジスタのスナップバック電圧をESD被保護素子としてのLDMOSトランジスタのスナップバック電圧より低くし、且つESD保護素子としてのLDMOSトランジスタの熱破壊電流値をスナップバック電圧の改善前より大きくする。

【解決手段】 ESD保護素子としてのLDMOSトランジスタ32は、N型エピタキシャル層3と、N+型埋め込み層2と、N型エピタキシャル層3の表面に形成されたドリフト層11と、エピタキシャル層3の表面に形成されたP型のボディ層10と、Pボディ層10の表面に形成されたN+型ソース層14と、エピタキシャル層3の表面上に形成されたゲート絶縁膜5、6と、ゲート絶縁膜5、6上に形成されたゲート電極8と、を具備し、N+型ソース層14の下方のボディ層10の底部にP型ボディ層窪み部10aが形成されている。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

バイポーラトランジスタ

【課題】高速動作性・高電流駆動力を有するヘテロ接合バイポーラトランジスタ及びその製造方法を提供する。

【解決手段】バイポーラトランジスタは、コレクタとして機能するSi単結晶層3と、Si単結晶層3の上に形成された単結晶のSi/SiGeC層30a及び多結晶のSi/SiGeC層30bと、エミッタ開口部を有する酸化膜31と、エミッタ電極50と、エミッタ層35とを備えている。単結晶のSi/SiGeC層30aに真性ベース層52が形成され、単結晶のSi/SiGeC層30aの一部と多結晶のSi/SiGeC層30bとCoシリサイド層37bとにより、外部ベース層51が構成されている。エミッタ電極の厚みは、エミッタ電極50に注入されたボロンがエミッタ電極50内を拡散して、エミッタ−ベース接合部まで達しないように設定されている。

(もっと読む)

トレンチにより制限された分離拡散領域を備えた相補型アナログバイポーラトランジスタ

【課題】表面上に素子をより高密度に実装する。

【解決手段】第1のトレンチと第2のトレンチとの間の位置において、エピタキシャル層の表面から基板へと下方に延在するドーパントのウェルは、エピタキシャル層の背景ドーピング濃度とは異なるドーピング濃度を有し、エピタキシャル層の残りの部分と第1および第2の接合を形成する。第1の接合は、第1のトレンチの底部から基板に延在し、第2の接合は、第2のトレンチの底部から前記基板に延在する。ウェルおよび第1および第2のトレンチは分離構造を構成し、分離構造は、分離構造の一方側のエピタキシャル層に形成された第1の素子と分離構造の他方側のエピタキシャル層に形成された第2の素子とを電気的に分離する。分離構造による電気的分離は第1および第2のトレンチとPN接合とによってもたらされ、ウェルは第1の導電型の材料でドープされ、基板およびエピタキシャル層は、第1の導電型とは反対の第2の導電型の材料でドープされ、第1および第2の接合はPN接合である。

(もっと読む)

参照電圧発生回路および受信回路

【課題】 電源電圧依存性および温度依存性の低い参照電圧発生回路を提供し、もって受信感度の良好な受信回路を実現する。

【解決手段】 受信回路は、AMI符号化された一対の信号を増幅する差動増幅回路(11)と、差動増幅回路の出力と所定の参照電圧とを比較して入力信号の論理レベルを判別する受信データ判定回路(12)と、前記参照電圧を発生する参照電圧発生回路(13)とを備え、参照電圧発生回路は電源電圧を基準にした温度依存性の低い参照電圧を発生するように構成した。

(もっと読む)

半導体基板、電子デバイスおよび半導体基板の製造方法

【課題】エピタキシャル成長により形成された結晶膜の成長面内における物性値を均一な値に近づける。

【解決手段】第1化合物半導体および第2化合物半導体を積層した積層半導体を含み、前記第1化合物半導体の所定物性値が第1面内分布を有し、前記第2化合物半導体の前記所定物性値が前記第1面内分布とは異なる第2面内分布を有し、前記積層半導体における前記所定物性値の面内分布の幅が、前記第1面内分布の幅または前記第2面内分布の幅より小さい半導体基板を提供する。

(もっと読む)

半導体装置

【課題】電力破壊を抑制できる半導体装置を提供すること。

【解決手段】ベース領域12の表面に設定されたベースコンタクト領域14において、ベース電極15がベース領域12に接合されている。ベースコンタクト領域14の境界部の下方には、エミッタ領域13と同じ導電型を有するN型領域21がベースコンタクト領域14を包囲するように形成されている。言い換えれば、ベースコンタクト領域14の境界部の下方において、P型のベース領域12およびN型領域21によりPN型の寄生ダイオードが形成されている。

(もっと読む)

有機トランジスタ、回路素子及びそれらの製造方法

【課題】低電圧で作動するとともに大きなベース電圧を印加した場合でも耐電圧が高く、各種の回路素子への応用が容易で、製造コストを抑えた有機トランジスタ及び回路素子を提供する。

【解決手段】コレクタ電極1とエミッタ電極2と両電極間に設けられた有機半導体層3と有機半導体層3内に設けられたベース電極4とを有する縦型トランジスタ部、及び、ベース電極4とベース電圧電源端子7との間に設けられた抵抗部6、を有する。抵抗部6は、コレクタ電極1と同じ材料からなりベース電圧電源端子7に接続する第1電極21と、エミッタ電極2と同じ材料からなりベース電極4に接続する第2電極22と、有機半導体層3と同じ材料からなり第1電極21及び第2電極22間に挟まれた抵抗層24とを有する。

(もっと読む)

半導体装置の製造方法及び半導体集積回路装置

【課題】本発明は、簡素な工程で、デバイスの特性を均一化することができる半導体装置の製造方法及び半導体集積回路装置を提供することを目的とする。

【解決手段】半導体基板40の表面の所定領域41に、LOCOS酸化膜70を形成するLOCOS酸化膜形成工程と、

該LOCOS酸化膜70と前記半導体基板40の表面の境界を覆うように、ポリシリコン膜90を形成するポリシリコン形成工程と、

該ポリシリコン膜90をマスクとして、前記半導体基板40の表面にイオンの打ち込みを行い、前記半導体基板40の表面に、不純物領域60を形成するイオン打ち込み工程と、を含むことを特徴とする。

(もっと読む)

ESD保護素子

【課題】ESD耐量及びノイズ耐性を向上させたESD保護素子を提供する。

【解決手段】本発明によるESD保護素子は、NPNバイポーラトランジスタTr1と、一端がパッド10に接続されたトリガ素子20とを具備する。NPNバイポーラトランジスタTr1は、第1ベース拡散層204と、パッド10に接続されたコレクタ拡散層4と、第1ベース拡散層204上に形成され、第1配線L1を介してトリガ素子20の他端に接続されたトリガタップ1と、第1ベース拡散層204上に形成され、第1配線L1と異なる第2配線L2を介してGNDに共通接続されたエミッタ拡散層2及び第2ベース拡散層3とを備える。

(もっと読む)

アバランシェ機能を有する高降伏電圧広バンドギャップMOSゲートバイポーラ接合トランジスタ

第1のコレクター、第1のエミッタ、及び第1のベースを有する第1の広バンドギャップバイポーラ接合トランジスタ(BJT)と、第1の広バンドギャップBJTのベースに電流を供給するように構成されたソース領域を有する広バンドギャップMOSFETと、第1のコレクターに電気的に接続された第2のコレクター、第1のエミッタに電気的に接続された第2のエミッタ、及び第1のベースに電気的に接続された第2のベースを有する第2の広バンドギャップBJTとを含む高パワー広バンドギャップMOSFETゲートバイポーラ接合トランジスタ(MGT)を提供する。 (もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】エミッタ電子輸送特性やエミッタ注入効率を劣化させることなく、レッジ部を薄層化することが容易で、微細化に適したヘテロ接合バイポーラトランジスタを提供すること。

【解決手段】エミッタ層は、第1の半導体層11と、第2の半導体層12と、第3の半導体層13との積層構造からなり、第3の半導体層13は、第2の半導体層12に対してウェット・エッチングにより選択的に除去でき、第2の半導体層12は、第1の半導体層11に対してウェット・エッチングにより選択的に除去でき、第1の半導体層11と第3の半導体層13のバンドギャップはベース層4のバンドギャップよりも大きく、第2の半導体層12は不純物添加によって縮退しており、第3の半導体層13は不純物添加によって中性領域を形成しているヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波帯域で動作する半導体装置の特性の低下を抑制しつつ、製造コストを低減できる半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置100は、電界効果型トランジスタと、ヘテロ接合バイポーラトランジスタと、ヘテロ接合バイポーラトランジスタのGaAsベース層7を用いて形成されたベースエピ抵抗素子28と、電界効果型トランジスタのInGaAsチャネル層4を用いて形成された配線部26と、配線部26とベースエピ抵抗素子28とを絶縁する高抵抗化領域27と、配線部26の水平方向の周囲を囲う絶縁性の素子分離領域24とを含む。また、ベースエピ抵抗素子28は、半絶縁性GaAs基板1の主面に垂直な方向から見て、配線部26と交差しているベースエピ抵抗素子領域29を有する。

(もっと読む)

静電破壊保護回路

【課題】静電破壊保護回路の大きさを変えることなく、保持電圧を向上させることができ、保持電圧の制御を可能とする静電破壊保護回路を提供する。

【解決手段】ベース領域12の表面に、エミッタ領域6近傍からコレクタ端子側1へベース領域より不純物濃度が高いP型拡散領域20を備える構造とすることで、保持電圧を増加させることができ、P型拡散領域の長さにより保持電圧の値を設定することができる。

(もっと読む)

1 - 20 / 150

[ Back to top ]