Fターム[5F003BB06]の内容

バイポーラトランジスタ (11,930) | ベース (1,440) | ベース抵抗 (264) | グラフトベース (114)

Fターム[5F003BB06]に分類される特許

1 - 20 / 114

半導体装置及びその製造方法

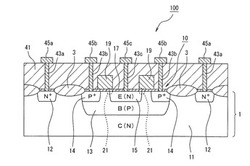

【課題】バーティカル型のバイポーラトランジスタにおいて、エミッタ領域からベース領域にかけて存在する界面準位を安定に低減することを可能とした半導体装置とその製造方法を提供する。

【解決手段】バーティカル型のバイポーラトランジスタ10は、シリコン基板1に形成されたP型のベース領域13と、シリコン基板1に形成されてベース領域13に接するエミッタ領域15と、シリコン基板1の表面であってベース領域13とエミッタ領域15との境界部21上に形成されたシリコン酸化膜17と、シリコン酸化膜17上に形成されたポリシリコンパターン19と、を有する。シリコン酸化膜17とシリコン基板1との界面に塩素が1×1017cm−3以上の濃度で存在する。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタの形成領域において半導体層の下部に絶縁層を有する基板が用いられた半導体装置において、バイポーラトランジスタの電流増幅率を向上させる。

【解決手段】バイポーラトランジスタは、半導体層1cに形成されたコレクタ5、ベース7、エミッタ9、ベース用高濃度オーミック拡散層11及びコレクタ用高濃度オーミック拡散層13、並びに半導体層1c上に形成されたゲート絶縁膜15及びゲート電極17を備えている。ベース7は、絶縁層1bに達する深さで形成され、上方から見てゲート電極17と一部重複して形成され、ゲート電極17下でコレクタ5に隣接して形成されている。ベース7は、ベース7側のゲート電極17の端部からコレクタ5側に向かってP型不純物濃度が低くなる濃度傾斜をもっている。

(もっと読む)

炭化珪素半導体装置

【課題】エミッタ層からコレクタ層を経由してベース層へ移動する電荷の移動を阻止し、エミッタ層からコレクタ層を経由してベース層に注入される電荷を無くすことで、コレクタ層における欠陥の成長を防止することが可能な炭化珪素半導体装置を提供する。

【解決手段】本発明の炭化珪素半導体装置は、炭化珪素半導体基板により構成された炭化珪素半導体装置であり、第1の導電型のコレクタ層102と、コレクタ層の上部に設けられた第2の導電型のベース層104と、ベース層の一部として設けられたベース電極105と、ベース層上に設けられベース電極と離間して設けられたエミッタ層107と、ベース電極からエミッタ層に対して移動する電荷の経路において、コレクタ層内に設けられた、コレクタ層内における電荷の経路を遮断する絶縁体層112とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタポリシリコンに対する良好なコンタクトを得ることができる半導体装置及びその半導体装置の製造方法を提供する。

【解決手段】ラテラル・バイポーラトランジスタを有する半導体装置であって、ラテラル・バイポーラトランジスタは、第1の導電層を構成する基板と、第1の導電層上に配置されたn−hill層312と、n−hill層312を囲む素子分離酸化膜320に開口されたオープン領域と、オープン領域上に形成されるポリシリコン膜910と、ポリシリコン膜910から固相拡散されたエミッタ領域と、素子分離酸化膜320に形成されたダミーゲートポリシリコン706と、を有し、ダミーゲートポリシリコン706によってポリシリコン膜910からの固相拡散されるエミッタ領域の形状が制御される。

(もっと読む)

半導体装置

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタ、コレクタ間の耐圧をより高めることができる半導体装置を提供する。

【解決手段】HCBT100は、第1の導電層を構成する基板1と、n−hill層11と、素子分離酸化膜6とを備え、n−hill層11は第2の導電層と第3の導電層を含み、第3の導電層は第4の導電層を含み、第4の導電層はエミッタ電極31Aと接続し、コレクタ電極31Bをさらに備え、n−hill層11はコレクタ電極31Bと電気的に接続し、少なくとも2つのコレクタ電極31Bを備え、n−hill層11はコレクタ電極31Bと電気的に接続し、少なくとも2つのコレクタ電極31Bは、コレクタ電極31B同士を結ぶ直線と、n−hill層11に備わる少なくとも一つの側面の2つの対向する位置を結ぶ直線とが直交する位置にあることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの動作速度を高速化できるようにした半導体装置の製造方法を提供する。

【解決手段】単結晶Si基板1に設けられたn型のコレクタ層20と、コレクタ層20の表面の周辺部上に設けられたSiO2膜21と、SiO2膜21を覆ってコレクタ層20の表面の中央部に接合するp型のベース層30と、を有し、ベース層30は、コレクタ層20の表面の中央部上に設けられた単結晶SiGe膜31aと、SiO2膜21を覆うように単結晶SiGe膜21上に積層された単結晶Si膜35aとを含む。ベース層30とコレクタ層20との接合領域60がコレクタ層20の表面の中央部に限定されるため、接合面積を小さくすることができ、ベース層とコレクタ層との間の容量CBCを低減することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を増加させることなく、ESD保護素子としてのLDMOSトランジスタのスナップバック電圧をESD被保護素子としてのLDMOSトランジスタのスナップバック電圧より低くし、且つESD保護素子としてのLDMOSトランジスタの熱破壊電流値をスナップバック電圧の改善前より大きくする。

【解決手段】 ESD保護素子としてのLDMOSトランジスタ32は、N型エピタキシャル層3と、N+型埋め込み層2と、N型エピタキシャル層3の表面に形成されたドリフト層11と、エピタキシャル層3の表面に形成されたP型のボディ層10と、Pボディ層10の表面に形成されたN+型ソース層14と、エピタキシャル層3の表面上に形成されたゲート絶縁膜5、6と、ゲート絶縁膜5、6上に形成されたゲート電極8と、を具備し、N+型ソース層14の下方のボディ層10の底部にP型ボディ層窪み部10aが形成されている。

(もっと読む)

バイポーラ半導体素子

【課題】高温や電流密度が高い条件下でも基板へ少数キャリアが到達するのを防いで、順方向電圧の増大を防ぐことができるバイポーラ半導体素子を提供する。

【解決手段】このSiC pinダイオード20では、n型SiC基板21とn型のドリフト層23との間に形成されている厚さを20μmとしたn型のバッファ層22が、p型のアノード層24,25からの正孔のトラップとして働いて、正孔(少数キャリア)がn型SiC基板21へ到達することを防ぐ。これにより、正孔(少数キャリア)がn型SiC基板21へ到達することを防いで、n型SiC基板21から積層欠陥が拡大するのを防いで、順方向電圧の増大を防止できる。

(もっと読む)

半導体装置の製造方法

【課題】本発明の実施形態は、ベース層の幅を狭く形成しエミッタ層の不純物濃度を高くした低雑音特性を有する半導体装置の製造方法を提供することを目的とする。

【解決手段】一実施形態に係る半導体装置の製造方法は、第1導電型の第1半導体層の上に第2導電型の第2半導体層を成長する半導体装置の製造方法であって、前記第1半導体層の表面を常圧よりも低い圧力の還元性雰囲気に曝して熱処理する工程(S02〜S04)と、前記第1半導体層の表面上に、前記第2半導体層を常圧の雰囲気でエピタキシャル成長する工程(S05〜S07)と、を備えたことを特徴とする。

(もっと読む)

バイポーラトランジスタ

【課題】高速動作性・高電流駆動力を有するヘテロ接合バイポーラトランジスタ及びその製造方法を提供する。

【解決手段】バイポーラトランジスタは、コレクタとして機能するSi単結晶層3と、Si単結晶層3の上に形成された単結晶のSi/SiGeC層30a及び多結晶のSi/SiGeC層30bと、エミッタ開口部を有する酸化膜31と、エミッタ電極50と、エミッタ層35とを備えている。単結晶のSi/SiGeC層30aに真性ベース層52が形成され、単結晶のSi/SiGeC層30aの一部と多結晶のSi/SiGeC層30bとCoシリサイド層37bとにより、外部ベース層51が構成されている。エミッタ電極の厚みは、エミッタ電極50に注入されたボロンがエミッタ電極50内を拡散して、エミッタ−ベース接合部まで達しないように設定されている。

(もっと読む)

シリコンゲルマニウムトランジスタの製造方法

【課題】犠牲エミッタ膜を高い選択性で除去することにより特性のバラツキを抑制し、高精度なホトリソグラフィー技術を必要としないシリコンゲルマニウムトランジスタの製造方法を提供する。

【解決手段】SiGe膜6上のシリコン酸化膜8上にN型の犠牲エミッタポリシリコン23を形成し、その周囲にシリコン窒化膜からなるサイドウォール7を形成する。次に、ノンドープのポリシリコン膜24を形成し、サイドウォール7及び犠牲エミッタポリシリコン23をマスクにSiGe膜6にP型不純物をイオン注入して、外部ベース領域を形成する。次に、犠牲エミッタポリシリコン23をエッチングして除去し、その下のシリコン酸化膜8も除去する。その後、犠牲エミッタポリシリコン23等が除去されたエミッタ部分にエミッタポリシリコンを形成する。犠牲エミッタポリシリコン23をエッチングして除去する工程では、エッチャントとしてTMAH水溶液を使用する。

(もっと読む)

半導体装置及びその製造方法

【課題】結晶欠陥による接合リークを防止しながら、バイポーラトランジスタの面積を縮小し、コレクタ容量の低減によってトランジスタ特性を向上できるようにした半導体装置及びその製造方法を提供する。

【解決手段】活性領域1からSTI4上にかけて連続して形成したSiGe膜は、半導体基板3上ではSiGeエピ膜6となり、STI4上ではSiGeポリ膜7となる。半導体基板3とSTI4の境界はSiGe−HBT形成工程以前の洗浄工程によって段差15が生じており、SiGeエピ膜6及び半導体基板3には、上記境界を基点とした結晶欠陥が応力によって発生する可能性がある。この境界に第1のP型不純物層8及び第2のP型不純物層9を設けることで、結晶欠陥をこれらP型不純物層8、9に内包し、接合リークの発生を抑制する。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】薄膜トランジスタ用半導体層の材料として、高い正孔移動度を示すp形半導体多結晶薄膜を、かつ、低い成膜温度でのプラスチック基板上への成膜をも行うことのできるp形半導体多結晶薄膜を、提供する。

【解決手段】ガラスまたはプラスチックまたはステンレス基板のような非結晶質または多結晶基板1上に、該基板の温度を300℃以下とし、成長膜へのガリウム(Ga)、アンチモン(Sb)、及びヒ素(As)原子のそれぞれの供給量JGa,JSb,及びJAsを、JSb<JGa<JAs+JSbを満たすような値として、Ga,Sb,及びAs原子を同時供給して真空蒸着により成膜してなる、Sb組成yが0.5<y<1を満たすp形GaSbyAs1-y多結晶薄膜6を形成する製造方法による。

(もっと読む)

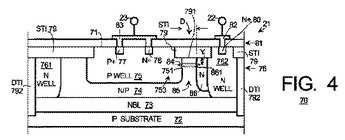

ESD保護デバイスおよび方法

関連するデバイスまたは回路24を保護する静電気放電(ESD)保護クランプ21、21’、70、700は、バイポーラ21、21’、70、700を備える。アバランシェ降伏が、上にある誘電体・半導体界面791から離れ、デバイス70、700のベース領域74、75の部分84,84以内に望ましく起こるように向かうベース75およびコレクタ86領域のドーパントを構成される。例えば、半導体ダイまたはウェハのトランジスタ21、21’、70、700の異なる方位配向のおかげで、ESDトリガ電圧の最大変化(△Vt1)MAXはベース・コレクタ間隔寸法Dの関数である。トリガ電圧一貫性および製造歩留まりが改良される。  (もっと読む)

(もっと読む)

半導体装置、高周波集積回路、高周波無線通信システムおよび半導体装置の製造方法

【課題】SOS基板の異方性を低減して半導体装置のデバイス特性の面内均一性を向上する。

【解決手段】絶縁体基板101の主面上にSi層(またはSi基板)100を有する半導体装置10において、絶縁体基板101はサファイア基板101であり、絶縁体基板101の主面はc面である。サファイア基板101において異方性の少ないc面にSi層100を形成するので、Si層100上に形成された半導体装置10のデバイス特性の面内均一性を向上することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSプロセスへの導入が容易で、エミッタ−ベース間のリーク電流(電界強度)を低減し、ノイズやサージ電圧の影響を受けにくい高性能な半導体装置とその製造方法の提供。

【解決手段】導電膜をマスクとして、2回のイオン注入を行ってエミッタを形成する。第2エミッタ領域111bは、低濃度の不純物イオン注入によって形成し、第1エミッタ領域111aは、高濃度の不純物イオン注入によって形成する。その結果、エミッタの周縁部に低濃度の第2エミッタ領域が形成され、電界が緩和され、リーク電流が低減する。また、導電膜とエミッタ電極116とが接続され、ノイズの影響を受けにくくなる。

(もっと読む)

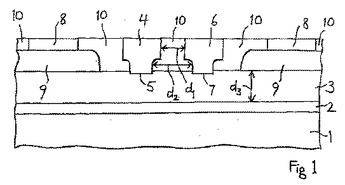

横方向のエミッタおよびコレクタを有するバイポーラトランジスタならびに製造方法

バイポーラトランジスタは、半導体材料からなる基板(1)と、基板内の高移動度層(2)と、高移動度層に隣接したドナー層(3)とを含む。エミッタ端子(4)がドナー層上のエミッタコンタクト(5)を形成し、コレクタ端子(6)がドナー層上のコレクタコンタクト(7)を形成する。ベース端子(8)が高移動度層に導電接続される。当該トランジスタは、GaAsのHEMT技術またはBiFET技術で製造可能である。  (もっと読む)

(もっと読む)

半導体装置

【課題】電力破壊を抑制できる半導体装置を提供すること。

【解決手段】ベース領域12の表面に設定されたベースコンタクト領域14において、ベース電極15がベース領域12に接合されている。ベースコンタクト領域14の境界部の下方には、エミッタ領域13と同じ導電型を有するN型領域21がベースコンタクト領域14を包囲するように形成されている。言い換えれば、ベースコンタクト領域14の境界部の下方において、P型のベース領域12およびN型領域21によりPN型の寄生ダイオードが形成されている。

(もっと読む)

半導体装置の製造方法及び半導体集積回路装置

【課題】本発明は、簡素な工程で、デバイスの特性を均一化することができる半導体装置の製造方法及び半導体集積回路装置を提供することを目的とする。

【解決手段】半導体基板40の表面の所定領域41に、LOCOS酸化膜70を形成するLOCOS酸化膜形成工程と、

該LOCOS酸化膜70と前記半導体基板40の表面の境界を覆うように、ポリシリコン膜90を形成するポリシリコン形成工程と、

該ポリシリコン膜90をマスクとして、前記半導体基板40の表面にイオンの打ち込みを行い、前記半導体基板40の表面に、不純物領域60を形成するイオン打ち込み工程と、を含むことを特徴とする。

(もっと読む)

ESD保護素子

【課題】ESD耐量及びノイズ耐性を向上させたESD保護素子を提供する。

【解決手段】本発明によるESD保護素子は、NPNバイポーラトランジスタTr1と、一端がパッド10に接続されたトリガ素子20とを具備する。NPNバイポーラトランジスタTr1は、第1ベース拡散層204と、パッド10に接続されたコレクタ拡散層4と、第1ベース拡散層204上に形成され、第1配線L1を介してトリガ素子20の他端に接続されたトリガタップ1と、第1ベース拡散層204上に形成され、第1配線L1と異なる第2配線L2を介してGNDに共通接続されたエミッタ拡散層2及び第2ベース拡散層3とを備える。

(もっと読む)

1 - 20 / 114

[ Back to top ]