Fターム[5F004EA06]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | マスク構成 (1,627) | レジスト以外のエッチングマスク (1,380) | SiO2膜 (416)

Fターム[5F004EA06]に分類される特許

401 - 416 / 416

膜スタックをエッチングするための方法およびシステム

膜スタックを設け、複数のドライ・エッチング・プロセスを用いてこの膜スタック中にフィーチャを形成するための方法およびシステムが記載される。膜スタック中に形成されたフィーチャは、約25nm以下の限界寸法を有するゲート構造を含み得る。この限界寸法は、4つのマスク層を用いてポリシリコン層中に形成できる。  (もっと読む)

(もっと読む)

エッチング方法、微細構造体の製造方法、導電線の形成方法、薄膜トランジスタの製造方法及び電子機器の製造方法

【課題】本発明は、微細なパターンを単純な工程で形成し得るエッチング方法を提供することを目的としている。

【解決手段】 本発明は、基板上に膜形成材料を含む液滴を配置する第1工程と、前記液滴を乾燥し、前記配置時の液滴の径よりも狭い幅の乾燥膜を形成する第2工程と、前記乾燥膜をエッチング保護膜としてエッチングする第3工程と、を含むエッチング方法により、上記課題を解決する。前記第2工程の後に、前記乾燥膜の一部を除去することにより前記乾燥膜をパターニングする第4工程を含んでもよい。

(もっと読む)

FeRAM用途のためのPt/PGOエッチングプロセス

【課題】強誘電体層のエッチングによる損傷を最小限にするエッチング方法を提供する。

【解決手段】強誘電体層の強誘電特性を保ち、エッチング残留物を除去しながら、強誘電体層の上の貴金属上部電極をエッチングする方法は、用意された基板上にバリア層を堆積することと(14)、バリア層上に堆積された下部電極層の上に強誘電体層を堆積することと(18)、強誘電体層上に堆積された上部電極層の上に接着層を堆積すること(22)、接着層上に堆積されたハードマスクをパターニングすることと(28)、最初のエッチング工程において、エッチング残留物を生成する所定の基板RFバイアス電力で貴金属上部電極層をエッチングすること(30)、および所定のRFバイアス電力よりも低いRFバイアス電力で貴金属上部電極層と強誘電体層とをオーバーエッチングすることによって、最初のエッチング工程のエッチング残留物を除去することと(32)を含む。

(もっと読む)

電子デバイス及び微細幅パターンの形成方法

【課題】 電子デバイス及び微細幅パターンの形成方法に関し、抜きパターンや残しパターンのいずれの場合もパターン分布の粗密に依存せずに所望の微細幅パターンを精度良く形成する。

【解決手段】 同じ線幅の孤立パターンの第1の凹部3と密パターンのn個の第2の凹部4とを設けた絶縁層2と、絶縁層2上に第1の凹部3及び第2の凹部4に対応する同じ線幅の第1の開口部6及び第2の開口部を有する第1の薄膜5と、第1の薄膜5上に、孤立パターンの第1の凹部3に対応する領域においては、第1の凹部3より広く且つ第2の凹部4のピッチの2倍と凹部の幅との差より狭い線幅の第3の開口部9を有するとともに、密パターンの第2の凹部4に対応する領域においては、第2の凹部4のピッチのn−1倍と凹部の幅との和より広く且つ第2の凹部4のピッチのn+1倍と凹部の幅との差より狭い線幅の第4の開口部10を有する第2の薄膜8とを備える。

(もっと読む)

半導体素子の作製方法及び半導体素子

【課題】 マスクを用いたエッチング加工を改良した半導体素子の作製方法及び半導体素子を提供すること。

【解決手段】 SiO2膜63上にレジストを塗布した後に回折格子作製マスク用のレジストパターン64を作製する(c)。レジストパターンをマスクとしてSiO2膜を加工することにより、レジストパターンをSiO2膜63に転写する(d)。レジストパターン64を除去することにより、InP上に傾斜面aを有する導波層構造を作製するためのSiO2マスクが形成される(e)。マスクから半導体表面への塩素プラズマの拡散によりマスク端から離れるにつれてエッチング深さが浅くなり、傾斜面aを有する形状が形成される(f)。最後にSiO2膜63を、炭化フッ素系ガスを用いたRIEにより除去する(g)。

(もっと読む)

シリコン含有誘電物質をエッチングする方法

本明細書にはシリコン含有誘電物質の層をパターンエッチングする方法が開示される。該方法は、約2:3〜約3:1、更に典型的には約1:1〜約2:1の範囲にあるCF4とCHF3を含むプラズマ供給源ガスを用いる。エッチングは、約4mTorr〜約6mTorrの範囲にあるプロセスチャンバ圧で行われる。該方法は、1.5:1以上のフォトレジストに相対してシリコン含有誘電体層をエッチングする選択性を与える。該方法は、また、半導体構造において前記エッチングされたシリコン含有誘電体層と下にある水平層間に88°〜92°の範囲にあるエッチングプロファイル側壁角を与える。該方法は、193nm放射光に敏感であるある種のフォトレジストと組合わせて用いた場合に平滑な側壁を与える。  (もっと読む)

(もっと読む)

有機材料層のパターニング方法およびこれを用いた電子デバイス

【課題】 有機材料層のパターン精度の向上をはかるとともに、有機材料層の劣化を防止し、信頼性の高い有機材料層のパターンを提供する。また、有機材料層のパターン精度の向上をはかり、小型でかつ高感度の電子デバイスを提供する。

【解決手段】 本発明の有機材料層のパターニング方法は、前記有機材料層上に少なくとも2層の異なる無機材料層を形成する工程と、前記無機材料層の上層にレジストパターンを形成する工程と、前記レジストパターンをマスクとしてエッチングを行い前記無機材料層のパターンを形成する工程と、前記レジストパターンを除去する工程と、前記無機材料層のパターンをマスクとしてエッチングを行い前記有機材料層のパターンを形成する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】上層配線に被覆されない接続孔を選択的に縮小させることにより、隣接する異電位配線とのショート不良を防止することを可能とする。

【解決手段】基板上に第1、第2絶縁膜18、19を形成する工程と、その上に有機犠牲層30と第1、第2マスク層31、32を順に形成する工程と、第2マスク層32に配線溝パターン33を形成する工程と、第2、第1マスク層32、31および有機犠牲層30に接続孔を形成するための接続孔パターン34を形成する工程と、第2、第1マスク層31、32をエッチングマスクに用いたエッチングにより第1マスク層31、有機犠牲層30に配線溝パターン33を形成し、第2絶縁膜19に接続孔35を形成する工程と、第1マスク層31、有機犠牲層30をマスクに用いて、第2絶縁膜19に配線溝36を形成し、第2、第1絶縁膜19、18に接続孔35を形成する工程とを備えている。

(もっと読む)

近接場露光によるレジストパターンの形成方法、及び該レジストパターンの形成方法を用いた基板の加工方法、デバイスの作製方法

【課題】高アスペクトなパターンの形成が可能となる近接場露光によるレジストパターンの形成方法、及び該レジストパターンの形成方法を用いた基板の加工方法、デバイスの作製方法を提供する。

【解決手段】近接場露光用マスクを基板上に形成したレジスト層に近接させ、該マスクの面側に光を照射した際に該マスクの微小開口から滲み出る近接場光を用いて露光し、前記レジスト層にマスクパターンを転写する近接場露光によるレジストパターンの形成方法において、前記基板上に、近接場光のしみ出し深さ以上の厚さのネガ型レジスト層を形成する工程と、前記ネガ型レジスト層を、前記近接場光を用いて露光する露光工程と、前記露光されたネガ型レジスト層を現像液で現像し、該ネガ型レジスト層の厚さよりも浅い領域にパターンを形成する現像工程と、を少なくとも有する構成とする。

(もっと読む)

偏向器、偏向器アレイ、偏向器の作製方法、荷電粒子線露光装置およびデバイス製造方法

【課題】 所望の偏向感度が得られ、高周波駆動に対応した偏向器及びその作製方法を提供する。

【解決手段】 基板501上に、貫通口と、この貫通口の側壁に配置された互いに対向する少なくとも一対の電極503a,503bと、を有する偏向器であって、前記基板の上面、前記基板の下面および前記電極と前記基板の間のうち少なくとも1か所に、複数の絶縁層504a, 504bが積層されており、前記複数の絶縁層の少なくとも1つが、二酸化シリコンからなる。

(もっと読む)

二層レジストプラズマエッチングの方法

【課題】

【解決手段】プラズマエッチング室内において、基板の上に形成された二層レジストをエッチングするための方法が提供される。該方法は、二層レジストの第1の層の上にパターンを形成された基板をエッチング室に導入する工程から開始される。次いで、SiCl4ガスがエッチング室に流し込まれる。次に、SiCl4ガスを流し入れつつエッチング室内においてプラズマを発生させる。次いで、二層レジストがエッチングされる。

(もっと読む)

半導体集積回路装置の製造方法

規格外れの不良ウェハをリアルタイムに検出することができる半導体集積回路装置の製造方法を提供することにある。

異常検知サーバ5は半導体ウェハを処理する半導体製造装置から出力された装置ログデータを装置ログデータ記憶部10に記憶する。その後、ロットエンド信号受信部12において、半導体製造装置から出力されるロットエンド信号を受信すると、異常データ検知部15は、第1検知条件記憶部13に記憶されている異常検知条件設定ファイル13aを参照した後、参照した内容に基づいて装置ログデータ記憶部10に記憶されている装置ログデータの中に異常データがあるか否かを判定する。そして、異常を検知するとエンジニアPCや作業者端末装置に検知結果を出力する。

(もっと読む)

溝配線を有する半導体装置および半導体装置の製造方法

【課題】 多層配線において、ショートやビア抵抗増加のような目合わせずれによる問題を回避し、信頼性の高い多層配線を得る。

【解決手段】 半導体装置は、第1配線層(201)と、層間絶縁層(202〜208)とを具備する。第1配線層(201)は、基板の上面側に設けられ、第1配線を含む。層間絶縁層(202〜208)は、前記第1配線層(201)上に設けられ、一方の端を前記第1配線に接続されたビアと、前記ビアの他方の端に接続された第2配線とを含む。前記層間絶縁層(202〜208)はシリコン酸化膜より低い比誘電率を有する。前記層間絶縁層(202〜208)の上部は、下側から順に、シリコン酸化膜(206)、シリコン窒化膜(207)、シリコン酸化膜(208)を備える。

(もっと読む)

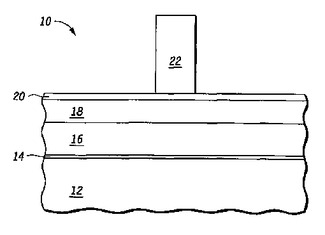

有機反射防止膜(ARC)を有する半導体装置及びその方法

半導体装置(10)の製造において、エッチングされる導電性材料(16)上のパターニング積層部は、下層にあるオルトケイ酸テトラエチル(TEOS)層(20)のパターニングに用いられるパターニングフォトレジスト層(22)を有している。TEOS層(20)は、従来より低い温度で成膜される。低温TEOS層(20)は、有機反射防止膜(ARC)(18)上に設けられ、有機反射防止膜は、導電層(16)上に設けられる。低温TEOS層(20)は、有機ARC(18)とフォトレジスト(22)との間の接着を提供し、低い欠陥性を有し、ハードマスクとして機能し、有機ARC(18)と共に望ましくない反射を低減させる位相シフト層として機能する。  (もっと読む)

(もっと読む)

シリコン基板に凹部を異方性エッチングにより形成する方法およびプラズマエッチングシステムの使用方法

【課題】シリコン基板に異方性エッチングにより深さが大きい凹部を形成するための、簡便な方法およびプラズマエッチングシステムの使用方法を提供する。

【解決手段】反応性エッチングガスをエネルギー励起するためにプラズマを用いる。反応性エッチングガスは、連続的に流れるガスフローの成分である。凹部は、エッチング時に、上記ガスフローを中断することなく少なくとも50マイクロメートルの深さに形成される。その結果、深さの大きい凹部を製造するための簡便な方法が提供される。

(もっと読む)

デュアルダマシンによる半導体装置の製造方法

【課題】 放熱性が良好で、製造コストが低く、微細加工に好適なデュアルダマシンによる半導体装置の製造方法を提供する。

【解決手段】 基板1上に無機層間膜5、有機層間膜6、シリコン酸化膜からなる下部マスク7、シリコン窒化膜からなる上部マスク8を形成し、上部マスク8上にシリコン酸化窒化膜からなり膜厚が20乃至100nmであるカバーマスク10を形成する。そして、反射防止膜11及びレジスト膜12を形成する。次に、レジスト膜12をマスクとして、反射防止膜11、カバーマスク10、下部マスク7をエッチングする。そして、カバーマスク10をマスクとして、有機層間膜6及び無機層間膜5をエッチングしてビアホールを形成する。次に、上部マスク8をマスクとして有機層間膜6をエッチングして配線溝を形成する。

(もっと読む)

401 - 416 / 416

[ Back to top ]