Fターム[5F004EA31]の内容

半導体のドライエッチング (64,834) | パターン形成手法 (4,711) | バイアススパッタ (15)

Fターム[5F004EA31]に分類される特許

1 - 15 / 15

プラズマエッチング方法

【課題】 テーパー角度を90度未満とするプラズマエッチング方法を提供する。

【解決手段】 反応性エッチングガスとしてフッ素と酸素とを真空容器1内に導入し、コイル6に高周波電力を供給して誘導結合型プラズマ7を発生し、このプラズマによって基板電極8上にエッチング部材10として配置されたシリコンをエッチングし、基板電極8に基板電極用交流電源11から供給する交流電力の周波数によってシリコンにエッチングされる形状を制御する。

(もっと読む)

半導体のためのエッチングプロセス

II〜VI型又はIII〜V型半導体のような半導体をエッチングするためのプロセスが提供される。この方法は、エッチングマスクを介して非反応性ガスで半導体をスパッタエッチングする工程と、半導体を取り出す工程と、反応性ガスでチャンバーを洗浄する工程と、を含む。エッチングマスクはフォトレジストを含む。この方法を使用し、半導体材料にエッチングされた光抽出素子又はナノ/微小構造物を有する発光ダイオードを製作することができる。 (もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法、および溝の形成方法

【課題】低いオン抵抗と高い耐圧性とを有する電界効果トランジスタ、電界効果トランジスタの製造方法、および溝の形成方法を提供する。

【解決手段】窒化物系化合物半導体からなる電界効果トランジスタであって、基板101と、前記基板上に形成された高抵抗層103と、前記高抵抗層上に形成された、炭素濃度が1×1018cm−3以下であり層厚が10nmより厚く、100nm以下であるチャネル層104を含む半導体動作層106と、前記半導体動作層に前記チャネル層の内部に到る深さまで形成されたリセス部107と、前記半導体動作層上に前記リセス部を挟んで形成されたソース電極108およびドレイン電極109と、前記半導体動作層上にわたって前記リセス部内を覆うように形成されたゲート絶縁膜110と、前記リセス部において前記ゲート絶縁膜上に形成されたゲート電極111と、を備える。

(もっと読む)

圧電素子及びその製造方法並びにインクジェットヘッド

【課題】電極間のリーク電流の発生及び応力集中が効果的に抑制されるとともに、高密度化が可能であり、さらに、圧電体層のプラズマダメージが抑制された圧電素子を提供する。

【解決手段】圧電素子10は、支持体12と、支持体12上に形成されている下部電極16と、下部電極16上に形成されている圧電体層20と、圧電体層20上に下部電極16と対向するように形成されている上部電極24と、を有し、圧電体層20の下部電極16側の面が上部電極24側の面よりも大きくなるように圧電体層20の下部電極16側の周囲に段差部20Aが形成されている。

(もっと読む)

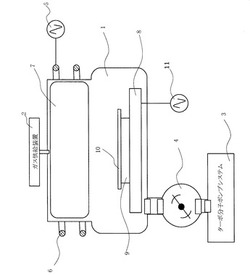

プラズマ処理方法及びプラズマ処理装置

【課題】成膜レートを安定に維持することができるプラズマ処理方法及びプラズマ処理装置を提供する。

【解決手段】本発明の一形態に係るプラズマ処理方法は、エッチング工程と保護膜形成工程とを交互に繰り返し実施することでシリコン基板に高アスペクト比のビアを形成する。そして、保護膜の形成工程にはスパッタ法が適用される。スパッタ工程では、アンテナコイル23に高周波電力(RF1)を供給して、真空槽21内にスパッタ用ガスのプラズマを形成する。このとき、アンテナコイル23に供給する高周波電力を2kW以上とする。アンテナコイル23に供給する高周波電力が2kW以上の場合、当該高周波電力が2kW未満である場合と比較して、ターゲット30の使用時間に依存しない安定した成膜レートを得ることが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】Cuを主体とする配線について、配線抵抗を低く維持するとともに、ストレスマイグレーション耐性及びエレクトロマイグレーション耐性を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の上方に形成された層間絶縁膜28、30と、層間絶縁膜28、30に形成されたビアホール34及び配線溝36内に形成され、Ta膜より成るバリアメタル膜38と、バリアメタル膜38上に形成されたTi膜40と、バリアメタル膜38及びTi膜40が形成されたビアホール34及び配線溝36内にそれぞれ埋め込まれ、Cuより成る導体プラグ44及び配線46とを有し、Ti膜40の膜厚が、配線溝36の底部において4nm以下になっている。

(もっと読む)

半導体装置の製造方法

【課題】層間絶縁層の剥離を抑制し、製品の歩留まりが向上するとともに製品信頼性が向上した半導体装置を得ることができる製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板上に形成された第1配線膜15と、反射防止膜17および第1レジスト膜18からなる積層体から、第1レジスト膜18を除去する工程と、前記工程において反射防止膜17表層に形成された変質膜22を除去する工程と、前記工程後に第1配線膜15に電気的に接続するビアプラグと、前記ビアプラグに電気的に接続する第2配線膜とを形成する工程とを含む。

(もっと読む)

プラズマ処理装置及びプラズマ処理方法

【課題】大幅な装置構成の変更や、処理条件の変更を要することなく、処理レート分布を制御可能なプラズマ処理装置及びプラズマ処理方法を提供する。

【解決手段】電源と、放電空間に臨んで設けられ、電源から電力が印加されるカソード体と、互いに絶縁分離されて放電空間に臨んで設けられた複数のアノード体と、を備え、各々のアノード体を介して放電空間の外部に流れる電流の経路のうち少なくとも2つの経路間でコンダクタンスを異ならせた。

(もっと読む)

パターニング方法

【課題】フレキシブル基板上に室温成膜した比較的厚いITO薄膜をエッチングにより残渣やサイドエッチなくパターニングすること。

【解決手段】不純物ドープ酸化インジウム薄膜のパターニング方法において、ドライエッチング法により該不純物ドープ酸化インジウム薄膜のエッチングを行う工程と、

ウェットエッチング法により前記ドライエッチング法を行った不純物ドープ酸化インジウム薄膜のエッチングを行う工程とを行うパターニング方法を用いる。具体的には、ITO薄膜を約50nm残すように上部をドライエッチングによりエッチングによりエッチングし、連続してウェットエッチングによりエッチングしてパターニングを行うパターニングを方法。

(もっと読む)

上部電極/強誘電体積層膜のエッチング方法

【課題】 上部電極/強誘電体積層膜のエッチング方法を提供する。

【解決手段】 上部電極/強誘電体積層膜のエッチング方法は、基板上に第1誘電体材料の第1層を形成する工程と、前記第1誘電体材料の第1層に下部電極を形成する工程と、前記第1誘電体材料の第1層と前記下部電極上にエッチストップ層を堆積させ、そこに開口部を形成する工程と、強誘電体材料層を堆積させる工程と、前記強誘電体材料層上に上部電極材料を堆積させ、前記上部電極/強誘電体材料積層膜を形成し、前記上部電極及び前記強誘電体材料層をスタックエッチングする工程と、前記第2誘電体材料の第2層を堆積させ、前記上部電極及び前記強誘電体材料を封止する工程と、前記第2誘電体材料の第2層をエッチングし、前記上部電極及び前記強誘電体材料の周囲にサイドウォールを形成する工程と、前記第1誘電体材料の第2層を堆積させる工程と、前記第1誘電体材料の第2、第3層を堆積させる工程とを有する。

(もっと読む)

トレンチの形成方法、充填材のパターンの形成方法、充填材のパターン及びデバイス

【課題】 被エッチング膜に対して、左右の側壁の傾斜角が互いに異なるトレンチを形成することができるトレンチ形成方法、2つの側壁の傾斜角が互いに異なる充填材のパターンの形成方法、これを用いた充填材のパターン及びデバイスを提供することを目的とする。

【解決手段】 基板1上に形成された被エッチング膜10の一部をエッチングしてトレンチを形成するトレンチ形成方法であって、被エッチング膜10上にトレンチに対応する開口35を有するドライエッチングマスク30を形成する工程と、ドライエッチングマスク30をマスクとして被エッチング膜10をエッチングしてトレンチを形成する工程と、を備え、ドライエッチングマスク30において開口35を挟んで対向する2つの側壁35L,35Rの傾斜角θDL,θDRが互いに異なる。

(もっと読む)

High−k層内に形態を形成する方法及びシステム

【課題】High−k層内に形態を形成する方法及びシステムを提供することである。

【解決手段】high−k層をプラズマ処理する方法は、high−k層が上に形成されている基板を、処理チャンバ内の基板ホルダ上に提供することと、この処理チャンバ内にプラズマを生成し、それによって、このhigh−k層をこのプラズマにさらすこととを含む。高周波電力がこの基板ホルダに印加され、この高周波電力は、この基板とこのhigh−k層との間に配設されている酸化物界面層の形成の割合を低減する特性を有する。デバイスは、high−k層内でエッチングされた形態を含む。このデバイスのエッチングプロファイルは、低減されたバーズビークを含むことができ、また、エッチングされた領域内におけるこの基板の表面は、エッチングされていない領域の下の基板と実質的に同一平面にすることができる。

(もっと読む)

高周波電力用分岐スイッチ及びエッチング装置

【課題】 プラズマ中の電流、電圧の変化に弱いデバイスの加工が可能な、プラズマ発生装置のための高周波電力用分岐スイッチ及びこの分岐スイッチを備えたエッチング装置の提供。

【解決手段】 主放電発生電力回路により高周波電力を分岐して副電極等に主放電電力の一部を導入する構造を持つプラズマ発生装置であって、分岐デバイスとして可変コンデンサーを用いると共に、この可変コンデンサーの容量に関して、パルスモータ又はサーボモータにより、最小容量値と設定容量値とを、又は低い設定容量値と高い設定容量値とを可及的に短時間で切り替える機構として容量値制御装置を設ける。

(もっと読む)

被エッチング層のエッチング方法、半導体装置の製造方法、及び、半導体装置

【課題】被エッチング層の所望の領域の表面を平坦化し得るエッチング方法を提供する。

【解決手段】対となった電界形成用電極13A,13B、及び、対となった電界形成用電極13A,13B間に被エッチング層20が形成され、且つ、エッチングすべき部分に開口部22が設けられたレジスト層21が該被エッチング層20の表面に形成された基体10における被エッチング層20のエッチング方法であって、対となった電界形成用電極13A,13Bへの異なる電圧の印加によって被エッチング層20の表面近傍に基体10の表面と略平行な電界(E)を生成させることで、エッチング種に基体10の表面と平行な速度成分を付与した状態で、該エッチング種によって被エッチング層20をエッチングする。

(もっと読む)

炭化珪素単結晶及びそのエッチング方法

【課題】半導体分野等を含め非常に応用の広い炭化珪素単結晶を得ること、及び、炭化珪素単結晶に三フッ化窒素プラズマを用いて平滑にできる炭化珪素単結晶のエッチング方法を提供する。

【解決手段】平滑性(表面粗さ)が±150nm以内である炭化珪素単結晶及び当該材料を得るために、三フッ化窒素を含有するガスをプラズマ励起し炭化珪素単結晶の表面を平滑化する。なお、三フッ化窒素ガスの圧力が0.5〜10Paであることが好ましい。

(もっと読む)

1 - 15 / 15

[ Back to top ]