Fターム[5F004FA06]の内容

半導体のドライエッチング (64,834) | エッチング工程前後の処理 (659) | 機械的ダメージ (16)

Fターム[5F004FA06]に分類される特許

1 - 16 / 16

GaN系半導体基板の製造方法

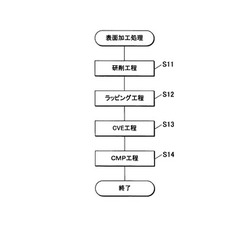

【課題】表面加工処理の所要時間を大幅に短縮化して生産性を向上できるGaN系半導体基板の製造方法を提供する。

【解決手段】GaN系半導体基板の表面加工処理において、GaN系半導体基板の表面に対して機械的研磨を行い(研削工程、ラッピング工程)、その後、GaN系半導体基板表面に対して化学的気相エッチングを行う(CVE工程)。

ラッピング工程後にGaN系半導体基板表面に残存する加工変質層が、CVE工程により効率的に除去されるので、GaN系半導体基板の表面加工処理の所要時間を大幅に短縮化できる。

(もっと読む)

基板表面に円錐形のナノ構造を製造する方法

本発明は、基板表面、特に光学素子上の円錐形のナノ構造、その製造方法、および、特に光学装置、太陽電池およびセンサにおけるその使用に関する。本発明に係る円錐形のナノ構造は、特に、非常に低い光反射性を有する基板表面を準備するために好適である。基板表面上に円錐形のナノ構造を作る本発明に係る方法は、少なくとも以下の工程を有する:a)ナノ粒子で被覆された基板表面を準備し、b)ナノ粒子で被覆された前記基板表面を少なくとも100nmの深さまでエッチングし、ここで前記ナノ粒子はエッチングマスクとして作用し、前記ナノ粒子の下方に双曲面構造が生じるようにエッチングパラメータを設定し、c)機械的な力を加えることによって前記双曲面構造を最小の直径の領域において破壊し、ここで前記基板表面に残る構造が一層の双曲面の実質的に半分に対応する円錐形の形状を有する。 (もっと読む)

半導体装置の製造方法

【課題】 下面を研削または研磨されたシリコン基板の抗折強度を高くする。

【解決手段】 半導体ウエハ21の下面側を適宜に研削または研磨する。この状態では、半導体ウエハ21の下面には研削または研磨によるダメージ層が形成されている。次に、ドライエッチングにより、半導体ウエハ21の下面に形成されたダメージ層を除去する。これにより、半導体ウエハ21をダイシングして得られた半導体装置のシリコン基板の抗折強度を高くすることができる。

(もっと読む)

SiC基板

【課題】 実用的な条件によって加工変質層を除去するSiC基板の製造方法を提供する。

【解決手段】 本発明のSiC基板11は、実質的に平行な第1および第2の主面11a、11bを有し、第2の主面11bのみが鏡面仕上げされており、反りが±50μm以下であるSiC基板であって、第2の主面11bの表面粗度Raは1nm以下であり、第1の主面11aの加工変質層が除去されている。

(もっと読む)

III−V族化合物半導体基板の製造方法

【課題】III−V族化合物半導体基板のPL強度を向上できるIII−V族化合物半導体基板の製造方法を提供する。

【解決手段】このIII−V族化合物半導体基板の製造方法では、まず、ウェハ3の表面3aを研磨する(研磨工程)。次に、ウェハ3の表面3aを洗浄する(第1の洗浄工程S7)。次に、ハロゲンを含むガスを用いて、ウェハ3を載置するためのチャック24に第1のバイアス電力を印加しながら、ウェハ3の表面3aに第1のドライエッチングを施す(第1のドライエッチング工程S9)。次に、ハロゲンを含むガスを用いて、チャック24に第1のバイアス電力よりも電力値が小さい第2のバイアス電力を印加しながら、ウェハ3の表面3aに第2のドライエッチングを施す(第2のドライエッチング工程S11)。

(もっと読む)

RFパウダーの製造方法

【課題】大量の粒子から成りかつ集合的形態をとるRFパウダー(粉状体)として使用される特性を有し、1枚のウェハから多数のRFパウダー粒子を高い収率で確実に分離して取り出すことができるRFパウダーの製造方法を提供する。

【解決手段】RFパウダーの製造方法は、1つの粒子11aが、基板12、磁界結合回路素子15を含み、大量の上記粒子から成るRFパウダーを製造する方法である。この方法は、ウェハ40上にアンテナ回路素子39を大量に作製する工程S11、ウェハで磁界結合回路素子を分離するための位置に切溝を形成するガスダイシング工程S13、磁界結合回路素子の周囲を保護膜で覆う保護膜形成工程S14、粘着シートにより強化プレートを貼り付ける強化工程S15、ウェハの裏面を切溝まで研削する研削工程S16、強化プレートを取り除いて回路素子を分離する分離工程S17を有する。

(もっと読む)

半導体チップの製造方法

【課題】プラズマダイシングとダイアタッチフィルムによるボンディングを両立させることができ、併せてプラズマ処理用の真空チャンバ内の汚損も抑えることができる半導体チップの製造方法を提供する。

【解決手段】半導体ウエハ1にダイアタッチフィルム4及びUVテープ5から成るフィルム層6をマスクとして設けた後、そのフィルム層6に、回路パターン形成面1aに形成された半導体素子2同士を区分する境界溝7を形成して半導体ウエハ1の表面を露出させる。そして、境界溝7に露出した半導体ウエハ1の表面をフッ素系ガスのプラズマによりエッチングし、半導体ウエハ1を境界溝7に沿って個々の半導体チップ1′に切り分ける。

(もっと読む)

半導体素子の製造方法

【課題】ゲートハードマスクの損失を最小化し、かつ、コンタクトホールのオープン不良現象の改善に適した半導体素子の製造方法を提供すること。

【解決手段】本発明の半導体素子の製造方法は、基板21上に第1パターンG’を形成するステップと、該第1パターン上に酸化膜を形成するステップと、該酸化膜上にハードマスク層を形成するステップと、該ハードマスク層を第1基板温度でエッチングするステップと、前記酸化膜をエッチングして第2パターンを形成するステップとを含み、前記酸化膜のエッチングの際、第1基板温度より更に高い第2基板温度でフッ素(F)及び炭素(C)を含有しているガスをメインエッチングガスとして用いる。

(もっと読む)

半導体基板の表面処理方法

【課題】半導体基板の裏面を研削した場合でも、チッピングや割れを防止できる半導体基板の表面処理方法を提供する。

【解決手段】大気圧プラズマ処理装置10で発生させたプラズマが半導体基板52の面取りされたエッジ部分54に衝突すると、エッジ部分54のひずみが除去され、同時にエッジ部分54の角が丸くなりエッジ部分54が断面R状に形成される。これにより、後工程において半導体基板52の裏面Bを研削する場合でも、エッジ部分54のひずみが除去されかつエッジ部分54が断面R状に形成されているので、エッジ部分54にチッピングや割れが発生することを防止できる。

(もっと読む)

ゲッタリング層形成装置

【課題】研磨された半導体ウェーハの裏面に多結晶シリコン層やシリコン窒化層からなるゲッタリング層を形成する場合において、ゲッタリング層に十分なゲッタリング効果を生じさせる。

【解決手段】半導体ウェーハを保持する保持面180を有するチャックテーブル18と、保持面180に表面側が保持された半導体ウェーハWの裏面W2を研磨する研磨手段20、21と、裏面W2が研磨された半導体ウェーハWを洗浄する洗浄手段15と、洗浄済みの半導体ウェーハWを収容して半導体ウェーハWの裏面W2にシリコン窒化層または多結晶シリコン層のいずれかをゲッタリング層として形成するゲッタリング層形成手段47とから少なくとも構成されるゲッタリング層形成装置1を提供する。

(もっと読む)

シリコン基板のストレスリリーフ方法

【課題】シリコン基板を対象としたストレスリリーフにおいて、低コストのプロセスで熱ダメージがなく、且つ環境負荷を低減することが可能なシリコン基板のストレスリリーフ方法を提供することを目的とする。

【解決手段】シリコン基板を機械研削した後の加工済み基板4を対象として、機械研削後の裏面1bに生成したストレス層を除去するために行われるストレスリリーフにおいて、加工済み基板4を原子状水素処理装置5の減圧された処理室7内に収容し、原子状水素発生装置20によって水素ガスから発生された原子状水素を処理対象面である裏面1bに接触させ、この処理対象面の表面層を原子状水素の作用によってガス化して除去する。これにより、低コストのプロセスで熱ダメージがなく且つ環境負荷を低減することが可能なストレスリリーフ処理が実現される。

(もっと読む)

カラーフィルタの形成方法およびこれを用いた固体撮像素子の製造方法

【課題】高精度のパターン形成を可能にし、混色を防ぐとともに薄型化を実現することのできるカラーフィルタの形成方法を提供する。また、薄型化をはかり、高度の微細化に際しても高感度で信頼性の高い固体撮像素子を提供する。

【解決手段】フィルタ材料を塗布する工程と、レジストパターンをマスクとして前記フィルタ材料をエッチングする工程とを含み、前記フィルタ材料をパターニングするカラーフィルタの形成方法であって、エッチングする工程は、エッチングガスとして、カーボン(C)化合物を含む酸素(O2)を主成分とする反応性ガスを用いてエッチングする工程を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 深さの異なるコンタクトホールを同時に形成する場合にも、高抵抗化や接続不良等を無い高品質なコンタクトホールを形成する。

【解決手段】 半導体基板10の表面側に、有機系の絶縁材料からなる第1層膜18、無機系の絶縁材料からなる第2層膜19の2層構造を有する層間絶縁膜17が形成される。ソース・ドレイン拡散領域11及びゲート電極14に達するコンタクトを形成するため、この層間絶縁膜17にコンタクトホールが形成される。第2層膜19のエッチングは、C4H8系のガスで行うと、エッチングは第1層膜18と第2層膜19の界面で止まる。次にエッチングガスをNH3系のガスに切り替えて、第1層膜18のエッチングを行う。

(もっと読む)

半導体装置及びその製造方法

【課題】デュアルダマシン法により配線層を形成するに際し、微細なビアホール及び配線トレンチへの配線材の埋め込みを容易にしうる半導体装置及びその製造方法を提供する。

【解決手段】 ビアホール形成領域以外の領域を覆うマスク20と、配線トレンチ形成領域以外の領域を覆うマスク22とをマスクとして絶縁膜16,18にビアホール26及び配線トレンチ32を形成するに際し、ビアホール形成領域の周辺部に絶縁膜18の上面が露出し周辺部を除く配線トレンチ形成領域内のマスク20が残存するようにマスク20を等方性エッチングした後、マスク20及び絶縁膜18,16を異方性エッチングすることにより、上部に幅広部34を有するビアホール26と、ビアホール26の幅広部26に接続された配線トレンチ32とを形成する。

(もっと読む)

半導体装置製造方法

【課題】密着性、電気抵抗特性および抗折強度特性のいずれをも満足させて、半導体基板に裏面電極となる金属膜を形成することができる半導体装置製造方法を提供することを目的とする。

【解決手段】半導体基板の一方の表面にデバイス層を形成し裏面に裏面電極を形成して成る半導体装置を製造する半導体装置製造方法において、裏面電極となるメタライズ層5の形成する成膜工程に先立って、裏面1bを機械研削して表面を谷部a、山部bを有する凹凸面に粗化し、次いで粗化された表面をアルゴンガスを主体とするプラズマ発生用ガスを用いた第1のプラズマエッチング処理により、機械研削に伴って生成した加工変質層1cを除去するとともに、谷部a、山部bを拡大して表面粗さを増大させる。

(もっと読む)

コヒーレントな波形ナノ構造の形成方法(変形体)

波形ナノ構造を形成する本発明の方法は、周期的な波形ナノ構造が材料表面に形成され、および該ナノ構造の波峰がイオンの入射面に対して垂直方向に配向するように、分子状窒素N2+イオン流束を用いて半導体材料に照射するものである。ナノ構造振幅を増大させるため、更なる照射をO2+イオン流束を用いて、そのイオンボンバードメント面を窒素N2+イオンによるボンバードメント面に一致させて実施する。O2+イオンボンバードメントのエネルギーおよび角度は、形成できる波形ナノ構造の波長がN2+イオンおよびO2+イオンの単独照射におけるものと一致するように選択する。また、規則的な波形ナノ構造をヒ素、ガリウムおよびシリコンの構造体に形成する3つの変形体も開示される。 (もっと読む)

1 - 16 / 16

[ Back to top ]