Fターム[5F032AB01]の内容

素子分離 (28,488) | PN接合を用いる分離 (255) | 素子領域側面、底面をPN接合で分離するもの (114)

Fターム[5F032AB01]に分類される特許

1 - 20 / 114

半導体装置

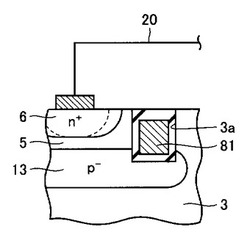

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域には、ドレイン領域となるn-型の拡散領域が形成されている。n-型の拡散領域の周囲を取囲むようにp型の拡散領域が形成されている。p型の拡散領域には、ソース領域となるn+型の拡散領域が形成されている。n-型の拡散領域の直下には、p-型の埋め込み層13が形成されている。n-型の半導体領域の領域には、高電位が印加されるn+型の拡散領域が形成され、そのn+型の拡散領域の表面上には電極が形成されている。電極とドレイン電極とは、配線20によって電気的に接続されている。配線20の直下に位置する部分に、p-埋め込み層13に達するトレンチ3aが形成されて、ポリシリコン膜81が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】異なる不純物濃度の埋め込み層を有する半導体装置を短時間かつ低コストで製造する方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の表面に第1の酸化膜11を形成する第1の酸化膜形成ステップと、フォトダイオードが形成される第1の領域に形成された前記酸化膜の一部を除去して第1の間隔で第1の開口部を形成すると共に、トランジスタが形成される第2の領域に形成された前記酸化膜を除去して前記半導体基板の表面を露出させる第1の開口部12を形成ステップと、前記第1の酸化膜をマスクとして利用して前記第1の開口部及び前記第2の領域に対して第1の不純物を注入する第1の不純物注入ステップと、前記第1の不純物を熱拡散させる第1の熱拡散ステップと、を有する。

(もっと読む)

半導体装置の製造方法

【課題】SON構造の半導体装置において、フォトリソグラフィー工程で高精度の位置合わせができ、プロセスラインの汚染を防止することができて、素子特性の劣化が防止され、信頼性の高い半導体装置の製造方法を提供する。

【解決手段】SON構造9上部のシリコン層32の段差18をアライメントマーク20として用いることによって、アライメントマーク20の形状崩れが防止されて、フォトリソグラフィー工程で高精度の位置合わせができるようになる。また、段差18が小さいためにフォトリソグラフィー工程で凹部へのレジストの残留やプロセス途中で発生するゴミの残留が防止され、プロセスラインの汚染が防止できる。その結果、素子特性の劣化が防止され、信頼性の高い半導体装置の製造方法を提供することができる。

(もっと読む)

半導体装置

【課題】出力トランジスタの形成領域から他の素子の形成領域への電子の移動を抑制する効果が高く、素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体基板SUBと、1対の注入元素子DRと、アクティブバリア構造ABと、p型接地領域PGDとを備える。半導体基板SUBは主表面を有し、かつ内部にp型領域を有する。1対の注入元素子DRは、p型領域上であって主表面に形成される。アクティブバリア構造ABは、主表面において1対の注入元素子DRに挟まれる領域に配置される。p型接地領域PGDは、主表面において1対の注入元素子DRに挟まれる領域を避けて1対の注入元素子DRおよびアクティブバリア構造ABよりも主表面の端部側に形成され、かつp型領域に電気的に接続された、接地電位を印加可能な領域である。p型接地領域PGDは、1対の注入元素子DRに挟まれる領域と隣り合う領域において分断されている。

(もっと読む)

半導体装置

【課題】半導体基板に向かって流れ込む回生電流又は寄生バイポーラトランジスタのオン電流を、チップサイズを増大させることなく低減できるLDMOSトランジスタの実現が課題となる。

【解決手段】N+型ドレイン層13等が形成されたN型エピタキシャル層5からなるN型層5aを、N型エピタキシャル層5の表面からN+型埋め込み層2まで延在するP型ドレイン分離層6で取り囲む。P型ドレイン分離層6とP型素子分離層3に囲まれたN型エピタキシャル層5からなるN型層5bにその表面から内部に延在するP型コレクタ層7を形成する。これにより第1導電型のドレイン分離層6をエミッタ、前記第2導電型の分離層5bをベース、前記コレクタ層7をコレクタとする寄生バイポーラトランジスタを形成しサージ電流を接地ラインに流す。

(もっと読む)

エピレス基板における分離型の相補型MOS装置

【課題】高い実装密度を得ることが可能な半導体装置の製造プロセスを提供する。

【解決手段】半導体装置を電気的に分離するための構造は、エピタキシャル層を含まない半導体基板240内にドーパントを打込むことにより形成される。この打込みに続き、極めて限られた熱収支に上記構造を晒すことでドーパントが顕著に拡散しないようにする。その結果として、上記分離構造の寸法が制限かつ規定され、こうして、エピタキシャル層を成長させる工程とドーパントを拡散させる工程とを含む従来のプロセスを用いて得られるよりも高い実装密度を得ることができる。

(もっと読む)

固体撮像装置及びその製造方法

【課題】素子を分離するための素子分離部による不具合の発生確率を低減する。

【解決手段】フォトダイオード310が内部に形成された半導体基板500と、素子分離部420とを備える。素子分離部420は、該素子分離部420の少なくとも一部が、半導体基板500に形成された溝410の内部に充填されるように形成される。素子分離部420は、溝410の内部の下方に形成されたシリコン酸化膜421と、溝410の内部の上方に形成されたシリコン酸化膜422とから構成される。シリコン酸化膜421の密度は、シリコン酸化膜422の密度より小さい。

(もっと読む)

半導体装置及びその製造方法

【課題】IGBT形成領域とその制御回路等形成領域とをPN接合分離法で分離し、且つIGBTからの漏れ電流が発生せず、制御回路等のCMOSトランジスタがラッチアップ等することのない高品質の半導体装置を実現する。

【解決手段】P型半導体基板1上に多層からなるN型エピタキシャル層3等を形成する。該N型エピタキシャル層3等をP+型分離層13等によりIGBT形成領域50と制御回路等形成領域40に分離する。該IGBT形成領域50の最下層の前記N型エピタキシャル層3と前記P型半導体基板1の双方に延在するN+型埋め込みガード層2を形成する。また該N+型埋め込みガード層2の端部と接続し前記エピタキシャル層3等の表面まで延在するN+型ガードリング9等を形成する。前記N+型埋め込みガード層2と該N+型ガードリング9等に囲まれた前記エピタキシャル層3等にIGBTを形成する。

(もっと読む)

素子分離領域を有する半導体装置とその製造方法

【課題】 素子分離領域の広がりによる素子形成領域間の拡大等の改善を図る。

【解決手段】 半導体基体11には、素子分離領域16が、所定の濃度をもって第1導電型不純物が導入された第1の選択的不純物導入領域17と、第1の選択的不純物導入領域17に比し低い所定の不純物濃度の第2導電型不純物が選択的に導入された第2の選択的不純物導入領域18とによって構成される。第2の選択的不純物導入領域18の不純物濃度の選定によって第1の選択的不純物導入領域17からの不純物の横方向拡散による広がり領域における第1導電型の打消しを行って、素子分離領域16の横方向の実質的広がりを抑制する。

(もっと読む)

半導体装置

【課題】出力用素子から半導体基板の内部に進入する電子により、被保護素子が誤動作を起こすことを抑制する半導体装置を提供する。

【解決手段】半導体基板と、出力用素子と、被保護素子TRSと、タップ部ATDと、第1のアクティブバリア構造ABRとを備える。第1のアクティブバリア構造ABRは、被保護素子TRSとタップ部ATDとの間に配置される。第1のアクティブバリア構造ABRは、p型不純物領域PSRに接続されたn型領域と、n型領域とオーミック接続されたp型領域とを含む。

(もっと読む)

半導体装置

【課題】第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供することを目的とする。

【解決手段】第1、第2素子形成領域20、30に形成された半導体素子のうち、第1素子形成領域20に形成された半導体素子を外部機器と接続し、第1素子形成領域20と第2素子形成領域30との間に、第1導電型層60と、当該第1導電型層60に挟まれる第2導電型層61とを配置し、第1、第2導電型層60、61の間に、オフ時に半導体層12の表面から埋込絶縁膜11に達し、第1、第2素子形成領域20、30との間を仕切る空乏層63、64を構成する。

(もっと読む)

固体撮像装置、及びその製造方法

【課題】光照射面側の素子分離を強化して、混色を低減させ、感度向上、素子分離部の暗電流低減できる固体撮像装置、及びその製造方法を提供すること。

【解決手段】n型の半導体基板30表面内に形成された前記n型の拡散層32を含み、前記半導体基板の裏面側から表面側に向かって照射された光により前記半導体基板内で生成された電子を蓄積する電荷蓄積部PDと、前記電荷蓄積部を挟み、前記半導体基板表面からこの半導体基板内に達するように形成されたp型の第1、第2拡散層(36)と、前記電荷蓄積部を電気的に分離し、前記半導体基板の前記裏面側が開口されるよう形成された第1、第2トレンチ55に埋め込まれたp型のa−アモルファスシリコン化合物(p型a−SiC)と、を具備する。

(もっと読む)

ガードリング構造を有する半導体デバイス、ディスプレイドライバ回路、及びディスプレイ装置

【課題】ガードリング構造を有する半導体デバイス、ディスプレイドライバ回路、及びディスプレイ装置を提供する。

【解決手段】本発明による半導体デバイスは、第1導電型の半導体基板と、半導体基板に既定の深さを有して形成された2以上の第2導電型の第1ウェル領域と、第2導電型の第1ウェル領域の内に既定の深さを有して形成された少なくとも一つの第1導電型の第2ウェル領域と、第1ウェル領域の間に位置し、第1ウェル領域と既定の間隔だけ離隔して既定の深さを有して形成された第2導電型のガードリング領域と、を含み、ガードリング領域は、システムグラウンド電圧に連結される。

(もっと読む)

トレンチにより制限された分離拡散領域を備えた相補型アナログバイポーラトランジスタ

【課題】表面上に素子をより高密度に実装する。

【解決手段】第1のトレンチと第2のトレンチとの間の位置において、エピタキシャル層の表面から基板へと下方に延在するドーパントのウェルは、エピタキシャル層の背景ドーピング濃度とは異なるドーピング濃度を有し、エピタキシャル層の残りの部分と第1および第2の接合を形成する。第1の接合は、第1のトレンチの底部から基板に延在し、第2の接合は、第2のトレンチの底部から前記基板に延在する。ウェルおよび第1および第2のトレンチは分離構造を構成し、分離構造は、分離構造の一方側のエピタキシャル層に形成された第1の素子と分離構造の他方側のエピタキシャル層に形成された第2の素子とを電気的に分離する。分離構造による電気的分離は第1および第2のトレンチとPN接合とによってもたらされ、ウェルは第1の導電型の材料でドープされ、基板およびエピタキシャル層は、第1の導電型とは反対の第2の導電型の材料でドープされ、第1および第2の接合はPN接合である。

(もっと読む)

半導体装置

【課題】バイポーラの高耐圧縦型PNPプロセスをベースにして、寄生PNPトランジスタに起因する漏洩電流の発生しない高耐圧IGBTを形成する。

【手段】P型半導体基板1に、IGBTのコレクタ電極15と電気的に接続するP+型コレクタ層8と、当該P+型コレクタ層8と連続するP+型埋め込み層4と、該P+型埋め込み層4の下層のN型埋め込み層2と、該P+型埋め込み層4と該N型埋め込み層2の間のN+型埋め込み層3とを形成する。また、N+型埋め込み層3の端部と一体となり、前記P型半導体基板1上に形成されたN型エピタキシャル層5の表面まで延在し、コレクタ電極15と電気的に接続されたN+型導電層7を形成する。

(もっと読む)

半導体装置の製造方法

【課題】CMP工程でその表面が研削され、平坦化された層間絶縁膜IL中にドライエッチングによりコンタクトホール20a等を形成する時、素子分離絶縁膜8a上に形成された最上層がシリサイド層12b、下層がポリシリコン層12aからなる配線層12の、該シリサイド層12bがオーバーエッチングにより消失することを防止する。

【解決手段】N+型埋め込み層2形成時に生じたシリコン段差に起因してN型エピタキシャル層4の表面にも段差が生じる。係る段差の高い部分に形成されたP型分離層5の上に素子分離絶縁膜8aを形成する。該素子分離絶縁膜8a上に上層がシリサイド層12b、下層がポリシリコン層12aからなる配線層12を形成するが、配線層12を形成する前に該素子分離絶縁膜8aの薄膜化を行い、配線層12最上層のシリサイド層12b表面とN+型ソース層15等の表面間の段差を、該素子分離絶縁膜8aの薄膜化する前に比べ小さくする。

(もっと読む)

固体撮像装置とその製造方法、及び電子機器

【課題】本発明は、感度ムラや、シェーディングが抑制された固体撮像装置を提供する。また、その固体撮像装置を用いた電子機器を提供する。

【解決手段】基板19と、基板19に形成された画素2と、隣接する画素間を分離する多段素子分離層31とを有して構成されている。画素2は、入射光に応じた信号電荷を生成、蓄積する受光部12と、基板19上に形成された画素電極14とを有して構成されている。多段素子分離層31は、複数段の不純物拡散層を有して構成されている。そして、受光部12を挟んで画素電極14に対向する領域の基板表面から深さ方向に形成された多段素子分離領域31は、基板19の光入射面から0.5μm〜1μmよりも深い領域において、受光部12から所定の距離W1だけ離して形成された下段素子分離層24,25を有している。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、半導体基板に欠陥が入るのを防止すること。

【解決手段】シリコン基板20に素子分離溝20aを形成する工程と、素子分離溝20a内に素子分離絶縁膜23を形成する工程と、素子分離絶縁膜23を形成した後、シリコン基板20に不純物を注入する工程と、不純物を注入した後、素子分離絶縁膜23とシリコン基板20のそれぞれの上面に、シリコン基板20の反りを抑制するカバー膜26を形成する工程と、カバー膜26が形成された状態で、シリコン基板20をアニールする工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置

【課題】 抵抗部と分離部の間のリーク電流を抑える技術を提供する。

【解決手段】 半導体装置100は、半導体基部10と分離部20と抵抗部30と電流補償部40を備えている。抵抗部30は、高電位側に接続される高電位側接続部位30Hと、低電位側に接続される低電位側接続部位30Lを有する。分離部20は、抵抗部30の高電位側接続部位30Hに隣接する第1部位20Hが高電位側に接続され、抵抗部30の低電位側接続部位30Lに隣接する第2部位20Lが低電位側に接続される。電流補償部40は、第1部位20Hと第2部位20Lの間の少なくとも一部に配置されている。電流補償部40と分離部20の間の抵抗値は、抵抗部30と分離部20の間の抵抗値よりも小さい。

(もっと読む)

半導体デバイス、半導体基板に分離されたポケットを形成する方法、半導体構成、PNPトランジスタ、横型NチャネルDMOSトランジスタ、横型トレンチDMOSトランジスタ

【課題】モジュール化された、相互作用しないやり方で、単一の半導体ウェハにともに接近して実装され、十分に分離された、最適化されたトランジスタまたは他のデバイスの任意の集合の作製を可能にする。

【解決手段】

一群の半導体デバイスが、エピタキシャル層を含まない基板に形成される。一実施例では、この一群は、5VのCMOSペア、12VのCMOSペア、5VのNPN、5VのPNP、いくつかの形状の横型トレンチMOSFET、および30V横型N−チャネルDMOSを含む。これらのデバイスの各々は、横方向かつ縦方向の双方において極めて小型であり、基板の他のすべてのデバイスから十分に分離され得る。

(もっと読む)

1 - 20 / 114

[ Back to top ]