Fターム[5F032DA77]の内容

Fターム[5F032DA77]に分類される特許

1 - 20 / 61

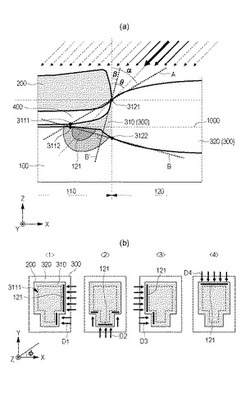

半導体装置の製造方法およびCMOSイメージセンサーの製造方法

【課題】 半導体装置に発生するノイズを低減する

【解決手段】 シリコン基板100の第1部分110を覆い、シリコン基板100の第1部分110に隣接する第2部分120を覆わない窒化シリコン膜200をマスクとしてシリコン基板100を熱酸化することにより、酸化シリコン膜300を形成する。窒化シリコン膜200をマスクとして酸化シリコン膜300のバーズビーク部310の下へ斜めイオン注入を行うことにより、不純物領域121を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体装置及びその製造方法

【課題】閾値電圧調整用金属を含む高誘電率絶縁膜を有するゲート絶縁膜を備えたn型MISトランジスタを有する半導体装置において、ゲート幅が狭くなっても、n型MISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】n型MISトランジスタnTrは、半導体基板1における素子分離領域32に囲まれた活性領域1aと、活性領域1a上及び素子分離領域32上に形成され且つ高誘電率絶縁膜12aを有するゲート絶縁膜13aと、ゲート絶縁膜13a上に形成されたゲート電極16aとを備えている。活性領域1aにおける素子分離領域32に接する部分のうち少なくともゲート絶縁膜13aの下側に位置する部分に、n型不純物領域28が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】溝部を絶縁膜で埋設する際に、溝部のアスペクト比が大きい場合であっても、内部にボイドを残存させることなく、溝部内に絶縁膜を充填する。これにより微細化した半導体装置の製造を容易に行うことを可能とする。

【解決手段】隣り合う凸部の間に形成される溝部の上端部においてオーバーハング形状を有すると共に、溝部の上部にボイドを有するように溝部内に溝部用絶縁膜を形成する。凸部の高さ方向に対して斜め方向から、溝部用絶縁膜に不純物をイオン注入することにより、溝部内に形成された溝部用絶縁膜の一部に不純物をドープする。溝部用絶縁膜の不純物がドープされた部分を除去した後、溝部内に溝部用絶縁膜を充填する。

(もっと読む)

固体撮像装置及びその製造方法

【課題】素子を分離するための素子分離部による不具合の発生確率を低減する。

【解決手段】フォトダイオード310が内部に形成された半導体基板500と、素子分離部420とを備える。素子分離部420は、該素子分離部420の少なくとも一部が、半導体基板500に形成された溝410の内部に充填されるように形成される。素子分離部420は、溝410の内部の下方に形成されたシリコン酸化膜421と、溝410の内部の上方に形成されたシリコン酸化膜422とから構成される。シリコン酸化膜421の密度は、シリコン酸化膜422の密度より小さい。

(もっと読む)

トレンチ分離型逆阻止MOS型半導体装置およびその製造方法

【課題】逆阻止用のトレンチを充填しなくても、ウエハプロセスを高良品率にすることのできるトレンチ分離型逆阻止MOS型半導体装置およびその製造方法を提供する。

【解決手段】第1導電型半導体基板と該半導体基板の第2主面に形成される第2導電型領域とにより構成される逆阻止接合を備え、前記半導体基板の第1主面から前記逆阻止接合に達する深さであって、該逆阻止接合を底面として前記半導体基板を囲む環状のトレンチと、該トレンチの側壁に、前記第2導電型領域と導電接続する第2導電型分離領域を有するトレンチ分離型逆阻止MOS型半導体装置において、高温水素アニール処理によりトレンチ103の開口部106をシリコン表面マイグレーションにより塞いでウエハ表面を平坦化させてトレンチ埋め込みレス分離構造とする。

(もっと読む)

半導体装置およびその製造方法

【課題】素子面積の増大を抑制しつつ、ハンプ特性を改善できる半導体装置およびその製造方法を提供する。

【解決手段】一導電型半導体基板100の一主面101にSTI構造の素子分離領域30を形成し、素子分離領域30上の端部に凹部13、14を有するゲート電極10を形成し、ゲート電極10をマスクにして一導電型不純物を斜めにイオン注入して、凹部13、14を介して素子領域50の端部領域53、54に不純物注入領域71、72を形成し、ゲート電極10をマスクにしてソース、ドレイン領域81、82を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】製造コスト削減、サイズ縮小ができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法であって、P型Si基板21の主面にトレンチ22を形成することによって、エンハンスメント型FET形成用の幅狭部分とでプレション型FET形成用の幅広部分とを含むアクティブ領域25を形成する工程と、主面の法線に対して30度〜45度の範囲内の注入角で、且つ、注入方向が法線を中心に相対的に回転するように、Si基板21に対してP型不純物を注入して、幅広部分にP型のチャンネルストッパー領域25aを形成すると共に、幅狭部分にP型チャンネル拡散領域25bを形成する工程と、トレンチ22をトレンチ素子分離絶縁層26で埋める工程と、ゲート絶縁膜27を形成する工程と、Si基板21上にN型不純物を注入して第2の部分にN型チャンネル拡散領域28を形成する工程と、ゲート電極29を形成する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】寄生MOSの形成を抑制し、且つ狭チャネル化を低減した半導体装置の製造方法を提供する。

【解決手段】支持基板2と絶縁層3と半導体層4とを含むSOI基板1に、ソース領域及びドレイン領域が第1導電型であるトランジスターを形成する半導体装置の製造方法であって、半導体層4上に、第1の耐酸化性膜6a’を形成する工程と、第1の耐酸化性膜6a’をマスクにして、第1導電型とは導電性の異なる、第2導電型の不純物7を半導体層4に注入する工程と、第2導電型の不純物7を半導体層4に注入する工程の後、第1の耐酸化性膜6a’の側面に第2の耐酸化性膜6b’を形成する工程と、第1の耐酸化性膜6a’及び第2の耐酸化性膜6b’をマスクにして、素子分離層8を形成する工程と、素子分離層8を形成する工程の後、第1の耐酸化性膜6a’及び第2の耐酸化性膜6b’を半導体層4上から除去する工程とを有することを特徴とする半導体装置100の製造方法。

(もっと読む)

集積化半導体装置及びその製造方法

【課題】 SOIウェーハを使用する集積化半導体装置の結晶欠陥の低減、耐圧向上、リーク電流の低減が要求されている。

【解決手段】 SOIウェーハにトレンチ16を形成する時に、トレンチ16の底に傾斜面17を有するように半導体層13を残存させる。この傾斜面17に沿って厚いシリコン酸化膜(第2の絶縁膜)25aを形成する。この厚いシリコン酸化膜(第2の絶縁膜)25aによって埋込み絶縁層12と半導体層13との界面への酸素の侵入を防ぐ。

(もっと読む)

半導体装置及びその製造方法

【課題】結晶欠陥の発生が抑制されたSTI型素子分離領域を有する半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板10にトレンチ33を形成する工程と、トレンチ33の内面に沿って、トレンチ33の側面上よりも底面上の膜厚が厚い第1の絶縁膜12aを形成する工程と、第1の絶縁膜12aを通して不純物をイオン注入することにより半導体基板10におけるトレンチ33の周辺部に不純物注入層13Aを形成する工程と、第1の絶縁膜12aの上にトレンチ33を埋める第2の絶縁膜12bを形成することにより、第1の絶縁膜12aと第2の絶縁膜12bとを有する素子分離領域12を形成する工程とを備えている。結晶欠陥が修復された状態でイオン注入を行うことができるので、半導体基板10の結晶欠陥を低減することができる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 活性領域の表層部を熱酸化したときに、活性領域の縁に酸化膜の薄い部分が発生することを防止することができる半導体装置の製造方法を提供する。

【解決手段】 半導体基板の表層部に、該半導体基板の表面よりも上方に突出した素子分離絶縁膜を形成することにより活性領域を画定する。活性領域の表面のうち、素子分離絶縁膜に接する一部の領域が、素子分離絶縁膜の突出部の陰になる条件で、半導体基板の表層部に、半導体基板の表層部の酸化速度を低下させる元素を斜め方向から注入する。この元素の注入後、活性領域の表面を熱酸化することにより、第1の酸化膜を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】

STIによる新たな課題を抑制できる半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、(a)Si基板上方に素子分離領域を包含する平面形状の開口を有するマスク層を形成する工程と、(b)マスク層の開口側壁上に、マスク層に対して選択的に除去可能な材料のサイドウォールスペーサを形成する工程と、(c)マスク層、サイドウォールスペーサをエッチングマスクとして、Si基板をエッチングしてトレンチを形成する工程と、(d)トレンチを埋める絶縁素子分離領域を形成する工程と、(e)サイドウォールスペーサを選択的に除去する工程と、(f)Si基板上方から、窒素をイオン注入する工程と、(g)マスク層を除去する工程と、(h)絶縁素子分離領域によって画定された活性領域に半導体素子を形成する工程と、を含む。

(もっと読む)

固体撮像装置

【課題】STI(素子分離部)界面近傍の応力に起因する暗電流を低減するとともに、画素部の微細化を行っても高感度を維持することができる固体撮像装置を提供することにある。

【解決手段】複数の画素部12がシリコン基板11上に形成されており、各画素部12を構成する光電変換部10は、シリコン基板11内に形成された絶縁膜からなる素子分離部13で電気的に分離されている。そして、素子分離部13で区画された光電変換部10において、素子分離部13と接する辺の結晶方向が<00−1>方向に形成されている。

(もっと読む)

不揮発性半導体メモリ及びその製造方法

【課題】周辺トランジスタの駆動特性の劣化を抑制できる不揮発性半導体メモリを提供する。

【解決手段】不揮発性半導体メモリは、第1の領域を取り囲む有機物を含む第1の素子分離絶縁膜9と、第1の領域内に配置されるメモリセルと、第2の領域を取り囲む有機物を含む第2の素子分離絶縁膜9と、第2の領域内に配置される周辺トランジスタHVTrと、第2の素子分離絶縁膜9の側面に沿って、半導体基板1内に設けられる不純物層7と、素子分離絶縁膜9の底面に沿って、p型の第1の不純物層8とを備える。素子分離絶縁膜9の側面に沿って不純物層7を設けることで、有機物に起因する固定電荷トラップの影響を緩和でき、不揮発性半導体メモリに用いられる周辺トランジスタ、例えばイントリンシック領域内に設けられるnチャネル型の高耐圧系MISトランジスタの逆ナローチャネル効果を抑制できる。

(もっと読む)

イオン注入方法および半導体装置の製造方法

【課題】バッチ式イオン注入装置を用いてウェルを形成した場合に、ウェル分離耐圧の低下を抑制することができるイオン注入方法および半導体装置の製造方法を提供する。

【解決手段】複数の半導体基板が載置されたディスク3が、イオンビーム1と垂直なX−Y面と、ディスク3の回転面32内においてY軸に直交する直線とのなす角が第1の角度β1となる状態で配置される。当該状態で、ディスク3をディスク回転軸53周りに回転させてイオンビーム1を照射することにより、第1導電型の不純物が半導体基板2に注入される。次いで、ディスク3が、X−Y面と、ディスク3の回転面32内においてY軸に直交する直線とのなす角が第2の角度β2となる状態で配置される。当該状態で、ディスク3をディスク回転軸53周りに回転させてイオンビーム1を照射することにより、第2導電型の不純物が半導体基板2に注入される。

(もっと読む)

半導体装置の製造方法

【課題】 製造後の半導体装置の電気的特性に与える影響を抑制しつつ、ハンプ現象の発生を防止可能な、トレンチ構造を有する半導体装置の製造方法を提供する。

【解決手段】 半導体基板10上にパッド絶縁膜(11、12)を成膜後、所定形状にパターニングした後、ウェル形成領域以外の領域をレジスト膜13でマスクする。その後、当該ウェル形成領域に対して、ウェル形成のための第1イオン注入処理を実行してウェル21を形成し、さらに、このレジスト膜13を残存させたままの状態で、ウェル21の上面に形成されているパッド絶縁膜の側壁面に対して斜め方向から第2イオン注入処理を実行する。その後、パッド絶縁膜をマスクとして半導体基板10をエッチングしてトレンチを形成した後、トレンチ内を絶縁膜で埋め込み、平坦化処理をする。そして、パッド絶縁膜を除去後、ゲート酸化膜成膜等の通常トランジスタ形成工程と同様の工程を実行する。

(もっと読む)

半導体装置の製造方法及びイメージセンサ装置

【課題】センサ素子間のクロストークを防止したイメージセンサ半導体装置を提供する。

【解決手段】本発明は、イメージセンサ半導体装置を提供する。第1の型の導電性を有する半導体基板を提供する。複数のセンサ素子が、半導体基板に形成される。分離構造が、複数のセンサ素子間に形成される。イオン注入処理が、少なくとも2つの異なる注入エネルギーを用いて分離構造のほぼ下に、第1の型の導電性を有するドープ領域を形成するために実施される。

(もっと読む)

半導体装置の製造方法

【課題】空洞部に対して熱酸化を行い、埋め込み絶縁層を形成した際に生じる隙間に起因する剥がれを確実に防止し、良好なSOI構造を形成することによってSOI構造を有する優れた半導体装置を製造することのできる、方法を提供する。

【解決手段】埋め込み絶縁層14を形成した後、半導体基板1の能動面側に非晶質半導体を堆積し、支持体12の表面と埋め込み絶縁層14の側面部とに非晶質半導体膜を形成するとともに、埋め込み絶縁層14中に非晶質半導体を充填する。次いで、非晶質半導体膜及び非晶質半導体を共に結晶化し、多結晶半導体膜及び多結晶半導体16aにし、さらに多結晶半導体膜を熱酸化して熱酸化膜17を形成する。その後、支持体12とその表面の熱酸化膜17とを除去し、第2半導体層6を露出させ、SOI構造を得る。

(もっと読む)

低暗電流撮像装置のアイソレーション方法

イメージセンサの感光性領域間のシリコンアイソレーションインタフェースにパッシベーション層を形成する方法であって、本方法は、入射光に反応して電荷を収集する、複数の離隔した感光性領域を持つ基板を用意し、感光性領域の間において基板にトレンチをエッチングし、感光性領域の間のトレンチがマスクで覆われないよう、感光性領域に複数のマスクを形成し、第1の低用量でイメージセンサをインプラントしてトレンチをパッシベートし、トレンチに誘電体を充填して感光性領域の間にアイソレーションを形成し、トレンチアイソレーションの表面コーナーのパッシベーションインプランテーションが可能となるよう、感光性領域を覆う一方で、アイソレーショントレンチの表面コーナーを覆わない複数のマスクを形成し、イメージセンサを第2の低用量でインプラントしてトレンチが形成されたアイソレーション領域の表面コーナーをパッシベートすることを含む。  (もっと読む)

(もっと読む)

1 - 20 / 61

[ Back to top ]