Fターム[5F033JJ18]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | 高融点金属 (7,010) | Ti (2,052)

Fターム[5F033JJ18]に分類される特許

1 - 20 / 2,052

半導体装置およびその製造方法

半導体ウェハ、半導体装置及びその製造方法

銅を含む電極連結構造体

半導体装置及びその製造方法

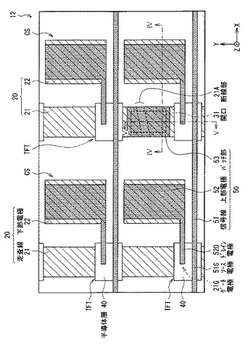

薄膜トランジスタアレイおよびその製造方法、並びに表示装置

【課題】配線密度を高くしすぎることなく断線を修復することが可能であり、フレキシブル性を持たせる場合に短絡や断線などを抑えることが可能な薄膜トランジスタアレイおよびその製造方法、並びに表示装置を提供する。

【解決手段】第1導電層と、前記第1導電層の少なくとも一部に対向して、前記第1導電層に合わせた平面形状の開口を有する絶縁膜と、前記開口を塞ぐと共に前記開口内で前記第1導電層に接するパッチ部を含む第2導電層とを備えた薄膜トランジスタアレイ。

(もっと読む)

半導体装置、半導体装置の製造方法、および電子機器

【課題】アスペクト比の異なる複数の開口下部に接続される配線に対して最適な処理を施すことができるようにする。

【解決手段】半導体装置の製造方法において、第1の半導体基板と第2の半導体基板が接合された半導体基板の第1の開口の下部配線と、貫通接続孔と異なるアスペクト比の第2の開口の下部配線に対して、バリアメタル膜の成膜と、スパッタガスによる物理エッチングを同時に行うアンカー処理工程が含まれる。本技術は、例えば、固体撮像装置などの半導体装置に適用できる。

(もっと読む)

配線の形成方法、電子素子、および表示装置

【課題】物理的な版を必要とせず、微細な導電パターンを形成でき、パターン変更に対して柔軟に対応できる配線の形成方法を提供する。

【解決手段】本発明では、基板上に、エネルギー付与によって臨界表面張力が変化する材料を含有する濡れ性変化層を形成する工程と、前記濡れ性変化層に選択的にレーザ光を照射して、前記濡れ性変化層の臨界表面張力が高くなるように変化させた高表面エネルギー領域部を前記濡れ性変化層に形成する工程と、前記高表面エネルギー領域部に導電性インクを塗布し、前記高表面エネルギー領域部上に配線を形成する工程と、を有し、前記濡れ性変化層と前記高表面エネルギー領域部とには段差がなく、前記配線は前記高表面エネルギー領域部上に形成されていることを特徴とする配線の形成方法が提供される。

(もっと読む)

半導体装置およびその製造方法ならびに表示装置および電子機器

【課題】配線層の膜応力を低減し、製造歩留まりを向上することが可能な半導体装置およびその製造方法並びに表示装置および電子機器を提供する。

【解決手段】本技術の半導体装置は、一方向に延在する複数の第1配線層と、第1配線層の間に設けられた第1配線層よりも膜厚が薄いゲート電極と、第1配線層およびゲート電極上に形成された絶縁膜と、絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、半導体層上に設けられた層間膜と、層間膜上に形成されると共に、層間膜に設けられた貫通孔を介して半導体層と接続された第2配線層とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極に、加工性と機能性の双方を高めた絶縁リングを設ける。

【解決手段】ドライエッチングにより形成された絶縁リング用環状溝CGa,CGbには絶縁物質が充填され、単独絶縁リング62a,62bが形成されている。また、ドライエッチングにより形成されたTSV用貫通孔THa,THbの側壁は、絶縁膜で覆われ、TSV側壁絶縁リング61a,61bが形成されている。また、TSV用貫通孔THa,THbの残りの部分には、シード/バリア層71を介して、例えば銅のような誘電体が充填されており、それによりTSV7が形成されている。TSV側壁絶縁リング61の厚さは、絶縁リング用環状溝CGの幅、言い換えれば、単独絶縁リング62の厚さの約半分である。従って、TSV側壁絶縁リング61の厚さは、TSV側壁絶縁リングを単独で設けた場合のその厚さの3分の1程度にすることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極が絶縁膜で被覆されていようがいまいが、貫通電極と配線の接触面積を確保すること。

【解決手段】本実施形態に係る半導体装置は、第1の半導体チップ200と、第1の半導体チップ200上に積層された第2の半導体チップ300と、第1の半導体チップ200と第2の半導体チップ300とを接続する貫通電極120と、を有している。貫通電極120は、第1の貫通電極部122と第2の貫通電極部124を有している。第1の貫通電極部122は、第2の半導体チップ300において、第2の絶縁膜42の上面から第2の配線32の上部まで設けられている。第2の貫通電極部124は、第1の貫通電極部122の下面と繋がっており、かつ第2の配線32と同一層から第2の半導体チップ300の第1の配線30上部まで設けられている。第1の貫通電極部122と第2の貫通電極部124の孔径は、平面視で、第1の貫通電極部122の孔径の方が大きい。

(もっと読む)

微細空間内に機能部分を形成する方法

【課題】低温分散系機能性材料を用いて、微細空間内に空隙、隙間、または空洞のない機能部分を形成する方法を提供する。

【解決手段】熱溶解性を有する機能性微粉末52を、液状分散媒51中に分散させた分散系機能性材料5を、微細空間3内に充填する。次に、微細空間3内の液状分散媒51を蒸発させる。次に、熱処理により機能性微粉末52を熱溶解させた後、加圧しながら冷却する。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜上に良質のグラフェンを形成しうる半導体装置の製造方法を提供する。

【解決手段】第1の基板上に触媒金属膜を形成する工程と、触媒金属膜を触媒としてグラフェンを形成する工程と、グラフェン上に第1の絶縁膜を形成する工程と、第1の絶縁膜上に第1の金属膜を形成する工程と、第2の基板上に、第2の金属膜を形成する工程と、第1の金属膜の表面と第2の金属膜の表面とを対向させ、第1の金属膜と第2の金属膜とを接合する工程と、第1の基板を除去する工程とを有する。

(もっと読む)

貫通電極基板の製造方法

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板の製造方法は、ウェハ状の基板に前記基板を貫通しない複数の有底孔を形成し、前記基板及び前記有底孔の表面に絶縁膜を形成し、前記有底孔が開口する側の前記基板及び前記有底孔の絶縁膜上に金属からなるシード膜を形成し、前記シード膜に第1の時間直流電流を供給する電解めっき法により、前記シード層が形成されている面の前記有底孔の底部に金属層を形成し、前記シード膜及び前記金属層にパルス電流を供給する電解めっき法により、前記有底孔内に金属材料を充填して導通部を形成し、前記有底孔が形成されている側と反対側の前記基板の表面を、前記導通部の表面が露出するまで研磨する。

(もっと読む)

半導体装置の設計方法、半導体装置の製造方法および半導体装置

【課題】半導体装置の性能を向上させる。

【解決手段】半導体装置の設計フローは、プラグPGに接続された配線M1を含むチップレイアウトを設計するステップと、設計されたチップレイアウトにおけるプラグPGに対する配線M1のマージンを、プラグPGに対する配線M1のリセス量に応じて修正するステップとを有している。この修正ステップは、テストウエハに試験用プラグとそれに3次元的に接続された試験用配線とを含むテストパターンを形成するサブステップと、試験用配線の配線幅および配線密度と試験用プラグに対する試験用配線のリセス量との相関を調べるサブステップを有している。更に、得られた相関に基づいてプラグPGに対する配線M1のリセス量を予測するサブステップと、予測されたリセス量に応じてプラグPGに対する配線M1のマージンを修正するサブステップを有している。

(もっと読む)

半導体ウェハ、半導体装置及びその製造方法

【課題】アライメントマークに集中する応力の方向依存性を低減して、クラックを発生しにくくする。

【解決手段】基板の第1の主面に、環状の第1の溝及びドット形状の第2の溝を形成する。第1及び第2の溝を埋め込むように絶縁膜を形成した後、基板の第1の主面にフォトレジスト膜を形成する。絶縁膜で埋め込まれた第2の溝の基板上での位置を基準として位置合わせした第1のパターンを、フォトレジスト膜に転写する。絶縁膜で埋め込まれた環状の第1の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する。

(もっと読む)

半導体装置の製造方法

【課題】接続孔部分における電気的特性のばらつきを低減することにより、半導体装置の信頼性および製造歩留まりを向上させることのできる技術を提供する。

【解決手段】成膜装置のドライクリーニング処理用のチャンバ57に備わるウエハステージ57a上に半導体ウエハSWを置いた後、還元ガスを供給して半導体ウエハSWの主面上をドライクリーニング処理し、続いて180℃に維持されたシャワーヘッド57cにより半導体ウエハSWを100から150℃の第1の温度で熱処理する。次いで半導体ウエハSWをチャンバ57から熱処理用のチャンバへ真空搬送した後、そのチャンバ57において150から400℃の第2の温度で半導体ウエハSWを熱処理することにより、半導体ウエハSWの主面上に残留する生成物を除去する。

(もっと読む)

半導体集積回路装置

【課題】チップあたりの端子数の増大に伴って、フリップチップ実装が種々の形態で実施されている。しかし、バンプピッチの微細化およびバンプの鉛フリー化によって、エレクトロマイグレーション耐性の確保がますます重要となっている。

【解決手段】本願の発明は、フリップチップ型の半導体集積回路装置において、チップの第1の主面上に形成された多数のUBMパッド状の各々に設けられた半田バンプの中間部には、上下を分割する前記半田バンプとは異なる材質の金属隔壁が設けられているものである。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化されたトランジスタのオン特性を向上させる。微細化されたトランジスタを歩留まりよく作製する。

【解決手段】一対の低抵抗領域及び該低抵抗領域に挟まれるチャネル形成領域を含む酸化物半導体層と、ゲート絶縁層を介してチャネル形成領域と重畳する第1のゲート電極層と、第1のゲート電極層のチャネル長方向の側面及びゲート絶縁層の上面と接し、一対の低抵抗領域と重畳する一対の第2のゲート電極層と、第2のゲート電極層上の、側端部を第2のゲート電極層の側端部と重畳する一対の側壁絶縁層と、を有する半導体装置を提供する。

(もっと読む)

半導体装置、及びその製造方法

【課題】TSV付き半導体装置において、貫通孔側面すべてにバリア及びシード層を成膜しないことで、空隙の発生を防止する。

【解決手段】

第1の溝部、及び前記第1の溝部より水平断面積が小さい第2の溝部からなる凸状溝部を画成し、且つ、前記第1及び第2の溝部により両端を開口する貫通ビアホールが形成される半導体基板と、前記第1の溝部の内面から、前記第2の溝部の側面の一部まで被覆して、前記貫通ビアホールの側面に隆起するバリア層およびシード層と、前記シード層の表面上、及び、前記シード層で被覆されていない前記第2の溝部内部に形成されて、前記半導体基板の両表面から露出する電極と、を備える半導体装置が提供される。

(もっと読む)

1 - 20 / 2,052

[ Back to top ]