Fターム[5F033QQ14]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | イオンミリング、スパッタエッチング (405)

Fターム[5F033QQ14]に分類される特許

401 - 405 / 405

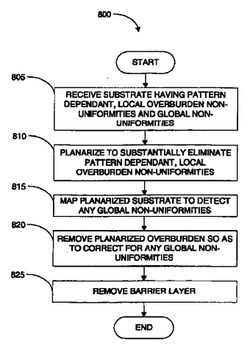

改良されたグローバルデュアルダマシン平坦化のためのシステム、方法、及び装置

【課題】

【解決手段】パターン化半導体基板(100)を平坦化する方法及びシステムは、パターン化半導体基板を受領する工程を含む。パターン化半導体基板(100)は、パターン内の多数の特徴部に充填された導電相互接続材料(120)を有する。導電相互接続材料は、過堆積(112)を有する。過堆積は、局所的な不均一性を有する。過堆積の全体部は、過堆積(120)を平坦化するために除去される。実質的に局所平坦化された過堆積は、大域的な不均一性を決定するためにマッピングされる。実質的に局所平坦化された過堆積は、大域的な不均一性を実質的に除去するためにエッチングされる。

(もっと読む)

配線用シード膜および半導体装置の配線方法

【課題】 低コストにて歩留まり,信頼性,電気的特性の高い半導体装置を作製する。

【解決手段】 絶縁膜60上の下層絶縁膜61に銅の下層配線62を形成(S61)した後、プラズマCVD法により層間絶縁膜63,ストッパ膜64を順次形成し、ストッパ膜64における下層配線62上に孔64aを形成してから、ドライエッチングして層間絶縁膜63にコンタクトホール63aを形成する(S62)。その後、上層絶縁膜65を形成しマスク66を介してドライエッチングすることにより、上層絶縁膜65に溝部65aを形成すると共に、コンタクトホール63a中の上層絶縁膜65を除去する(S63)。そして、バリア膜67を形成(S64)した後、Cu−Ni膜,Cu−Zn膜,Cu−Zn−Ni膜のうち何れかを堆積してシード膜68を形成する(S65)。

(もっと読む)

配線構造

【課題】 銅を配線材として用いても、微細な配線構造の形成が可能で、製造の工程数が少なく、低コスト化が可能な配線構造を提供する。

【解決手段】 半導体素子が形成された基板上に絶縁膜103が多層形成され、絶縁膜103に形成された配線溝およびビアホールに金属配線剤が充填されて、配線および接続プラグが形成された配線構造において、絶縁膜103のうち少なくとも一層が対電子線感光性を有する材料から形成されており、絶縁膜103の層間にはバリア絶縁膜104を有し、前記金属配線剤は銅を含むものである。

(もっと読む)

配線構造の製造方法

【課題】 銅を配線材として用いても、微細な配線構造の形成が可能で、製造の工程数が少なく、低コスト化が可能な配線構造の製造方法を提供する。

【解決手段】 配線構造の製造方法が、半導体素子201の上にWプラグ203(下層配線)が形成された基板上に、対電子線感光性を有する材料を含む第二層間絶縁膜204(絶縁膜)を形成する工程と、第二層間絶縁膜204に電子線を照射して、第二層間絶縁膜204を露光する工程と、第二層間絶縁膜204を現像して未露光部を除去し、配線溝および/またはビアホールおよび/またはコンタクトホールを形成する工程とを有する。

(もっと読む)

多層配線構造の製造方法及びその構造

【課題】 上層配線層と下層配線層とを、アスペクト比の高いビアコンタクトで接続した多層配線構造を提供する。

【解決手段】 多層配線構造のビアコンタクト形成工程が、ビアホールの底面上に触媒層を設け、触媒層上にビアホールの上方に向ってめっき金属層を成長させ、めっき金属層でビアホールを充填する無電解めっき工程からなる。

(もっと読む)

401 - 405 / 405

[ Back to top ]