Fターム[5F033QQ84]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 熱処理 (5,181) | 熱処理を続けて2回以上行うもの (74)

Fターム[5F033QQ84]に分類される特許

41 - 60 / 74

低誘電率層間絶縁膜、それを有する基板およびその製造方法

【課題】誘電率が低く、かつ誘電率の経時安定性、機械強度、密着性等の特性が良好な絶縁膜の提供。

【解決手段】有機化合物と空孔形成剤とを含む膜形成用組成物を基板上に塗布して前記基板上に皮膜を形成し、前記皮膜を硬化し、その後、前記皮膜をポアシール剤を含む超臨界媒体で処理して得られる、低誘電率層間絶縁膜。

(もっと読む)

絶縁膜形成用組成物および電子デバイス

【課題】 低誘電性であり、かつ塗膜形成後の経時によって一旦上昇した誘電率を加熱処理によって回復させる能力(k値回復性)を良化させた絶縁膜形成用組成物を提供する。

【解決手段】 (A)少なくとも一種の有機ポリマーまたは2つ以上の不飽和基を置換基として有するカゴ型シルセスキオキサン化合物を重合させた高分子化合物、(B)溶剤、(C)下記一般式(C-1)〜(C-3)の何れかで表される少なくとも一種の有機シリコーン化合物を含有することを特徴とする。

【化1】

(R1はメチル基等を表し、x1は0〜95mol%, x2は5〜100mol%、x1+ x2 = 100mol%であり、R2, R3はアルキル基等を、R4はメチル基等を表し、X3は5〜100mol%, x4は0〜95mol%、x3 +

x4 = 100mol%であり、Rfはフルオロアルキル基を表し、x5は0〜95mol%, yは5〜100mol%、x5 + x6 = 100mol%である。)

(もっと読む)

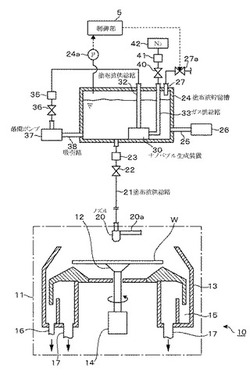

半導体装置の製造方法、半導体製造装置及び記憶媒体

【課題】基板上にシリコンを含む低誘電率膜を塗布法により形成するにあたり、簡便な方法により低誘電率膜中に気孔を形成すること。

【解決手段】低誘電率膜の前駆体であるシリコンを含む化合物の塗布液中に、負電荷を持ち、かつ浮力がほぼゼロの極めて小さな気泡であるナノバブルを導入し、この塗布液を基板上に塗布した後に、基板を加熱して低誘電率膜を形成する。このナノバブルが負電荷を持っているので、凝集しにくく、溶液中に均一に分散し、また基板の加熱後にも気泡として低誘電率膜中に取り込まれるため、均一で小さな気孔を形成することができる。

(もっと読む)

CMP後のウェーハを洗浄するための熱的方法

【解決手段】化学機械研磨後に半導体ウェーハを洗浄するための方法を提供する。方法の一例では、ウェーハに酸化環境における熱処理を施し、その後、還元環境における熱処理を施す。酸化環境における熱処理では、残留物を除去すると共に、露出した銅を酸化して酸化銅層を形成する。還元環境における熱処理では、その後、酸化銅を元素銅へ還元する。これにより、露出した銅は清浄となり、無電解メッキ等、更なる処理のための状態となる。 (もっと読む)

半導体製造方法および半導体製造装置

【課題】半導体装置のSOD膜形成工程において、下層にダメージを生じることなくリワークを可能とする半導体製造方法および半導体製造装置を提供する。

【解決手段】ウェハを保持し、これを回転させながら、ウェハ上に絶縁膜を形成するための薬液を供給して、塗布膜を形成し、塗布膜が形成されたウェハについて、移動および加熱処理を行うことなく非接触で表面検査を行い、表面検査により不良と判断されたウェハ上に、溶媒を供給しながら回転させることにより、塗布膜を除去する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】配線溝に埋設された銅膜(銅配線)の抵抗を低減することができる、半導体装置の製造方法および半導体装置を提供する。

【解決手段】絶縁膜1の表面に、配線溝2が形成された後、その配線溝2の内面を含む絶縁膜1の表面上に、CuおよびMnの合金からなる合金膜3が被着される。この合金膜3の被着後、合金膜3(絶縁膜1)上に、Cu膜4が配線溝2を埋め尽くすように積層される。その後、1回目の熱処理が行われて、合金膜3と絶縁膜1との界面に、MnxSiyOz(x,y,z:零よりも大きい数)からなるバリア膜5が形成される。次いで、Cu膜4およびバリア膜5の配線溝2外の各不要部分が除去される。その後、2回目の熱処理が行われる。この熱処理により、配線溝2上にMnが析出する。そして、配線溝2上に析出したMnが除去される。

(もっと読む)

絶縁膜の製造方法、絶縁膜、積層体および電子デバイス

【課題】 誘電率、密着性、機械強度、耐熱性等の膜特性が良好な絶縁膜の製造方法、絶縁膜、絶縁膜の積層体および電子デバイスを提供する。

【解決手段】 膜形成用組成物を塗布して形成した膜に、少なくとも二つのエネルギー線種の高エネルギー線を連続して照射し、前記膜を硬化させる硬化工程を有することを特徴とする絶縁膜の製造方法。該製造方法により製造された絶縁膜、該絶縁膜を積層してなる積層体およびこれらを用いてなる電子デバイス。

(もっと読む)

半導体装置及びその製造方法

【課題】フルシリサイド化されたゲート電極を有する半導体装置の製造方法において、活性領域と素子分離領域との段差による影響を受けることなく、活性領域上と素子分離領域上とに形成されたそれぞれのゲート電極形成膜及びゲート配線形成膜の露出を精度良う。

【解決手段】活性領域11を囲む素子分離領域12が形成された半導体基板10の上に形成された保護膜15a及び保護膜15bを覆うように下地保護膜19及び層間絶縁膜20を形成した後、化学機械研磨(CMP)法により、保護膜15aの上面が露出するまで、層間絶縁膜20、下地保護膜19及び保護膜15bを研磨除去する。

(もっと読む)

ギ酸銅錯体、銅粒子の製造方法および配線基板の製造方法

【課題】簡便かつ低コストに、銅粒子を製造する方法および当該銅粒子を分散させた液体材料を用いた配線基板の製造方法、ならびに、当該銅粒子を製造するために用いられるギ酸銅錯体を提供すること。

【解決手段】本発明は、下記一般式(1)

(式中、Cuは2価の銅、R1およびR2はそれぞれ置換基を有していてもよい脂肪族炭化水素基を示す。)で表されるギ酸銅錯体の前記2価の銅が0価の銅に還元されるとともに、前記ギ酸配位子が二酸化炭素に酸化されるように前記ギ酸銅錯体を分解することにより銅粒子を得る銅粒子の製造方法、当該銅粒子を分散させた液体材料を基板に塗布する配線基板の製造方法、上記一般式(1)で表されるギ酸銅錯体を提供することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 アルミ配線がゲート電極を覆うMOSトランジスタにおいて、ゲート電極が受けたプラズマダメージにより発生するしきい値電圧のバラツキを防止する。

【解決手段】 BPSG膜デポジション後のウエハを縦型熱処理装置に導入し、まず、BPSG膜を920℃の窒素熱処理によって膜の緻密化及び平坦化処理を行い、次いで、連続して430℃の水素熱処理を施す。これにより、工程を増やすことなく、しきい値バラツキを防止できる。

(もっと読む)

半導体装置の製造方法

【課題】接続孔部分における電気的特性のばらつきを低減することにより、半導体装置の信頼性および製造歩留まりを向上させることのできる技術を提供する。

【解決手段】成膜装置のドライクリーニング処理用のチャンバ57に備わるウエハステージ57a上に半導体ウエハSWを置いた後、還元ガスを供給して半導体ウエハSWの主面上をドライクリーニング処理し、続いて180℃に維持されたシャワーヘッド57cにより半導体ウエハSWを100から150℃の第1の温度で熱処理する。次いで半導体ウエハSWをチャンバ57から熱処理用のチャンバへ真空搬送した後、そのチャンバにおいて150から400℃の第2の温度で半導体ウエハSWを熱処理することにより、半導体ウエハSWの主面上に残留する生成物を除去する。

(もっと読む)

導電性パターンの形成方法、およびそれを用いた有機トランジスタの製造方法

【課題】 高い配置精度を有する導電性パターンを、簡便な工程で得ることのできる手段を提供すること。

【解決手段】 基板1表面上にあらかじめ導電性パターンに応じて形成した凹部2に、機能液を注入し、機能液を導電膜6に変換することにより導電性パターンを形成させる。これにより、高精度に配置された導電性パターンを、大掛かりな設備を必要とせずに形成させることができる。しかも、材料を無駄に廃棄することがないので、材料使用率を向上させることができる。

(もっと読む)

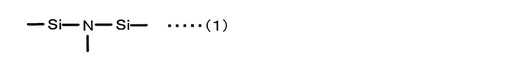

絶縁膜形成用組成物、半導体装置用絶縁膜、その製造方法および半導体装置

【課題】低誘電率で、かつ、優れた耐ストレス性と優れた耐クラック性とを有する半導体装置用絶縁膜を得ることができる絶縁膜形成用組成物、その絶縁膜形成用組成物から得られる半導体装置用絶縁膜および、その半導体装置用絶縁膜を利用して得られる高品質で信頼性の高い半導体装置を歩留まりよく提供する。

【解決手段】 本絶縁膜形成用組成物は、実質的に炭素とケイ素と水素とのみからなる鎖部分を主鎖とし、かつ、主鎖以外の部分に窒素を含有するポリマーを含んでなる。ポリマー中に、窒素が、式1で表される構造要素として存在することが好ましい。

【化17】 (もっと読む)

(もっと読む)

デバイスとその製造方法、配線形成方法及び電気光学装置並びに電子機器

【課題】平坦性の高いパターンを形成可能とする。

【解決手段】基板Pに配線形成材料を含む液状体を塗布する工程と、塗布した液状体を焼成する工程とを有する。配線形成材料に対して不活性な雰囲気下で前記焼成を行う。

(もっと読む)

半導体装置の製造方法

【課題】 凹部が形成された絶縁性表面上に導電部材を堆積させ、その後、CMPを行う際に、欠陥が発生することを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板上に形成された絶縁膜に凹部を形成する。(b)前記凹部を形成した後、基板を10℃/s以下の昇温速度で300℃以上の温度まで昇温させ第1の脱ガス処理を行う。(c)熱処理後、凹部内に充填されるように、絶縁膜上に導電膜を堆積させる。(d)堆積した導電膜を、絶縁膜が露出するまで研磨する。

(もっと読む)

半導体装置およびその製造方法

【課題】FUSIゲート電極に達するコンタクト部と、ソース・ドレイン層に達するコンタクト部とで深さが異なることに起因する不具合を解消した半導体装置およびその製造方法を提供する。

【解決手段】層間絶縁膜4を厚さ方向に貫通して2つのソース・ドレイン層34上層部のシリサイド層35およびFUSIゲート電極32にそれぞれ達する2つのFUSIコンタクト部41が設けられている。FUSIコンタクト部41は、層間絶縁膜4を貫通するコンタクト開口部CH1内に、完全にシリサイド化されたFUSIコンタクト層411を充填して構成されており、FUSIゲート電極32と同じ高さを有している。

(もっと読む)

疎水性多孔質シリカ材料による構造物内部の埋め込み方法

【課題】 トレンチ、ホールを埋め込むための多孔質シリカ材料がエッチングなどのプロセス過程で受けるダメージを減じるようにするトレンチ内部の埋め込み方法の提供。

【解決手段】 50〜5000nmの大きさの開口部を有するトレンチ、ホールからなる構造物を設けてある半導体基板に対して、その構造物の内部に配線を形成した後、疎水性多孔質シリカ材料の前駆体を含有する所定の粘度の溶液を基板上に塗布し、加水分解し、焼成して、配線の形成された構造物内部を疎水性多孔質シリカ材料で埋め込む。

(もっと読む)

半導体装置及びその製造方法

【課題】FUSI電極とポリシリコン抵抗体とを備え、簡便に製造できる半導体装置およびその製造方法を提供する。

【解決手段】FUSIゲート電極とポリシリコン抵抗体とを有するMISトランジスタを備えた半導体装置において、ポリシリコン抵抗体のうちコンタクト形成領域に設けられた部分は、ゲート電極または不純物拡散領域と同時にシリサイド化される。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート配線の幅が狭いフルシリサイド化ゲートプロセスを用いた半導体装置において、ゲート配線の設計ルールを変更することなく、ゲート配線とコンタクトとの接触面積を確保することが容易で且つゲート配線の配線抵抗が小さい半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板10に形成された素子分離領域12及び素子分離領域12に囲まれた活性領域11と、素子分離領域12及び活性領域11の上に形成され、フルシリサイド化されたゲート配線19と、ゲート配線19の側面を連続的に覆う絶縁性のサイドウォール21とを備えている。ゲート配線19の少なくとも一部分は、サイドウォール21から突出して形成されている。

(もっと読む)

ポリマー、膜形成用組成物、絶縁膜およびその製造方法

【課題】新規なポリマー、特に、電子デバイスなどに用いられる誘電率、機械強度等の膜特性が良好な膜形成組成物に用いられるポリマー、さらには膜形成組成物を用いて得られる絶縁膜およびそれを有する電子デバイスを提供する。

【解決手段】エチレン性二重結合またはアセチレン性三重結合を分岐末端にもつデンドリマーとケイ素原子に結合した水素原子を少なくとも2つ以上有する化合物とをヒドロシリル化反応させて得られるポリマー、該ポリマーを含有する膜形成用組成物、該組成物を用いて得られる絶縁膜、及び該絶縁膜を有する電子デバイス。

(もっと読む)

41 - 60 / 74

[ Back to top ]