Fターム[5F033SS08]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | PVD(物理的気相成長法) (621) | スパッタ (435)

Fターム[5F033SS08]の下位に属するFターム

反応性スパッタ (28)

Fターム[5F033SS08]に分類される特許

401 - 407 / 407

有機層の粘着性を改良するための非晶質炭素層を含むデバイス及びその製造方法

フォトレジスト層の粘着性を改良する非晶質炭素層(16)を含む半導体デバイス(10)、及びその半導体デバイスを製造する方法。デバイス(10)は、表面(15)を有する基板(12)と、該基板の表面(15)に設けられた非晶質炭素層(16)と、該基板の表面に設けられた低表面エネルギー材料(14)層とを含む。デバイス(10)は、表面(15)を有する基板(12)を提供するステップと、低表面エネルギー材料層(14)を析出させるステップと、プラズマ化学気相成長(PECVD)やスパッタリングを用いて、基板(12)の表面に低表面エネルギー材料層(14)に接する非晶質炭素層(16)を析出させるステップとから形成される。  (もっと読む)

(もっと読む)

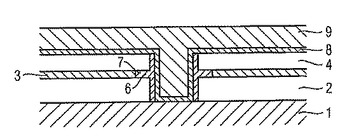

デバイス内にバリア層を有するコンタクトホールを形成する方法及び得られるデバイス

デバイスの下層(2)にコンタクトを形成する方法は、コンタクトホール(5)を形成するステップと、デバイスのコンタクトホール内にバリア材からなるコンタクトホールバリア層(7)を形成するステップと、コンタクトホールの底面のコンタクトホールバリア層をエッチングするステップと、コンタクトホール内にライナ材(8)を堆積するステップと、コンタクトホールに導電性材料(9)を充填するステップとを有する。半導体、受動素子、キャパシタ又はFeRAMなどのデバイスが上記方法に従って形成される。コンタクトホールの側壁にあるコンタクトホールバリア層(7)が、水素及び/又は酸素の側方拡散を抑制する。コンタクトホールバリア層は、ウェットエッチングプロセスによって生じる既存のバリア層(3)内のボイド(6)を充填するために上記プロセス後に、又は既存のバリア層への損傷を抑制するために上記プロセス前に行うことができる。

(もっと読む)

(もっと読む)

集積回路デバイス内の相互接続構造体

【課題】 フォトレジスト汚染の問題に悩まされないデュアル・ダマシン構造体を形成する方法を提供すること。

【解決手段】 本発明は、集積回路デバイス内のデュアル・ダマシン相互接続構造体の製造に関する。具体的には、平坦化材料及び拡散障壁材料を用いて、低kの誘電体薄膜内にシングル又はデュアル・ダマシン構造体を形成するための方法が開示される。この方法の好ましいデュアル・ダマシンの実施形態において、最初に誘電体材料にビアを形成し、次にビア内及び誘電体材料上に平坦化材料を付着させ、平坦化材料上に障壁材料を付着させる。次に、リソグラフィにより像形成材料にトレンチが形成され、障壁材料を通して平坦化材料がエッチングされ、トレンチ・パターンが誘電体材料に転写される。これらのエッチング・ステップの過程の間及び該エッチング・ステップの過程に続いて、像形成材料、障壁材料及び平坦化材料が除去される。次に、結果として得られるデュアル・ダマシン構造を金属化することができる。この方法を用いる場合、層間誘電体材料によるフォトレジスト汚染の問題が軽減される。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体チップ上に絶縁膜を介して外部端子と再配線とが形成される半導体装置において、従来は外部端子、若しくは再配線からのノイズの影響から電子回路を保護する為、接地電位層を設けていたが、この接地電位層の為に工程が大幅に増加し、さらに、半導体装置の厚さが厚くなってしまう可能性があった。

【解決手段】本発明では、基板上の多層配線、即ち、それぞれが層間絶縁膜を介して積層された複数の層と、それぞれの層内に形成された配線とを有する多層配線の最上位の層内において、配線が配置された領域以外の領域に、定電位が与えられるノードに電気的に接続するメタル部材が形成される。これにより、工程を大幅に増加することなく、かつ、半導体装置の厚さを厚くすることなく、電子回路がノイズの影響を受けてしまう可能性を低減することができる。

(もっと読む)

表示装置及びその作製方法

【課題】 配線抵抗による電圧降下の影響や画素への信号の書き込み不良や階調不良などを防止し、より高画質のEL表示装置や液晶表示装置を代表とする表示装置を提供することを課題とする。

【解決手段】 本発明はEL表示装置や液晶表示装置を代表とする表示装置に用いられる電極や配線として、Cuを有する配線を設ける。また、該配線のCuを主成分とする導電膜は、マスクを用いたスパッタ法により形成する。このような構成により、電圧降下や信号のなまりを低減することができる。

(もっと読む)

銅配線構造およびその製造方法

【課題】銅配線の寿命を増大させ、同時に、密着性を高め、ストレスマイグレーション耐性を向上させる。

【解決手段】Cu16とバリアメタル12、あるいはCu16とキャップ層19との界面近傍に、不純物15を固溶させる、不純物15を析出させる、非晶質Cu14を存在させるまたはCuとの化合物を形成することにより、界面近傍の空孔を減らし、Cuのエレクトロマイグレーション(EM)に対する界面拡散の寄与を減少させ、寿命を増大させ、同時に、密着性を高め、ストレスマイグレーション耐性を向上させた。

(もっと読む)

半導体チップ、配線基板およびそれらの製造方法ならびに半導体装置

【課題】複数の半導体チップを配線基板に積層しても、半導体チップを積層した半導体装置の厚みおよび基板面積の増大および半導体チップ間の配線長の増加を招かない半導体チップ、その製造方法および半導体装置等を提供する。

【解決手段】半導体基板13と、半導体基板13の第1の面14に形成された第1の外部電極21と、半導体基板13の第2の面17に形成された第2の外部電極22と、半導体基板13に形成された貫通孔16とを有し、貫通孔16は第2の面17となす内角が鈍角をなして形成された斜面15に設けられ、第1の外部電極21と第2の外部電極22とは、貫通孔16の内壁および斜面15を経由して形成された導電パターン19により電気的に接続されている。

(もっと読む)

401 - 407 / 407

[ Back to top ]