Fターム[5F033SS09]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | PVD(物理的気相成長法) (621) | スパッタ (435) | 反応性スパッタ (28)

Fターム[5F033SS09]に分類される特許

1 - 20 / 28

半導体装置及び半導体装置の作製方法

【課題】微細化されたトランジスタのオン特性を向上させる。微細化されたトランジスタを歩留まりよく作製する。

【解決手段】一対の低抵抗領域及び該低抵抗領域に挟まれるチャネル形成領域を含む酸化物半導体層と、ゲート絶縁層を介してチャネル形成領域と重畳する第1のゲート電極層と、第1のゲート電極層のチャネル長方向の側面及びゲート絶縁層の上面と接し、一対の低抵抗領域と重畳する一対の第2のゲート電極層と、第2のゲート電極層上の、側端部を第2のゲート電極層の側端部と重畳する一対の側壁絶縁層と、を有する半導体装置を提供する。

(もっと読む)

トランジスタアレイ、およびその製造方法

【課題】簡略化された構成を有するトランジスタアレイを、簡易的に製造することが可能なトランジスタアレイの製造方法を提供することを主目的とする。

【解決手段】金属基板を用い、上記金属基板上に、絶縁性材料からなり、貫通孔を有する絶縁層を形成する絶縁層形成工程と、上記絶縁層上に、ドレイン電極が上記絶縁層に形成された貫通孔を介して上記金属基板に接続されるように薄膜トランジスタを形成する、薄膜トランジスタ形成工程と、上記金属基板をパターニングすることにより、上記金属基板を画素電極とする画素電極形成工程と、を有することを特徴とする、トランジスタアレイの製造方法を提供することにより、上記課題を解決する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート配線が保護膜に覆われた構造において、保護膜に発生するクラックがゲート配線に到達することを防止することにより、ゲート−エミッタ間のショート不良を防止する。

【解決手段】半導体素子の第1領域と接続される表面電極17、および通路12の少なくとも一部に、半導体素子の第2領域と接続される第1金属配線18を形成する。その後、はんだ29が実装されない通路12bに形成する第1保護膜25の高さが、はんだ29が実装される通路12aに形成する第1保護膜25の高さよりも高くなるように、注入器32を用いて第1保護膜25を通路12に塗布する。続いて、表面電極17および第1保護膜25の上に金属層27、28を形成してはんだ29が実装されない通路12bに形成した第1保護膜25が金属層27、28から露出するように、はんだ29が実装されない通路12bに形成した第1保護膜25の一部および金属層27、28を切削する。

(もっと読む)

半導体装置及び電子機器

【課題】半導体装置の作製工程におけるプラズマダメージの影響を低減し、しきい値電圧

のばらつきの抑制された均一な表示特性の半導体装置を提供する。

【解決手段】トランジスタ上の平坦化層と、該平坦化層の上面もしくは下面に設けられる

と共に前記平坦化層からの水分や脱ガス成分の拡散を抑制するバリア層を備えた半導体装

置であって、これら平坦化層及びバリア層の位置関係を工夫することにより平坦化層に及

ぶプラズマダメージを低減する上で有効なデバイス構成を用いる。また、画素電極の構造

として新規な構造との組み合わせにより、輝度の向上等の効果をも付与する。

(もっと読む)

薄膜素子用基板の製造方法、薄膜素子の製造方法、薄膜トランジスタの製造方法、薄膜素子、および薄膜トランジスタ

【課題】本発明は、表面平滑性に優れ、薄膜素子の特性劣化を抑制することが可能な薄膜素子用基板が得られる新規な薄膜素子用基板の製造方法を提供することを主目的とする。

【解決手段】本発明は、金属基材に薬液処理を施す金属基材表面処理工程と、上記金属基材上にポリイミド樹脂組成物を塗布して絶縁層を形成する絶縁層形成工程とを有し、上記絶縁層の表面粗さRaが30nm以下であることを特徴とする薄膜素子用基板の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

半導体装置、その製造方法及びその製造方法に用いるスパッタリングターゲット

【課題】 バリア膜形成による配線の抵抗値増大及びボイドの発生を防ぐことができる半導体装置、その製造方法及びその製造方法に用いるスパッタリングターゲットを提供すること。

【解決手段】 Si酸化物を含む絶縁膜1にCuの配線が設けられている半導体装置であって、絶縁膜1に設けられた溝状の開口部1aの内面に形成されたバリア膜4と、開口部1a内であってバリア膜4上に形成されたCuからなる配線本体2と、を備え、バリア膜4が、バリア膜4が、少なくとも絶縁膜1上に形成されたBa酸化物及びSr酸化物の少なくとも一方を含有するCu合金下地層を有し、該Cu合金下地層と絶縁膜1との界面にBaSi酸化物及びSrSi酸化物の少なくとも一方が偏析している。

(もっと読む)

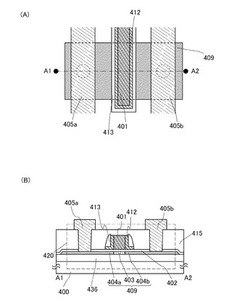

金属−絶縁体相転移材料を用いた機能要素の形成方法及びこれによって形成された機能要素、並びに機能デバイスの製造方法及びこれによって製造された機能デバイス

【課題】金属−絶縁体相転移材料として二酸化バナジウム(VO2)を用いた機能要素の形成方法及びこれによって形成された機能要素、並びに機能デバイスの製造方法及びこれによって製造された機能デバイスを提供すること。

【解決手段】基板40の面に、金属−絶縁体相転移材料10としてVO2薄膜が形成されており、平行な2つの電極15a、15bがVO2薄膜の面に形成されている。両電極を結ぶ複数の機能要素としての金属配線20a〜20eは、レーザ光源30からのレーザ35がVO2薄膜に走査方向37で走査され、レーザ35によって照射されたVO2薄膜の部分が絶縁相から金属相に相転移して金属化されるにことよって形成される。金属配線が形成された領域の少なくとも一部にレーザを照射し、高温(例えば、100℃)とした後、低温(例えば、室温)に冷却して絶縁体化させて、金属配線が形成された領域の少なくとも一部を消去することができる。

(もっと読む)

半導体装置の製造方法

【課題】簡易に、動作中におけるON抵抗の経時変化を低減する半導体装置の製造方法を提供すること。

【解決手段】例えば、第2絶縁膜(層間絶縁膜30)が形成された半導体基板10をアニール炉に入れ600℃以上のアニール処理を施した後、酸素ガスが含まれるガス雰囲気下で前記半導体基板を前記アニール炉から取り出す半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】温度が上昇するほどキャリアの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、素子形成面が(110)面方位の半導体基板上にチャネル長方向が<−110>方向に沿って配置される第1絶縁ゲート型電界効果トランジスタpMOS1と、前記半導体基板上にチャネル長方向が<−110>方向に沿って配置され、前記第1絶縁ゲート型電界効果トランジスタと前記チャネル長方向に隣接する第2絶縁ゲート型電界効果トランジスタnMOS1と、前記第1,第2絶縁ゲート型電界効果トランジスタ上を覆うように設けられ、正の膨張係数を有し、前記第1,第2絶縁ゲート型電界効果トランジスタに、動作熱によりチャネル長方向に沿って圧縮応力を加えピエゾ材料を含む第1ライナー絶縁膜11−1とを具備する。

(もっと読む)

半導体装置

【課題】窒化珪素膜でCu配線を挟み込むことによりCuによりTFTが汚染されるのを防ぐ。

【解決手段】結晶性半導体膜と、結晶性半導体膜上のゲート絶縁膜とゲート絶縁膜上のゲート電極と、結晶性半導体膜及びゲート電極上の第1の層間絶縁膜と、第1の層間絶縁膜に設けられた第1のコンタクト部を介して結晶性半導体膜に電気的に接続される第1の配線と、第1の層間絶縁膜及び第1の配線上の、第1の配線の一部を露出させた第2のコンタクト部が設けられた第1の窒化珪素膜及び第1の窒化珪素膜上の第2の層間絶縁膜と、第2のコンタクト部により露出させた第1の配線上に設けられたCuの拡散を防ぐバリア層と、第2のコンタクト部に設けられたバリア層上のCuでなる第2の配線と、第2の配線を被覆して設けられた第2の窒化珪素膜とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】相変化メモリの記憶層を構成する相変化膜と層間絶縁膜との剥がれを防止すると共に、層間絶縁膜と相変化膜との間に介在する接着層の構成原子が相変化膜内に拡散して相変化膜の特性を変動させる不具合を防止する。

【解決手段】層間絶縁膜20上には抵抗素子RM1、RM2が形成されている。抵抗素子RM1、RM2のそれぞれは、プラグ23(下部電極)と、その上部に積層された接着層24、記憶層25および上部電極26によって構成されている。接着層24は、記憶層25と層間絶縁膜20との界面剥離を防止するために設けられているが、プラグ23(下部電極)の上面には、接着層24が設けられていない。

(もっと読む)

半導体装置の製造装置

【課題】メタルキャップ層の製造工程におけるパーティクルの発生や組成比の変動を抑制させて、半導体装置の信頼性と生産性を向上させた半導体装置の製造装置に関するものである。

【解決手段】成膜チャンバ33は、第1カソード40aと第2カソード40bを備え、各カソード40a,40bに、それぞれZrを含む第1ターゲット42aと、BNを主成分とする第2ターゲット42bを搭載する。そして、成膜チャンバ33は、各外部電源を駆動して第1ターゲット42aと第2ターゲット42bとを同時にスパッタし、第1絶縁層の表面と第1配線の表面、又は、第2絶縁層の表面と第2配線の表面に、ZrBNを主成分とするメタルキャップ層を成膜させる。

(もっと読む)

マグネトロンスパッタリング装置および半導体装置の製造方法

【課題】ウェーハ外周部のスルーホールやトレンチ内における被覆性を向上できるマグネトロンスパッタ装置および半導体装置の製造方法を提供する。

【解決手段】サセプタ3に接続された高周波電源8と、スパッタ室2の外側であって、ターゲットの中心軸C1と同軸のプレート9と、中心軸を中心Cにプレートを回転させる回転移動手段と、プレートの一面においてS極端をターゲットに向けたS極マグネット10Sと、プレートの一面においてN極端をターゲットに向けた第1及び第2のN極マグネット10Nと、を備え、第1のN極マグネットと第2のN極マグネットとの磁束密度がS極マグネットの磁束密度より大きい。

(もっと読む)

回路素子用の保護膜及び該保護膜の作製方法

本開示の一の実施例によると、回路素子用の保護膜を作製する方法は概して、基板表面を有する基板を供する工程、前記基板表面上に電気部品を作製する工程、並びに、前記基板表面及び電気部品を第1保護誘電膜でコーティングする工程を有する。前記第1保護誘電膜は概して、透湿性が0.01g/m2/日、吸湿率が0.04%未満、誘電率が10未満、誘電損失が0.005未満、絶縁破壊電圧強度が8×106V/cmよりも大きく、シート抵抗が1015Ω-cmで、かつ欠陥密度が0.5/cm2未満である、水蒸気に溶けない材料で作られる。  (もっと読む)

(もっと読む)

基板貫通相互接続を形成する方法

少なくとも1つの基板貫通相互接続を形成する方法の一実施形態において、第1の表面202、及び反対側の第2の表面204を有する半導体基板200を提供する。半導体基板に、少なくとも1つの開口210を、半導体基板内で第1の面から中間深さまで延在するように形成する。少なくとも1つの開口は、基部216によって部分的に画定される。基部上に、少なくとも1つの金属触媒ナノ粒子220を提供する。金属触媒ナノ粒子によって導電性材料222の堆積が促進される条件下で、少なくとも1つの開口内に導電性材料を堆積させる。半導体基板の材料を第2の面から除去することにより、少なくとも1つの開口を充填する導電性材料の一部を露出させることができる(図3K)。別の実施形態では、ナノ粒子を使用する代りに、導電性材料を、少なくとも1つの開口を部分的に画定する基部に選択的に堆積するように選択することができる。  (もっと読む)

(もっと読む)

電子装置およびその製造方法

【課題】ヒステリシスを有するMIM素子を配列した電子装置を、高い歩留まりで製造可能とする。

【解決手段】電子装置は、基板と、前記基板上に互いに平行に第1の方向に延在するように形成されたダミーパターンと、前記ダミーパターンの相対向する第1および第2の側壁面にそれぞれ形成された第1および第2の導電性側壁膜よりなり、各々前記第1の方向に延在する一対の下部電極パターンと、前記基板上に、前記ダミーパターンおよび前記一対の下部電極パターンを覆って形成された、金属酸化物よりなるヒステリシス膜と、前記ヒステリシス膜上に、前記第1の方向とは異なる第2の方向に延在するように形成された導電膜よりなる上部電極パターンと、よりなる。

(もっと読む)

半導体装置の製造方法

【課題】TiNを含む金属膜上におけるレジスト除去速度の低下を抑え、レジスト残りが発生することがない安定したレジスト除去を実現できるようにする。

【解決手段】半導体装置の製造方法は、基板10の上に窒化チタンを含む金属膜12を形成する工程(a)と、金属膜12の上に酸化膜13を形成する工程(b)と、酸化膜13の上にレジストパターン14を形成する工程(c)と、レジストパターン14をマスクとして金属膜13を選択的にエッチングする工程(d)と、工程(d)よりも後に、レジストパターン14を酸素プラズマにより除去する工程(e)とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】導体材料がキャパシタ電極材料に到達するのを抑制可能な半導体装置及びその製造方法を提供すること。

【解決手段】本発明の第1の態様に係る半導体装置は、半導体基板と;前記半導体基板上に形成される下部電極と、前記下部電極上に形成される容量絶縁膜と、前記容量絶縁膜上に形成される上部電極より構成されるキャパシタと;前記上部電極及び下部電極上に形成されるコンタクトホールと;前記コンタクトホール内に形成される、酸素を含有したバリア層と;内面に前記バリア層が形成された前記コンタクトホールに充填される導体層とを備える。

(もっと読む)

半導体装置の製造方法

【課題】アルミ又はアルミ合金等からなる配線層の熱応力に基づく問題を回避可能な方法を提供すること。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板上に配線層を形成する工程と;前記配線層をパターニングする工程と;前記配線層を保護絶縁膜で覆う工程とを含む。そして、前記配線層を形成する工程の後であって、前記配線層を前記保護絶縁膜で覆う工程の前に行われる必要な全ての熱処理工程を、前記配線層の塑性変形温度以下で行う。

(もっと読む)

半導体装置およびその製造方法

【課題】 基板のエッジから膜剥がれが発生しても、膜剥がれの進行を止めることが可能な構造を持つ半導体装置を提供する。

【解決手段】 有効チップ100を含む半導体基板101上に形成された層間絶縁膜102と、層間絶縁膜102の有効チップ100上に形成された配線パターン103と、層間絶縁膜102の有効チップ100上と半導体基板101のエッジ104上との間に形成され、層間絶縁膜102を、有効チップ100を含む内周部分(Inside)と有効チップ100を含まない外周部分(Outside)とに分離する少なくとも一本の溝パターン105と、溝パターン105内、及び配線パターン103内に形成された配線材106とを具備する。

(もっと読む)

1 - 20 / 28

[ Back to top ]