Fターム[5F033SS08]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | PVD(物理的気相成長法) (621) | スパッタ (435)

Fターム[5F033SS08]の下位に属するFターム

反応性スパッタ (28)

Fターム[5F033SS08]に分類される特許

201 - 220 / 407

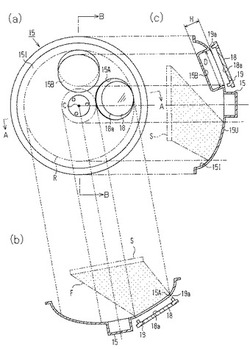

成膜装置及び成膜方法

【課題】予備スパッタの安定化を図ることにより膜質や膜厚制御性を向上させた成膜装置及び成膜方法を提供する。

【解決手段】シャッタ板15は、回動経路Rに設けられてターゲット18とシャッタ板15との間にターゲット18を遮蔽するための遮蔽面15Uを有し、また、回動経路Rに設けられてターゲット18とシャッタ板15との間に基板S側に向かって凹設された凹部15Bとを有する。そして、シャッタ板15は、ターゲット18のプレスパッタを実行するとき、その凹部15Bとターゲット18とを対向させ、ターゲット18の本スパッタを実行するとき、その開口15Aとターゲット18とを対向させる。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体キャパシタの特性ばらつきを低減する。

【解決手段】本発明の製造方法は、基体上に第1電極32と強誘電体膜33と第2電極34とが順次積層された強誘電体キャパシタ3を形成する工程と、強誘電体キャパシタ3及び前記基体を覆って第1層間絶縁膜5を形成する工程と、第1層間絶縁膜5を覆って第2層間絶縁膜6の材料膜61を形成する工程と、材料膜61の上面側をCMP法で研磨することにより、強誘電体キャパシタ3上に位置する第1層間絶縁膜5を露出させる工程と、第1層間絶縁膜5を露出させる工程の後に、第1層間絶縁膜5を貫通して第2電極34を露出させるコンタクトホール70を形成する工程と、コンタクトホール70内に、第2電極34と導通するプラグ導電部を形成する工程と、を有する。第1層間絶縁膜5は、第2層間絶縁膜6と比して、CMP法による研磨速度が遅くなるようにする。

(もっと読む)

貫通配線付基板の製造方法

【課題】貫通配線16a〜16cが基板18から剥離することを抑制し、且つ貫通孔44の内壁面に均一な膜厚の絶縁膜を膜厚制御性良く形成する。

【解決手段】シリコンからなる基板18の表裏面を貫通孔44が貫通し、貫通孔44の内部に熱酸化膜45を介して配線金属47からなる貫通配線16が充填され、基板18の表面に緩衝膜17が積層され、貫通配線16は緩衝膜17を貫通して緩衝膜17上に延長されている貫通配線付基板を製造する方法であって、基板18をエッチングして貫通孔44を形成する第1の工程と、基板18を加熱することにより第1の工程で形成された貫通孔44の内壁に熱酸化膜45を成膜する第2の工程と、第2の工程の後に基板18の表面に緩衝膜材料48を塗布及び熱硬化させて緩衝膜17を形成する第3の工程と、第3の工程の後に貫通孔44の内部に配線金属47を充填して貫通配線16a〜16cを形成する第4の工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】本発明の課題は、電極や配線の周囲に空間部を形成するに際し、電極材料や配線材料が耐フッ酸性がない材料であっても適用でき、かつ有機汚染の心配のない半導体装置の製造方法を提供することである。

【解決手段】本発明の半導体装置の製造方法は、ゲート電極21aの周囲を昇華性を有する材料としての塩化アルミニウム膜22aからなる犠牲膜で被覆し、その犠牲膜の周囲を外殻層としてのSiN膜23で被覆し、外殻層に設けた開口部24を通して犠牲膜をその昇華温度以上に加熱し除去して、ゲート電極21aの周囲に空間部25を形成する。

(もっと読む)

表示装置の作製方法

【課題】電気特性に優れ、信頼性の高い薄膜トランジスタを有する表示装置を生産性よく作製する方法を提案することを課題とする。

【解決手段】ゲート電極上にゲート絶縁膜を形成し、ゲート絶縁膜上に微結晶半導体膜を成膜し、微結晶半導体膜の表面からレーザビームを照射して微結晶半導体膜の結晶性を改善する。次に、結晶性が改善された微結晶半導体膜を用いて薄膜トランジスタを形成する。また当該薄膜トランジスタを有する表示装置を作製する。

(もっと読む)

半導体装置の製造方法及び記憶媒体

【課題】基板上に形成された有機膜をエッチングするにあたり、良好なエッチング形状を得ること。

【解決手段】シリコン含有膜をプラズマによりエッチングして当該膜上のパターンマスクのパターンを転写する工程と、前記パターンマスクを除去して前記シリコン含有膜の表面を露出させる工程と、プラズマ中の酸素の活性種により前記シリコン含有膜のパターンを介して前記有機膜の表面をエッチングし、凹部を形成する工程と、その後、前記シリコン含有膜をスパッタして前記凹部の内壁面にシリコン含有物からなる保護膜を形成する工程と、凹部を、プラズマ中の酸素の活性種により前記シリコン含有膜のパターンを介して更に深さ方向にエッチングする工程と、を行うことで、凹部の側壁を酸素の活性種から保護しながらエッチングを行うことができるため良好なパターン形状が得られる。

(もっと読む)

半導体集積回路装置、半導体集積回路装置用パターンの生成方法、半導体集積回路装置の製造方法、および半導体集積回路装置用パターン生成装置

【課題】有効に電源ノイズの吸収をはかり、回路の安定動作を実現することを目的とする。特にノイズ発生源のすぐ近くでノイズの吸収を行う。

【解決手段】少なくとも一つの回路ブロックを備えた半導体集積回路装置であって、前記回路ブロック上に第1の導体層1aと、前記第1の導体層1a上に容量絶縁膜1cを介して形成された第2の導体層1bとを具備してなるバイパスコンデンサを具備し、前記バイパスコンデンサの前記第1及び第2の導体層の一方は基板電位を固定する基板コンタクトを介してグランド配線または電源配線の一方に接続され、他方は電源配線またはグランド配線の残る一方に接続される。

(もっと読む)

スパッタリング装置

【課題】傾斜したマルチカソードの各々でスパッタされた中性原子を用いることでウェハー表面のパターン化された孔または溝でより良い側壁および底部のカバレッジを形成できるスパッタリング装置を提供する。

【解決手段】ウェハーホルダ12に対して傾斜した複数のカソード11を有し、該カソード11に該カソード11の中央軸とずれた軸で回転する複数のマグネット18を設け、反応容器内を5Paより高い圧力に制御し、プラズマがカソード11に印加されたrf電力の容量的結合によって生成されるとき、選択されたカソード11の上に負の自己バイアス電圧を生成し、前記カソード11から放出されたスパッタ原子をイオン化し、前記負バイアス電位により加速するように為したスパッタリング装置。

(もっと読む)

半導体装置及びその作製方法

【課題】接続孔内から無電解めっき層が剥がれて抜け落ちるのを防止できる半導体装置及びその作製方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体層32上に形成された第1の絶縁層33,203と、前記第1の絶縁層に形成され、前記第1の絶縁層の上面から途中まで異方性エッチングにより形成された第1の接続孔203cと、前記第1の絶縁層に形成され、前記第1の接続孔に繋げられ、前記第1の接続孔下の前記第1の絶縁層が等方性エッチングにより形成され、前記半導体層上に位置する第2の接続孔203gと、前記第1の接続孔内の側面及び前記第1の絶縁層上に形成された第2の絶縁層203dと、前記第2の接続孔の底面の前記半導体層から成長され、前記第2の接続孔内及び前記第1の接続孔内に埋め込まれた無電解めっき層204aと、を具備することを特徴とする。

(もっと読む)

スパッタリング方法

【課題】傾斜したマルチカソードの各々でスパッタされた中性原子を用いることでウェハー表面のパターン化された孔または溝でより良い側壁および底部のカバレッジを形成する。

【解決手段】5Paより高い圧力下において、ウェハー基板24を回転させながら、High−k誘電体材料を有するターゲットおよびカソード11を傾斜させて配置し、該カソード11と下部電極15にそれぞれrf電流を印加し、下部電極15にプラズマ電位に対して負のバイアス電位を印加してスパッタリングを行う。

(もっと読む)

固定用構造および嵌合構造

【課題】半導体デバイスの温度サイクル(TC)信頼性試験において、金属線がチップ表面からリフトオフされてチップが剥がれてしまわない固定用構造及び嵌合構造を提供する。

【解決手段】半導体デバイスの金属構造210のための固定用構造は、オーバーハング形状の側壁230を少なくとも1つ含んだ固定用凹部構造220を含んでいる。上記金属構造210は、少なくとも部分的に上記固定用凹部構造220内に配置されている。

(もっと読む)

カーボンナノチューブベースの電気的接続の製造方法

【課題】デュアルダマシン構造にも適用出来る好ましくはカーボンで作られるナノチューブによるビアの形成法を提供する。

【解決手段】底部と、側壁とを備える、少なくとも1つのビアを、金属材料の2つの層4及び12を隔てる絶縁材料層5の中に形成する。次いで接着層7及び/又は保護層8の上に触媒層9を堆積する。さらに抑止層11を、前記ビアの前記底部における前記触媒層9の部分を除く、前記ビアの前記ビアの側壁の上と、前記絶縁材料層5の上に方向性堆積によって形成する。ナノチューブを前記抑止層11のない前記ビア底部の前記触媒層9の部分から成長させて前記金属材料の2つの層4及び12を電気的に接続する。

(もっと読む)

半導体装置

【課題】金属面上に配置した場合でも磁束のトラップが少ない半導体装置を提供する。

【解決手段】半導体基板11の一方の面上の第1の絶縁層13上に複数本が略平行に並設された第1の金属配線19と、他方の面上の第2の絶縁層14上に複数本が略平行に並設された第2の金属配線18と、第2の金属配線18の一端18a側で半導体基板11を貫通した複数個の第1の貫通配線17aと、第2の金属配線18の他端18b側で半導体基板11を貫通した複数個の第2の貫通配線17bとを備え、第1の金属配線19の一端19aと第2の金属配線18の一端18aが第1の貫通配線17aを介して接続され、第1の金属配線19の他端19bと第2の金属配線18の他端18bが第2の貫通配線17bを介して接続され、配線17a,17b,18,19からなる配線結線が半導体基板11の平面方向と垂直な向きに中心軸線を有するソレノイドアンテナ20を構成している。

(もっと読む)

半導体装置の作製方法

【課題】材料や形成されたパターンが異なる複数の層が積層された構造の半導体装置において、CMP法による研磨処理やSOG膜成膜による平坦化処理を行わなくても平坦化でき、さらに基板材料を選ばず、簡便に平坦化を行う方法を提供することを課題とする

【解決手段】異なる層が複数積層されて形成された半導体装置において、絶縁膜に開口部を形成し、その開口部内に配線(電極)または半導体層を形成することにより、絶縁膜および配線(電極)または半導体層上に形成される絶縁膜に対してCMP法による研磨処理またはSOG膜の成膜による平坦化を行わなくても表面の平坦化を行うことができる。

(もっと読む)

半導体装置

【課題】上層配線と下層配線との間の絶縁耐圧を一定以上に維持しつつ、層間絶縁膜の膜厚を小さくすることができる、半導体装置を提供する。

【解決手段】下層配線としてのソース配線10上には、第2層間絶縁膜および第3層間絶縁膜が積層されている。第3層間絶縁膜上には、上層配線としてのドレイン配線15が形成されている。このドレイン配線15は、平面視でソース配線10と交差する。また、ソース配線10とドレイン配線15との間には、平面視でソース配線10とドレイン配線15とが交差する部分を含む領域24に、各層間絶縁膜の材料よりも高い絶縁性を有する材料からなる高絶縁体17が備えられている。

(もっと読む)

コンタクトスペーサを備えるコンタクト構造体の形成方法及びそれを用いた半導体素子の製造方法

【課題】コンタクトスペーサを備えるコンタクト構造体の形成方法及びそれを用いた半導体素子の製造方法を提供する。

【解決手段】本発明のコンタクト構造体の形成方法は、半導体基板上に層間絶縁膜を形成する工程と、層間絶縁膜をパターニングして半導体基板の所定領域を露出させるコンタクトホールを形成する工程と、半導体基板の主表面に対して傾斜した蒸着方向を有する蒸着法を用いてコンタクトホールの側壁にコンタクトスペーサを形成する工程と、を有する。このとき、蒸着方向は主表面と主表面に対する法線との間に位置する。それと共に、このコンタクト構造体の形成方法を用いた半導体素子の製造方法も提供される。

(もっと読む)

自己集合ナノ構造をパターン化する方法及び多孔性誘電体層を形成する方法(自己集合ナノ構造をパターン化しそして多孔性誘電体を形成する方法)

【課題】 自己集合ナノ構造をパターン化しそして多孔性誘電体層を形成する方法を提供する。

【解決手段】 自己集合ナノ構造をパターン化しそして多孔性誘電体を形成する方法は、1つの態様において、下側層を覆ってハードマスク層を設けるステップと、パターン化の間に保護されるべきハードマスク層の領域をフォトレジスト層により予め画定するステップと、ハードマスク層及びフォトレジスト層を覆って共重合体層を形成するステップと、共重合体層から自己集合ナノ構造を形成するステップと、自己集合ナノ構造をパターン化するためにエッチングするステップとを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置の製造方法及び表示装置

【課題】段差部における配線の被覆性の向上と、微細な配線の形成と、配線間における寄生容量の増加の抑制とが可能である半導体装置の製造方法を提供する。

【解決手段】基板の一方の主面側に、接続孔が形成された絶縁膜と上記絶縁膜上に形成された配線とを備える半導体装置の製造方法であって、上記製造方法は、液状導電性材料を用いて少なくとも接続孔内に導電部を形成する工程(導電部形成工程)と、ウェットエッチングにより接続孔内以外に形成された導電部を除去する工程(導電部除去工程)とを含む半導体装置の製造方法である。

(もっと読む)

絶縁膜及びその製造方法、並びに絶縁膜を備えた電子デバイス

【課題】 他の部分にダメージを与えることなく優れた絶縁性が得られる絶縁膜及びその製造方法、並びに絶縁膜を備えた電子デバイスを提供する。

【解決手段】 基板1上に、蒸着法により、Al、Hf、Zr及びSiからなる群から選択された少なくとも1種の元素を含む酸化物又は窒化物からなる蒸着絶縁膜2を形成する。そして、この蒸着絶縁膜2に対して、基板1の温度を300乃至500℃にして、水素プラズマ処理及び酸素プラズマ処理からなる群から選択された少なくとも1種の処理を施す。

(もっと読む)

201 - 220 / 407

[ Back to top ]