Fターム[5F033SS08]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | PVD(物理的気相成長法) (621) | スパッタ (435)

Fターム[5F033SS08]の下位に属するFターム

反応性スパッタ (28)

Fターム[5F033SS08]に分類される特許

141 - 160 / 407

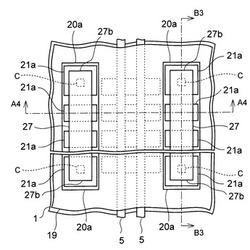

半導体装置とその製造方法

【課題】キャパシタを備えた半導体装置とその製造方法において、キャパシタの品質を向上させること。

【解決手段】第1の導電膜19、誘電体膜20、及び第2の導電膜21をこの順に形成する工程と、第2の導電膜21をパターニングして、複数の上部電極21aを形成する工程と、レジストパターン27の側面27bが後退するエッチング条件を用いて、該レジストパターン27をマスクにしながら誘電体膜20をエッチングし、キャパシタ誘電体膜20aを形成する工程と、第1の導電膜19をパターニングして下部電極19aを形成する工程と、上部電極19aの上の層間絶縁膜33にホール33aを形成する工程と、ホール33aに導体プラグ37を埋め込む工程とを有し、端部の上部電極21a上のホール37の形成予定領域が、側面27bが後退した後のレジストパターン27により覆われる半導体装置の製造方法による。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備えた保護回路等が必要となる。

【解決手段】ゲート電極15を被覆するゲート絶縁層37と、ゲート絶縁層37上においてゲート電極15と端部が重畳し、第2酸化物半導体層40と導電層41が積層された一対の第1配線層38及び第2配線層39と、少なくともゲート電極15と重畳しゲート絶縁層37及び該第1配線層38及び該第2配線層39における導電層41の側面部及び上面部の一部と第2酸化物半導体層40の側面部と接する第1酸化物半導体層36とを有する非線形素子30aを用いて保護回路を構成する。

ゲート絶縁層37上において物性の異なる酸化物半導体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可能となり、接合リークが低減し、非線形素子30aの特性を向上させることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ダマシン法による配線パターン形成の際、低誘電率膜を層間絶縁膜に使った場合においてもビアホールや配線溝の側壁面における損傷や変形の発生を抑制し、同時に、下側配線パターンと上側配線パターンとのコンタクト抵抗を低減する半導体装置の提供。

【解決手段】活性素子を有する基板と、前記基板上において前記活性素子を覆う第1の層間絶縁膜と、前記第1の層間絶縁膜中に埋設された第1の配線層43Cuと、前記第1の層間絶縁膜上に形成された第2の層間絶縁膜52と、前記第2の層間絶縁膜中に埋設された第2の配線層と、を備え、前記第2の配線層は配線パターンと、前記配線パターンから延在し前記第1の配線層を構成する導体パターンの表面と直接に接触するビアプラグ50Vとを有し、前記配線パターンの底面および側壁面、および前記ビアプラグの側壁面は拡散バリア膜49A,49Bにより覆われることを特徴とする半導体装置。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、強誘電体膜を備えたキャパシタの劣化を防止すること。

【解決手段】シリコン基板30の上方に、下部電極61と、強誘電体膜よりなるキャパシタ誘電体膜62と、上部電極63とを有するキャパシタQを形成する工程と、キャパシタQ上に第1の保護膜70を形成する工程と、第1の保護膜70に、上部電極63に達する第1の開口70aを形成する工程と、第1の開口70aを形成した後に、第1の保護膜70及び第1の開口70aから露出する上部電極63の上方に層間絶縁膜71を形成する工程と、層間絶縁膜71に、第1の開口70aの内側で上部電極63に達する第1のホール71aを形成する工程と、第1のホール71aに第1の導体プラグ77aを埋め込む工程とを含む半導体装置の製造方法による。

(もっと読む)

半導体装置およびその製造方法

【課題】電極上に膜(水素バリア膜、バリアメタル)が形成される場合に、電極上での膜のカバレッジ不良の発生を防止することができる、半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1では、強誘電体膜13上に、強誘電体膜13に接する電極下層15とこの電極下層15上に積層される電極上層16との積層構造を有する上部電極14が積層されている。そして、電極上層16の上面は、平坦化により、強誘電体膜13の表面モホロジーと無関係な平坦面となっている。したがって、電極上層16上で水素バリア膜17およびバリアメタル28をほぼ均一な厚さに形成することができ、上部電極14上での膜のカバレッジ不良の発生を防止することができる。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、強誘電体膜を備えたキャパシタの劣化を防止すること。

【解決手段】シリコン基板30の上方に、下部電極61、強誘電体膜よりなるキャパシタ誘電体膜62と、上部電極63とを有するキャパシタQを形成する工程と、キャパシタQ上に層間絶縁膜71を形成する工程と、層間絶縁膜71に、上部電極63に達するホール59aを形成する工程と、ホール59aの内面、及びホール59aから露出する上部電極63の表面に第1のバリア膜67を形成する工程と、第1のバリア膜67上に、第1のバリア膜67よりも酸素濃度が高い第2のバリア膜68を形成する工程と、第2のバリア膜68の上方に導電膜74を形成して、ホール59aを埋め込む工程とを含む半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法及び成膜システム

【課題】フッ素添加カーボン膜(CF膜)上にハードマスク用の薄膜であるSiCO膜あるいはSiCN膜を成膜するにあたり、その薄膜とフッ素添加カーボン膜との間で大きな密着性を得ること。

【解決手段】 SiCO膜をハードマスクとして使用する場合に、CF膜をシリコンの有機化合物例えばトリメチルシランガスを活性化したプラズマ雰囲気に例えば5〜10秒程度曝し、次いでこのプラズマに窒素プラズマを加えてフッ素添加カーボン膜の上にSiCN膜を成膜し、その後例えばトリメチルシランガスと酸素ガスとを活性化したプラズマによりSiCO膜を成膜する。SiCO膜の成膜時に、酸素の活性種がCF膜中の炭素と反応することが抑えられ、従ってCF膜の脱ガス量が低減する。またSiCN膜をハードマスクとして使用する場合も、同様に最初にトリメチルシランガスのプラズマ処理を行う。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を効率良く製造できるようにする。

【解決手段】シリコン基板1上に強誘電体キャパシタ37を形成する際、下部電極膜25の上に、アモルファス又は微結晶の酸化導電膜26を形成する。酸化導電膜26を熱処理により結晶化した後、強誘電体膜27の初期層27Aの形成時に酸化導電膜26を還元することにより、結晶粒が小さく且つ配向が整った第2の導電膜26Aを形成する。強誘電体膜27は、MOCVD法により形成し、その初期層27Aは第2の導電膜26Aの結晶配向に倣って成長する。これにより、強誘電体膜27の表面モフォロジが良好になる。

(もっと読む)

薄膜トランジスタ基板とその製造方法

【課題】工程効率が向上し、かつ、信頼性が向上した酸化物半導体薄膜トランジスタ基板とその製造方法を提供する。

【解決手段】酸化物半導体薄膜トランジスタは、絶縁基板上に形成され、ゲート電極を含むゲート線と、ゲート線と交差しドレイン電極接続部を含むデータ線と、ゲート電極の周辺に形成される酸化物半導体活性層パターンと、データ線と酸化物半導体活性層パターンの上に形成されドレイン電極接続部を露出する第1開口部、及び酸化物半導体活性層パターンを露出する第2開口部を有するパシベーション層と、第1開口部及び第2開口部によって酸化物半導体活性層パターンとドレイン電極接続部とを電気的に接続するドレイン電極とを含む。

(もっと読む)

有機薄膜トランジスタ、有機薄膜トランジスタの製造方法、および電子機器

【課題】有機材料からなる下地の絶縁性層に対してダメージを与えることなく、かつ上部に設けられる有機半導体層に対して良好なオーミックコンタクトが得られるソース電極およびドレイン電極を低コストで得ることを可能にする。

【解決手段】有機絶縁層からなる基板11と、基板11上にめっき成膜された層からなるソース電極13sおよびドレイン電極13dの第1層13-1と、第1層13-1よりも有機半導体材料に対して低オーミック接合を形成する金属材料からなり第1層13-1を覆う状態でめっき成膜されたソース電極13sおよびドレイン電極13dの第2層13-2と、第1層13-1および第2層13-2で構成されたソース電極13sおよびドレイン電極13d間にわたって設けられた有機半導体層15とを備えた有機薄膜トランジスタ1aである。

(もっと読む)

アクティブマトリクス基板、ディスプレイパネル、表示装置およびアクティブマトリクス基板の製造方法

【課題】アクティブマトリクス基板の開口率と消費電力とを向上させる。

【解決手段】アクティブマトリクス基板101Aは、透明基板10と、透明基板10上に形成された配線(LG,LD,LP,L1,L2等)と、この配線(LG,LD,LP,L1,L2等)の少なくとも一部を覆う透明半導体層44と、配線(LG,LD,LP,L1,L2等)および透明半導体層44の少なくとも一部を覆う透明な絶縁膜と、を備える。配線(LG,LD,LP,L1,L2等)は、主配線としての第1メタル配線41Mと、これから分岐する副配線としての透明な配線(41,42,43等)と、を含む。主配線としての第1メタル配線41Mは、少なくとも一部が副配線としての配線(41,42,43等)よりも高い導電性を備えた材料を用いて形成される。

(もっと読む)

電子デバイス及びその製造方法

【課題】層間絶縁膜に形成した空隙部を導電材料で充填して配線・接続部を形成する際に問題となる、下層の導電領域と配線・接続部との接続状態に起因する不都合を生ぜしめることなく、微細な配線及び接続部が所望の状態に正確且つ容易に実現されてなる信頼性の高い電子デバイスを実現する。

【解決手段】ダミー構造物16を形成し、ダミー構造物16の側面のみに側壁膜17を形成する。このダミー構造物16を覆うように層間絶縁膜18を形成する。そして、側壁膜17が残るようにダミー構造物16のみを除去し、下層配線14の表面の一部を露出させ、層間絶縁膜18に形成された開口18aをCuで埋め込み、Cuの表層を層間絶縁膜18の表面に合わせて平坦化する。以上により、下層配線14と直接的に接続されるCu接続部22を形成する。

(もっと読む)

カーボンナノチューブベースの水平相互接続アーキテクチャ

【課題】本発明は、少なくとも二つのボンディングパッド間に水平方向の電気接続を確立することを可能にする装置に関する。

【解決手段】本装置はボンディングパッドの垂直壁を接続する水平なカーボンナノチューブを備え、ボンディングパッドは少なくとも二つの物質を積層させることによって形成されていて、その一つはナノチューブ成長に触媒作用をもたらし、他の一つはナノチューブ成長に触媒作用をもたらす物質の層間のスペーサとして機能する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】基板に発生する応力を低減できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体素子が形成される素子領域を有する基板と、素子領域の隣接部分の基板に形成されるビアホールと、ビアホール内に絶縁層を介して設けられる導通部と、基板と絶縁層との間に設けられる緩衝層とを備え、緩衝層は、基板の熱膨張係数と緩衝層の熱膨張係数との差が、基板の熱膨張係数と絶縁層の熱膨張係数との差より小さい材料から形成される。

(もっと読む)

半導体装置

【課題】ソース/ドレイン領域へのコンタクトの方法を改良することにより、配線抵抗を減らす。

【解決手段】基板上の酸化珪素膜と、酸化珪素膜上のソース領域、ドレイン領域、ソース領域の上部に形成された第1のシリサイド、ドレイン領域の上部に形成された第2のシリサイド、及びチャネル形成領域を有する半導体層と、ゲイト絶縁膜と、多結晶珪素膜及び第3のシリサイドを有するゲイト電極と、ゲイト電極の側面に設けられた側壁と、第1のシリサイドに密着して形成された第1の金属配線と、第2のシリサイドに密着して形成された第2の金属配線と、を有し、第1の金属配線と第2の金属配線は同一金属膜をエッチングして形成された構造であり、第1乃至第3のシリサイドは、金属膜に用いられる金属を用いて形成されたシリサイドである。

(もっと読む)

銅めっきされた高アスペクト比のビア、及びその製造する方法

【課題】 最新のスケーリング技術の要件に適応することができ、適切に機能する実行可能なビアを一貫して生成できる、改善されたビア製造プロセスを提供すること。

【解決手段】 改善された高アスペクト比ビア及びそれを形成するための技術が提供される。1つの態様において、銅めっきされた高アスペクト比ビアを製造する方法が提供される。この方法は、以下のステップを含む。誘電体層内に高アスペクト比ビアをエッチングする。高アスペクト比ビア内及び誘電体層の1つ又は複数の表面の上に、拡散バリア領域を堆積させる。拡散バリア層の上に銅層を堆積させる。銅層の上にルテニウム層を堆積させる。高アスペクト比ビアを、ルテニウム層の上にめっきされた銅で充填する。この方法によって形成される銅めっきされた高アスペクト比ビアも提供される。

(もっと読む)

半導体装置及び回路基板

【課題】小型の半導体装置においても静電容量の大きなキャパシタを配置することが可能な構造を有する半導体装置を提供する。

【解決手段】半導体装置1は、半導体素子8が形成された半導体基板2と、半導体基板2のパッシベーション膜12を介して配置され1方向に長く形成された開口部4aを有する平面型のスロットアンテナ4と、スロットアンテナ4と並列接続する共振用キャパシタ15とを備え、共振用キャパシタ15はチップ型素子となっている。

(もっと読む)

半導体装置およびその作製方法

【課題】開口率の高い半導体装置又はその製造方法を提供する。また、消費電力の低い半導体装置又はその製造方法を提供する。

【解決手段】ゲート電極として機能する透光性を有する導電層と、該透光性を有する導電層上に形成されるゲート絶縁膜と、ゲート電極として機能する透光性を有する導電層上にゲート絶縁膜を介して半導体層と、半導体層に電気的に接続されたソース電極又はドレイン電極として機能する透光性を有する導電層とで構成されている。

(もっと読む)

強誘電体メモリ装置の製造方法

【課題】コンタクトプラグ上に直接形成される下地層の結晶配向性を良好にし、さらにこの下地層の平坦性をも良好にすることで、下部電極や強誘電体膜の結晶配向性の改善を図った強誘電体メモリ装置の製造方法を提供する。

【解決手段】基板の上方に導電性の下地層を形成する工程と、下地層の上方に第1電極と強誘電体膜と第2電極とを積層する工程と、を含む強誘電体メモリ装置の製造方法である。下地層の形成工程は、プラグ20を含む層間絶縁膜26上に、自己配向性を有する導電材料からなる導電層411を形成する工程と、導電層411を窒素雰囲気中で熱処理し、窒化導電層412とする工程と、窒化導電層412を、シリコン酸化膜研磨用のスラリーを用いたCMP法によって低研磨速度で平坦化処理し、プラグ20を含む層間絶縁膜26上を覆った状態の平坦化窒化チタン層41とする工程と、を含む。

(もっと読む)

パターン形成キャップを用いるエアギャップ形成と一体化

【課題】 膜をパターン形成する方法及びこれらの得られた構造を提供する。

【解決手段】 実施形態において、基板、例えば、ダマシン層の上にアモルファス炭素マスクを形成する。アモルファス炭素マスクの上にスペーサ層を堆積させ、スペーサ層をエッチングして、スペーサを形成するとともにアモルファス炭素マスクをさらす。アモルファス炭素マスクを選択的にスペーサまで除去して、基板層をさらす。ギャップ充填層がスペーサの周りに堆積されて、基板層を覆うがスペーサをさらす。スペーサを除去して、選択的に基板の上にギャップ充填マスクを形成する。ギャップ充填マスクのパターンは、一実施態様においては、ダマシン層に転写されて、IMDの少なくとも一部を除去するとともにエアギャップを形成する。

(もっと読む)

141 - 160 / 407

[ Back to top ]