Fターム[5F033SS08]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | PVD(物理的気相成長法) (621) | スパッタ (435)

Fターム[5F033SS08]の下位に属するFターム

反応性スパッタ (28)

Fターム[5F033SS08]に分類される特許

61 - 80 / 407

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】記憶素子の下にあるコンタクトプラグの上面の平坦性を改善し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、半導体基板上に設けられた複数のスイッチングトランジスタと、隣接する2つのスイッチングトランジスタ間に埋め込まれ、該隣接する2つのスイッチングトランジスタの各ゲートから絶縁されかつ該隣接する2つのスイッチングトランジスタのソースまたはドレインに電気的に接続され、上面がスイッチングトランジスタの上面よりも高い位置にあるコンタクトプラグと、コンタクトプラグの上面上に設けられ、データを記憶する記憶素子と、記憶素子上に設けられた配線とを備えている。

(もっと読む)

薄膜素子用基板の製造方法、薄膜素子の製造方法、薄膜トランジスタの製造方法、薄膜素子、および薄膜トランジスタ

【課題】本発明は、表面平滑性に優れ、薄膜素子の特性劣化を抑制することが可能な薄膜素子用基板が得られる新規な薄膜素子用基板の製造方法を提供することを主目的とする。

【解決手段】本発明は、金属基材に薬液処理を施す金属基材表面処理工程と、上記金属基材上にポリイミド樹脂組成物を塗布して絶縁層を形成する絶縁層形成工程とを有し、上記絶縁層の表面粗さRaが30nm以下であることを特徴とする薄膜素子用基板の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

半導体デバイスの製造方法及び積層化半導体デバイスの製造方法

【課題】半導体デバイスの薄型化工程および分割工程における半導体デバイスの歩留まり低下を抑制し、基板両面に配線層を有する半導体デバイスの製造方法を提供する。

【解決手段】半導体デバイス110の製造方法は、基板101の一方の面に第1の半導体素子102を形成する工程と、第1の半導体素子102上に第1の配線層104を形成する工程と、支持基板上に保護樹脂層を形成する工程と、第1の配線層104と保護樹脂層とが接触するように、支持基板を基板101に支柱を介して固定する工程と、基板101の他方の面側に第2の配線層404を形成する工程と、基板101の一部及び支柱の一部又は全部を除去して基板101と支持基板とを分離する工程と、を含むことを特徴とする。

(もっと読む)

表示装置の作製方法

【課題】液滴吐出法により吐出する液滴の着弾精度を飛躍的に向上させ、微細でかつ精度の高いパターンを基板上に直接形成することを可能にする。もって、基板の大型化に対応できる配線、導電層及び表示装置の作製方法を提供することを課題とする。また、スループットや材料の利用効率を向上させた配線、導電層及び表示装置の作製方法を提供することを課題とする。

【解決手段】液滴吐出法による液滴の吐出直前に、所望のパターンに従い基板表面上の液滴着弾位置に荷電ビームを走査し、そのすぐ後に該荷電ビームと逆符号の電荷を液滴に帯電させて吐出することによって、液滴の着弾位置の制御性を格段に向上させる。

(もっと読む)

半導体装置の製造方法

【目的】ウェット処理を行った場合でも絶縁膜上に庇形状が形成されない半導体装置の製造方法を提供する。

【構成】本発明の一態様の半導体装置の製造方法は、基板上に絶縁膜を形成する工程(S102)と、絶縁膜上に保護膜を形成する工程(S104)と、保護膜に第1の開口部を形成する工程(S114)と、第1の開口部内に保護膜よりもウェットエッチングレートが大きい犠牲膜を形成する工程(S116)と、第1の開口部内の犠牲膜に第1の開口部よりも幅の狭い第2の開口部を形成する工程(S122の一部)と、第2の開口部を転写することで絶縁膜に第3の開口部を形成する工程(S122の一部)と、第3の開口部が形成された後に、ウェット処理を行なう工程(S126)と、ウェット処理後に、第3の開口部内にバリアメタル膜を形成する工程(S128)と、第3の開口部内に導電性材料を埋め込む工程(S132)と、を備えたことを特徴とする。

(もっと読む)

半導体装置製造方法及び積層半導体装置

【課題】複数の基板を貼り合わせる積層半導体装置を効率よく製造できる方法を提供する。

【解決手段】複数の基板を貼り合わせて積層半導体装置を製造する半導体装置製造方法であって、回路が形成された複数の基板のうちの一の基板に凹部を形成する凹部形成ステップと、一の基板を複数の基板のうちの他の基板に重ね合わせる重ね合わせステップと、重ね合わせステップの後に、一の基板の凹部に導電性材料を導入することにより、一の基板の回路と他の基板の回路との間の電気的な導通路を形成する導通形成ステップとを備える半導体装置製造方法が提供される。

(もっと読む)

半導体装置の製造方法

【目的】Cu配線寿命の劣化と絶縁膜の絶縁性劣化を共に低減する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、チャンバ内面にシリコン(Si)膜を表面層とする多層膜を形成する工程(S102)と、前記多層膜が内面に形成されたチャンバ内に、表面に銅(Cu)配線と絶縁膜とが形成された基板を配置して、希ガスプラズマ処理を行なう工程(S106)と、を備えたことを特徴とする。

(もっと読む)

電子デバイスの製造方法

【課題】配線部をスパッタリングにより形成するスパッタ配線工程において、基板の外周部を、スパッタ装置内のヒーターとクランプリングとにより挟み込み、基板を保持することによる、基板の欠けの発生を抑制する。

【解決手段】緩衝層形成工程において、基板1の表面1Aに緩衝層3を形成するとともに、緩衝層3の材料と同じ材料を用いて、緩衝層形成工程の保護層形成工程を実施し、半導体装置10の製造方法を複雑化させることなく、基板1の表面1Aの外周部1B、および裏面1Dの外周部1Eに保護層4を形成するので、緩衝層形成工程の後に実施するスパッタ配線工程において、基板1の表面1Aおよび裏面1Dを直接挟み込むことなく、保護層4を介在させて挟み込み、基板1を保持することができ、基板1、特に基板1の外周部1B、および外周部1Eに欠けが発生することを抑制して、スパッタ膜11を形成することができる。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】絶縁表面上に第1配線と、前記第1配線を覆う第1層間絶縁膜と、前記第1層間絶縁膜上の一部に接して第2層間絶縁膜と、前記第1層間絶縁膜及び前記第2層間絶縁膜上に第2配線とを有し、前記第1配線と前記第2配線とが重なっている領域には、前記第1層間絶縁膜と前記第2層間絶縁膜とが積層された半導体装置である。第1配線と第2配線間に層間絶縁膜が積層されていることで寄生容量の低減が可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】設計基準を遵守しつつ容量値を向上しうる容量素子を有する半導体装置及びその製造方法を提供する。

【解決手段】複数の電極パターンをそれぞれ有し、積み重ねるように配置された複数の配線層と、複数の配線層の間にそれぞれ設けられ、隣接する配線層の複数の電極パターンのそれぞれを電気的に接続する複数のビア部と、複数の配線層及び複数のビア部の間隙に形成された絶縁膜とを有する容量素子を有し、ビア部は、電極パターンの中心に対して、電極パターンの延在方向と交差する方向にずらして配置されており、電極パターンは、ビア部が接続された部分において線幅が太くなっており、隣接する電極パターンとの間の間隔が狭まっている。

(もっと読む)

半導体装置のパッド構造

【課題】半導体装置のパッド構造を提供する。

【解決手段】半導体装置200は、半導体基板202、相互接続構造、複数のダミーメタルビア235及びパッド構造を備える。半導体基板202は、内部に複数の微小電子素子が設けられている。相互接続構造は、半導体基板202上に設けられ、複数の金属層210a〜210iと、金属層を隔離する複数のIMD層220とを有する。金属層210a〜210iは、最上金属層210iと、最下金属層210aと、最上金属層210iと最下金属層210aとの間に設けられた少なくとも2層の金属層とを含む。複数のダミーメタルビア235は、少なくとも2層の金属層間に設けられた1層又は2層以上のIMD層220内に形成される。パッド構造は、ダミーメタルビア235の上に直接設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】放熱性に優れ、製造歩留まりの向上を図ることができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】

半導体装置は、基板1の上方に設けられた化合物半導体層2,3,4と、化合物半導体層2,3,4の上方に設けられた複数のソース電極7及び複数のドレイン電極9と、化合物半導体層2,3,4を貫通し、複数のソース電極7のそれぞれに接続される複数のビア配線22と、化合物半導体層2,3,4を貫通し、複数のドレイン電極9のそれぞれに接続される複数のビア配線23と、複数のビア配線22に接続され、基板1に埋め込まれたソース共通配線18と、複数のビア配線23に接続され、基板1に埋め込まれたドレイン共通配線20とを有する。

(もっと読む)

集積回路および集積回路の製造方法

【課題】トランジスタのゲート電極上に第1の誘電体層を形成し、かつ金属層と接合したダマシン構造を形成する方法を提供する。

【解決手段】トランジスタのゲート電極上に第1の誘電体層を形成し、第1の誘電体層上にエッチストップ層を形成し、第1の誘電体層およびエッチストップ層を貫通する開口を形成し、トランジスタのソース/ドレイン(S/D)領域を露出し、開口内に、エッチストップ層の第1の上面と少なくとも部分的に実質的に同じ高さである表面を有する金属層を形成して、トランジスタのS/D領域に接触させ、さらに金属層と接合したダマシン構造を形成する。

(もっと読む)

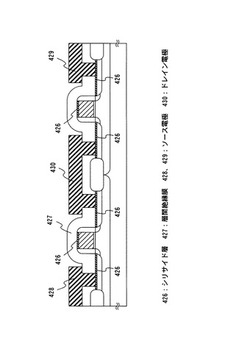

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体層を用いた、表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供することを課題の一つとする。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させることができる。

(もっと読む)

半導体装置

【課題】温度が上昇するほど電子又はホールの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板中のPウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Pウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ負の膨張係数を有しチャネル領域に引っ張り応力を加える第1絶縁層20を備えたN型の絶縁ゲート型電界効果トランジスタN1と、半導体基板中のNウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Nウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ正の膨張係数を有しチャネル領域に圧縮応力を加える第2絶縁層30を備えたP型の絶縁ゲート型電界効果トランジスタP1とを具備する。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】画素、メモリ部、又はCMOS回路等に配置されたトランジスタのチャネル形成領域213、214と重なる第1の配線(ゲート電極)の一部または全部と第2の配線(ソース線またはドレイン線)154、157とを重ねる。また、ゲート電極と第2配線154、157の間には第1の層間絶縁膜149及び第2の層間絶縁膜150cを設け、寄生容量を低減した半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】保護膜の亀裂や膜剥がれを防止する。

【解決手段】化合物半導体基板1上に少なくとも一層からなる下層配線2を形成し、化合物半導体基板1上に有機材料からなる層間膜3を堆積し、層間膜3上に金からなる上層配線5を形成し、層間膜3中に下層配線2と上層配線5とを接続するヴィア4を形成し、上層配線5の表面および層間膜3の表面の上にシリコン窒化膜からなる密着性向上用膜6を形成し、密着性向上用膜6上にシリコン酸化膜からなる熱膨張抑制膜7を形成し、熱膨張抑制膜7上にシリコン窒化膜からなる保護膜8を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置における被研磨面の平坦性を向上させる。

【解決手段】凸状パターンが形成された下地の上に埋め込み層を形成して前記凸状パターンを埋め込む工程と、前記凸状パターンの上の前記埋め込み層に異方性エッチングを施して、前記凸状パターンの上の前記埋め込み層に凹部を形成する工程と、前記絶縁膜の表面を化学機械研磨により研磨する工程と、を備えたことを特徴とする半導体装置の製造方法が提供される。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

61 - 80 / 407

[ Back to top ]