Fターム[5F033SS08]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | PVD(物理的気相成長法) (621) | スパッタ (435)

Fターム[5F033SS08]の下位に属するFターム

反応性スパッタ (28)

Fターム[5F033SS08]に分類される特許

81 - 100 / 407

表示装置およびその作製方法

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、画素部に酸化物半導体を用いた薄膜トランジスタを用い、さらに駆動回路の少なくとも一部の回路も酸化物半導体を用いた薄膜トランジスタで構成する。同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

配線を形成する方法及び半導体装置の作製方法

【課題】生産性がよく、信頼性を向上した配線の作製方法とそれを用いた半導体装置の作製方法を提供する。

【解決手段】液滴吐出法によりゲート電極を形成する半導体装置の作製方法であって、基板上に半導体を形成し、半導体上にゲート絶縁膜を形成し、ゲート絶縁膜上に絶縁膜を形成し、絶縁膜にコンタクトホールを形成し、コンタクトホールにバリア膜として機能する金属膜をスパッタリング法または蒸着法により形成し、液滴吐出法により、コンタクトホールに銅からなる導電層をコンタクトホールを充填するように形成し、金属膜と導電層からなるゲート電極を形成する半導体装置の作製方法。

(もっと読む)

不揮発性記憶装置

【課題】第1の配線と第2の配線との交差部に整流素子と不揮発性記憶素子を有する不揮発性記憶装置で、従来に比して高さを抑えることができる不揮発性記憶装置を提供する。

【解決手段】第1の方向に延在するビット線BLと、ビット線BLとは異なる高さに形成され、第2の方向に延在するワード線WLと、ビット線BLとワード線WLとが交差する位置にビット線BLとワード線WLの間に挟持されるように配置される抵抗変化型メモリセルと、を備え、抵抗変化型メモリセルは、抵抗変化素子20がN型半導体層10とP型半導体層30で挟まれた構造を有する。

(もっと読む)

カーボンナノチューブへの金属接合方法及びカーボンナノチューブを用いた配線構造

【課題】 カーボンナノチューブと電極をなす金属とを強い結合力でかつ十分な密着性を持って接合できるカーボンナノチューブへの金属接合方法及びCNTを用いた配線構造を提供する。

【解決手段】本発明のカーボンナノチューブへの金属接合方法は、カーボンナノチューブを成長させる工程と、成長させたカーボンナノチューブの欠陥に硫黄原子を導入する工程と、前記硫黄原子を介して、Au、Ag、Pt、Pd、Ru、Rh、Os、Ir、Hg、Si、Ga及びAsの中から選択された少なくとも1つの金属またはこれらの合金を接合する工程とを、含む。

(もっと読む)

半導体装置

【課題】下層導電層の表面を十分保護することができ、信頼性が高く、配線容量が小さなデュアルダマシン配線を有する半導体装置の製造方法を提供する。

【解決手段】導電性領域11を有する下地と10、下地の表面を覆う絶縁性エッチストッパ膜12と、絶縁性エッチストッパ膜上に形成された層間絶縁膜と、層間絶縁膜表面から第1の深さで形成された配線用溝と、配線用溝底面から導電性領域に達する接続用孔と、配線用溝および接続用孔を埋め込んで形成されたデュアルダマシン配線である。層間絶縁膜が配線用溝の側面および底面を包む第1種の絶縁層15と、第1種の絶縁層よりも下に配置され、第1種の絶縁層とエッチング特性の異なる第2種の絶縁層56とを含む。接続用孔は、断面で見た時に第1種の絶縁層内で傾斜し、上方に向かって次第に開口が増大する部分を有する。

(もっと読む)

貫通電極付き半導体デバイスの製造方法

【課題】既にデバイスや配線が形成されている半導体基板に対し、効率良く貫通電極を形成する貫通電極付き半導体デバイスの製造方法を提供する。

【解決手段】半導体基板11の主面に第1のシリコン酸化膜12を形成し、主面Aからもう一方の主面側の第1のシリコン酸化膜12に達する細孔13を形成し、細孔13の孔壁に第2のシリコン酸化膜14を形成し、第1のシリコン酸化膜12上に第1の金属薄膜15および第2の金属薄膜16を形成し、細孔13の端部における第1のシリコン酸化膜12を除去し、細孔13内に導電性物質を充填し貫通電極17を形成する貫通電極付き半導体基板の製造方法。細孔13を、DRIE法で形成する。導電性物質を、溶融金属吸引法または印刷法により細孔13内に充填する。

(もっと読む)

半導体装置、電子部品、半導体装置の製造方法

【課題】貫通電極の電気特性を効率よく検査する。

【解決手段】本発明の半導体装置2の製造方法は、シリコン基板20に半導体素子を含んだ電気回路を形成する工程と、シリコン基板20を貫通して設けられ、電気回路と電気的に接続される第1貫通電極22を形成する工程と、シリコン基板20を貫通して設けられ、シリコン基板20の表面20aで第1貫通電極22と短絡する第2貫通電極23を形成する工程と、シリコン基板20の裏面20bにおいて、第1貫通電極22と第2貫通電極23との間の電気特性を検査する工程と、を有する。

(もっと読む)

高周波デバイスおよびその製造方法

【課題】基板に開口を有する高周波デバイスを精度よく位置合わせすることが可能な高周波デバイスおよびその製造方法を提供する。

【解決手段】基板11に貫通電極下部14D、開口16および突起17を設ける。基板11の表面に、絶縁膜12、誘電体層13、絶縁膜12と誘電体層13とを貫通する貫通電極上部14Aおよびスイッチング素子15を形成する。基板11には、開口16および突起17を同時に形成したのち、基板11を貫通すると共に貫通電極上部14Aと接する貫通電極下部14Dを形成する。開口16および突起17を同時に形成することにより、インターポーザ基板などの実装基板に精度よく位置合わせすることが可能な高周波デバイス1を、工程数を増やすことなく得ることが可能となる。

(もっと読む)

電界効果型トランジスタの製造方法、電界効果型トランジスタ、表示装置、及び電磁波検出器

【課題】絶縁層へのコンタクトホール形成時における、導電層の浸食や破損の抑制された電界効果型トランジスタの製造方法、電界効果型トランジスタ、表示装置、及び電磁波検出器を提供する。

【解決手段】導電層形成工程によって形成されたソース電極20A、ドレイン電極20B、及び画素電極20Cを含む導電層20上に、該導電層20及び酸化物半導体層18を覆うように、無機材料を主成分とする無機絶縁層23を形成する。そして、この無機絶縁層23上にフォトレジスト膜30を形成してパターン状に露光した後に、現像工程において、現像液を用いて現像することでレジストパターン30B’を形成する。現像工程では、この現像液をエッチング液として用いて、無機絶縁層23の内のレジストパターン30B’から露出した領域を除去することによって導電層20の一部を露出させて、無機絶縁層22にコンタクトホール27を形成する。

(もっと読む)

薄膜のパターニング方法、デバイス及びその製造方法

【課題】本発明は、表面エネルギーの低い薄膜に、ダメージなくパターニングを行う薄膜のパターニング方法、デバイス及びその製造方法を提供することを目的とする。

【解決手段】薄膜20上に、蒸着膜30を積層する工程と、

前記蒸着膜上に、フォトレジスト層40を積層する工程と、

フォトリソグラフィにより、前記フォトレジスト層をパターニングし、パターニングされた前記フォトレジスト層を用いて前記蒸着膜をエッチングしてパターニングする工程と、

パターニングされた前記蒸着膜をパターンマスクとして、前記薄膜をエッチングしてパターニングを行う工程と、を含むことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】電極パッドの損傷を抑制することができる半導体装置を提供する。

【解決手段】半導体基板11と、半導体基板11の上方に形成された電極パッド30とを有し、電極パッド30は、第1の融点温度を有する材料からなる第1の層32と、第1の層32上に位置するとともに外に向けて表出し、第1の融点温度よりも高い第2の融点温度を有する材料からなる第2の層33とを含むことを特徴とする。これにより、外部から電極パッド30への圧力により第1の層32に達する傷ができても、必要に応じて第1の融点以上の温度で加熱することにより電極パッド表面の平坦性を修復することができる。

(もっと読む)

半導体装置

【課題】電極部と貫通電極層の間の抵抗値ばらつきに依存しない信頼性に優れた半導体装置を提供する。

【解決手段】半導体基板表面2aの第1絶縁膜8の中に、外部接続端子を有する電極部18が形成され、基板をビアホール10が貫通し、ビアホール側壁10a及び基板裏面の第2絶縁膜12とビアホール底面の第1絶縁膜とに貫通電極層11が形成され、電極部と貫通電極層との間にシリサイド層9を接続形成し、ビアホール中心軸を含む平面で切断された断面において、シリサイド層の幅A≦ビアホール底部の幅Bである。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

電子素子及びその製造方法、並びに表示装置

【課題】低温プロセスで製造でき、リーク電流が抑制された電子素子を提供する。

【解決手段】基板10上に、端部断面のテーパー角度が60°以下である下部電極22と、前記下部電極22上に配置され、水素原子の含有率が3原子%以下であり、波長650nmにおける屈折率nが1.475以下であるSiO2膜24と、前記SiO2膜24上に配置され、前記下部電極22と重なり部を有する上部電極26と、を有する電子素子である。

(もっと読む)

半導体基板と半導体基板の製造方法および半導体パッケージ

【課題】高信頼性の貫通電極を有する半導体基板と半導体基板の製造方法を提供することを目的とする。

【解決手段】第1絶縁層(2)を介して第1配線層(3)が形成され、貫通孔(4)の内周に第2配線層(5)を形成し、貫通孔(4)は、第1の開口部(4a)と、第1の開口部(4a)よりも開口面積が小さい第2の開口部(4b)で形成され、第2の開口部(4b)に第3配線層(103a)を形成するとともに、第3配線層(103a)を第1の開口部(4a)よりも先に形成することを特徴とする。

(もっと読む)

半導体装置

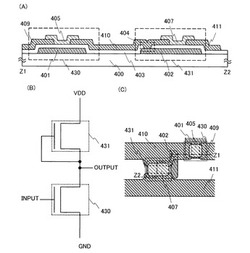

【課題】開口率の高い半導体装置又はその作製方法を提供することを目的の一とする。また、消費電力の低い半導体装置又はその作製方法を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に設けられた半導体層と、半導体層を覆うゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の導電層と第2の導電層とで積層されたゲート電極を含むゲート配線と、半導体層と前記ゲート電極を含む前記ゲート配線を覆う絶縁膜と、絶縁膜上に設けられ、半導体層と電気的に接続され、第3の導電層と第4の導電層とで積層されたソース電極を含むソース配線と、を有し、ゲート電極は、第1の導電層で形成され、ゲート配線は、第1の導電層と第2の導電層で形成され、ソース電極は、第3の導電層で形成され、ソース配線は、第3の導電層と第4の導電層で形成されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置のパターンの微細化が進展した場合においても、工程数を増加させること無く、容易にハードマスクを形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に、少なくとも、層間絶縁膜2と金属配線層3とをこの順で形成する方法であり、金属配線層3は、層間絶縁膜2上に形成された金属膜上にフォトレジスト膜のパターンを形成した後、このフォトレジスト膜の表面に、触媒反応を用いて絶縁体を選択的に堆積させて絶縁ハードマスクを形成するハードマスク形成工程と、次いで、この絶縁ハードマスクを用いて金属膜をエッチング処理するエッチング工程の各工程によって形成される。

(もっと読む)

半導体装置の製造方法

【課題】欠陥の発生を防止し且つ電気的特性に優れた強誘電体キャパシタを用いた半導体装置の製造方法を提供する。

【解決手段】第1の導電層40を形成し、第1の導電層40の表面に酸化膜10を形成し、酸化膜10を大気にさらし、酸化膜10を、減圧下且つ第1の温度で減圧加熱処理し、減圧加熱処理された酸化膜10を大気にさらすことなく、減圧下且つ第1の温度よりも低い第2の温度で、非晶質の第1の誘電体層41を酸化膜10上に形成し、第1の温度よりも高い第3の温度で、非晶質の第1の誘電体層41を結晶化する。

(もっと読む)

半導体装置とその製造方法、電気光学装置とその製造方法、回路基板とその製造方法、及び電子機器

【課題】フォトリソグラフィー法及びエッチング法を用いることなく導電層間を接続することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、基板上に第1導電層と層間絶縁膜と第2導電層とを順に積層形成する導電層工程と、前記第2導電層の表面から物理的加工を施すことで、前記第2導電層と前記層間絶縁膜とを貫通して前記第1導電層に達する凹部を形成するコンタクトホール形成工程と、を有することを特徴とする。

(もっと読む)

81 - 100 / 407

[ Back to top ]