Fターム[5F033SS10]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | PVD(物理的気相成長法) (621) | 真空蒸着 (77)

Fターム[5F033SS10]に分類される特許

61 - 77 / 77

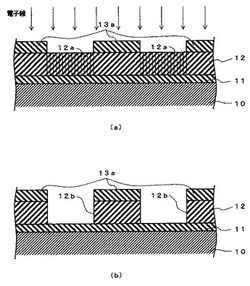

半導体装置の製造方法

【課題】絶縁膜のドライエッチング工程を含む半導体装置の製造方法において、エッチング加工制御性を向上する手段を提供する。

【解決手段】下部構造部10上のストッパー膜11上に炭素元素を含む絶縁膜である被加工膜12を形成する。この上にマスクパターン13aを形成し、このマスクパターンをマスクに被加工膜に向けて電子線等のエネルギー注入を行って被加工膜に硬化部位12aを形成し、このマスクパターンをマスクに被加工膜の硬化部位を異方性エッチングし溝12bを形成する。

(もっと読む)

障壁冗長構成要素を有する相互接続構造体および相互接続構造体を形成する方法

【課題】障壁冗長構成要素を有する相互接続構造体と、相互接続構造体を形成する方法とを提供する。

【解決手段】導電性ライン20の部分の上にバイア拡散障壁30が存在する。導電性ライン20の上で障壁30がない部分に存在する導電性材料54は、導電性ライン拡散障壁22とバイア拡散障壁30との間の電気的経路を提供する。従って、導電性材料54、導電性ライン拡散障壁22およびバイア拡散障壁30を用いて、内部障壁冗長構成要素が形成される。障壁冗長構成要素によって提供されるこの電気的経路によって、バイア底部のEM不良から生じる突然の回路開放を回避することができる。従って、監視デバイスによってEM不良が検出された後、チップ交換またはシステム操作調節のために十分な時間を提供する障壁冗長構成要素が相互接続構造体に提供される。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】基板上にトランジスタ等の半導体素子とセンサーとを作り込んで設ける場合に、同一工程で作製することにより得られる半導体装置およびその作製方法を提供することを目的とする。

【解決手段】同一基板上に、互いに接する第1の領域および第2の領域を有する第1の半導体膜と、チャネル領域とソースまたはドレイン領域として機能する第3の領域とを有する第2の半導体膜と、第1の半導体膜および第2の半導体膜を覆って設けられた絶縁膜と、絶縁膜上に設けられ且つ第1の領域と電気的に接続する第1の導電膜と、第2の領域と電気的に接続する第2の導電膜とを設け、第1の領域、第2の領域および第3の領域に不純物元素を第1の領域と第2の領域に含まれる不純物元素の濃度が異なるように導入する。

(もっと読む)

スペーサレスFET及びデュアル・ライナ法による歪み強化を増加させる構造体及び方法

【課題】 スペースレスFET及びデュアル・ライナ法による歪み強化を増加させる構造体及び方法を提供する。

【解決手段】 歪み強化がnFET及びpFETデバイスの両方に対して達成される半導体構造体及びそれを製造する方法を提供する。特に、本発明は、より強い歪み強化及び欠陥削減のための少なくとも1つのスペーサレスFETを提供する。少なくとも1つのスペーサレスFETは、pFET、nFET又はそれらの組合せとすることができるが、一般に、pFETはnFETよりも大きな幅を有するように製造されるので、スペーサレスpFETが特に好ましい。少なくとも1つのスペーサレスFETは、スペーサを有するFETを含んだ従来技術の構造体よりも、デバイス・チャネルにより接近した応力誘起ライナを設けることを可能にする。スペーサレスFETは、スペーサレスFETの下側に侵入しない、対応するシリサイド化ソース/ドレイン拡散コンタクトの抵抗に悪影響を与えることなく達成される。

(もっと読む)

配線パターンの形成方法及びデバイスの製造方法

【課題】細い線状の微細パターンを、精度よく安定して形成することができる配線パターンの形成方法及びデバイスの製造方法を提供する。

【解決手段】隔壁構造体が、その幅が機能液Lの飛翔径よりも小さいゲート電極溝部56aと、ゲート電極溝部56aの一部に形成され、その幅が機能液Lの飛翔径以上であり、かつ、外周の少なくとも一部に円弧を有する形状であるゲート電極補助溝部57aとを有し、ゲート電極補助溝部57a内に前記機能液Lを配置する工程と、機能液Lによりゲート電極補助溝部57aにゲート電極補助部を形成すると共に、機能液Lの毛管現象によりゲート電極溝部56aにゲート電極補助部に接続されるゲート電極を形成する工程と、を備える.

(もっと読む)

膜パターンの形成方法、デバイス、電気光学装置、及び電子機器

【課題】 幅の異なる幾つかの領域を有するパターン形成領域に機能液を配置する場合等において、形成される膜パターン間での膜厚さを無くした該膜パターンの形成方法を提供する。

【解決手段】 本発明の膜パターンの形成方法は、基板48上に所定パターンのバンク34を形成するバンク形成工程と、前記形成したバンク34に対してフッ素化処理を施す撥液化処理工程と、前記撥液化処理後、前記バンク34に区画されたパターン形成領域55,56に機能液を配置する機能液配置工程と、前記配置した機能液を乾燥させる乾燥工程と、を含み、前記バンク形成工程は、前記基板48上に第1バンク層34aを形成する第1バンク層形成工程と、前記形成した第1バンク層34a上に、該第1バンク層34aよりもフッ素化され易い第2バンク層34bを形成する第2バンク層形成工程と、を含むことを特徴とする。

(もっと読む)

不揮発性記憶素子とその製造方法

【課題】 本発明は上記の問題に鑑みてなされたものであり、その目的は、情報の書込み時及び消去時における過渡電流を小さくし、消費電流を低減することができる不揮発性記憶素子及びその製造方法を提供する点にある。

【解決手段】 電気抵抗状態の高低を情報として記憶することができる可変抵抗体4と、可変抵抗体4に接する複数の電極2を備えてなる不揮発性記憶素子であって、複数の電極2の内の少なくとも1つの電極2の可変抵抗体4との接触面積が、不揮発性記憶素子の作製に用いる製造プロセスの最小加工寸法の2乗よりも小さいことを特徴とする。

(もっと読む)

最新のLow−k材料のための紫外線硬化法

【課題】最新のLow−k材料のための紫外線硬化法の提供。

【解決手段】改善された弾性率及び材料硬度を有する低誘電率材料。このような材料の製造方法は、誘電材料を準備すること、及び、該材料を紫外線(UV)硬化させて、UV硬化誘電材料を製造することを含む。UV硬化は、改善された弾性率及び材料硬度を有する材料をもたらす。改善は、それぞれ、典型的には、50%より大きいか、又は約50%である。UV硬化誘電材料は、所望により、UV後処理され得る。UV後処理は、LIV硬化誘電材料と比べて、材料の誘電率を低下させ、更に、改善された弾性率及び材料硬度を維持する。UV硬化誘電体は、更に、炉での硬化法よりも、硬化において、より低い総熱量を示し得る。

(もっと読む)

半導体デバイス及びその製造方法

【課題】低抵抗配線および低抵抗高アスペクト比ビアプラグを実現するSiCパワーデバイスを提供する。

【解決手段】半導体デバイスは、炭化珪素半導体基板11と、炭化珪素半導体基板11の主面上に形成されたソース電極(オーミック電極)15と、ソース電極15と電気的接続をとるためのビアプラグ25または配線21と、炭化珪素半導体基板11の裏面に形成されたドレイン電極(オーミック電極)22とを備えている。ビアプラグ25または配線21は、ドレイン電極22のシンター温度よりも高い融点の材料、好ましくはタングステンまたは銅を用いる。

(もっと読む)

表示装置、及び表示装置の作製方法

【課題】信頼性の高い表示装置を低いコストで歩留まり良く製造することができる技術を提供することを目的とする。

【解決手段】一導電型の不純物領域を含む半導体層と、半導体層上にゲート絶縁層と、ゲート電極層と、一導電型の不純物領域と接する配線層と、ゲート絶縁層上に設けられ、配線層と接する導電層と、導電層と接する第1の電極層と、第1の電極層上に電界発光層と、第2の電極層とを有し、配線層は導電層を介して第1の電極層と電気的に接続している。

(もっと読む)

半導体集積回路用キャパシタ

【課題】 層間絶縁膜に埋め込まれた導電プラグ上にキャパシタを形成する場合、その導電プラグ上にPZTなどを成膜する際の成膜温度を抑える必要性がなく、且つ、PZTの製造時に生じる酸素の下部電極への内向拡散を抑制することを可能にしようとする。

【解決手段】 層間絶縁膜1に埋め込まれた導電性プラグ2の頂面を含む領域にSiO2 、SiN、Al2 O3 から選択されたアモルファスの第1層3A、第1層3A上に形成されたTiAlN或いはTi/TiAlNからなる第2層3B、Ir或いはIrO2 からなる第3層3Cで構成された下部電極3と、下部電極3上に順に形成された誘電体層4及び上部電極5とを備える。

(もっと読む)

局部エッチストッパーを有する半導体メモリ素子及びその製造方法

【課題】局部エッチストッパーを有する半導体メモリ素子及びその製造方法を提供する。

【解決手段】セル領域及びコア/周辺領域に区分され、素子分離膜210が形成されてアクティブ領域205が限定されている半導体基板200を提供し、半導体基板の所定領域にゲート電極構造体を形成し、その両側のアクティブ領域にソース、ドレーン領域を形成し、半導体基板の結果物上部に層間絶縁膜235を形成した後、セル領域のソース、ドレーン領域が露出されるように層間絶縁膜の所定部分をエッチングし、露出されたソース、ドレーン領域とコンタクトされるように自己整列コンタクトパッド240a,240bを形成し、層間絶縁膜を所定厚さを除去し、その後、セル領域の層間絶縁膜が除去された空間にエッチストッパー245aを形成し、コア/周辺領域のゲート電極構造体の側壁にトップスペーサー245bを形成する段階を含む半導体メモリ素子の製造方法である。

(もっと読む)

高周波信号伝送回路の製造方法及び高周波信号伝送回路装置

【課題】

低誘電損失を実現しつつ集積化が図れ、さらに反射損失を低減できる高周波信号伝送回路の製造方法及び高周波信号伝送回路装置を提供すること。

【解決手段】

中空部4、つまり半導体基板1上に設けられた凹部4の側面には、エッチストッパー材2aが設けられている。このようにエッチストッパー材2aが設けられることにより、エッチングによって、凹部4の領域と凹部4以外の半導体基板1の領域との境界に沿って、寸法誤差を低減しつつ、凹部4を形成することができる。寸法誤差を低減することができる結果、特性インピーダンスを整合させることができ反射損失を低減できる。

(もっと読む)

室温金属直接ボンディング

貼り合わされたデバイス構造であって、好ましくはデバイスまたは回路に接続された第1の組の金属ボンディングパッドおよび第1の基板上の金属ボンディングパッドに隣接する第1の非金属領域を有する第1の基板、好ましくはデバイスまたは回路に接続された第1の組の金属ボンディングパッドに隣接する第2の組の金属ボンディングパッド、および第2の基板上の金属ボンディングパッドに隣接する第2の非金属領域を有する第2の基板、および第2の非金属領域に対して第1の非金属領域を接触ボンディングさせることにより形成される第1と第2の組の金属ボンディングパッドの間の接触ボンディングされた界面を含むボンディングされたデバイス構造。第1と第2の基板の少なくとも一方は弾性的に変形され得る。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】従来のCMPプロセスを用いることなく、高アスペクト比の開口を有する接続孔にも良好な埋め込みが可能である半導体装置の作製方法を提供する。また、従来よりも少ない工程数で、配線形成が可能な方法を提供することを目的とする。更には、高集積化された半導体装置の歩留まり高い作製方法を提案する。

【解決手段】複数の空孔を有する絶縁膜表面に撥水表面を有する膜を形成し、撥水表面を有する膜の一部に光を照射して、親水表面を有する領域を形成した後、親水表面を有する領域に導電性粒子を有する液状物質を吐出し、焼成して導電膜を形成することを特徴とする。

(もっと読む)

絶縁膜形成方法

【課題】導電性基板若しくは半導電性基板に設けられた非常に微細な貫通孔の内側表面であっても、均一な絶縁膜を形成することができるとともに、貫通孔の開口部においても内部においても確実に信頼性の高い絶縁膜を形成することができる絶縁膜形成方法を提供すること。

【解決手段】導電性基板若しくは半導電性基板に設けられた貫通孔の内表面に絶縁膜を形成する絶縁膜形成方法として、前記貫通孔の開口部に第1の絶縁膜を形成する工程と、該貫通孔の内表面に第2の絶縁膜を形成する工程と、該第2の絶縁膜を硬化させる工程とを有することを特徴とする。ここで、第1の絶縁膜は、物理的蒸着方法又は化学的蒸着方法によって形成された絶縁膜であり、第2の絶縁膜は、電着塗装によって形成された絶縁膜である。

(もっと読む)

集積回路デバイス内の相互接続構造体

【課題】 フォトレジスト汚染の問題に悩まされないデュアル・ダマシン構造体を形成する方法を提供すること。

【解決手段】 本発明は、集積回路デバイス内のデュアル・ダマシン相互接続構造体の製造に関する。具体的には、平坦化材料及び拡散障壁材料を用いて、低kの誘電体薄膜内にシングル又はデュアル・ダマシン構造体を形成するための方法が開示される。この方法の好ましいデュアル・ダマシンの実施形態において、最初に誘電体材料にビアを形成し、次にビア内及び誘電体材料上に平坦化材料を付着させ、平坦化材料上に障壁材料を付着させる。次に、リソグラフィにより像形成材料にトレンチが形成され、障壁材料を通して平坦化材料がエッチングされ、トレンチ・パターンが誘電体材料に転写される。これらのエッチング・ステップの過程の間及び該エッチング・ステップの過程に続いて、像形成材料、障壁材料及び平坦化材料が除去される。次に、結果として得られるデュアル・ダマシン構造を金属化することができる。この方法を用いる場合、層間誘電体材料によるフォトレジスト汚染の問題が軽減される。

(もっと読む)

61 - 77 / 77

[ Back to top ]