Fターム[5F033SS10]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | PVD(物理的気相成長法) (621) | 真空蒸着 (77)

Fターム[5F033SS10]に分類される特許

21 - 40 / 77

相互接続構造およびこれを形成する方法(細い相互接続開口のための導電性構造)

【課題】電気的抵抗が低い相互接続構造、および、かかる相互接続構造を形成する方法を提供する。

【解決手段】相互接続構造は、少なくとも1つの開口を含む誘電物質を含む。少なくとも1つの開口内には、任意のバリア拡散層、結晶粒成長促進層、凝集めっきシード層、任意の第2のめっきシード層、および導電性構造が配置される。典型的にはCuである金属含有導電性物質を含む導電性構造は、バンブー微細構造を有し、平均グレイン・サイズが0.05ミクロンよりも大きい。いくつかの実施形態では、導電性構造は、(111)結晶方位を有する導電性結晶粒を含む。

(もっと読む)

ビアがガウジングされた相互接続構造体及びその製造方法

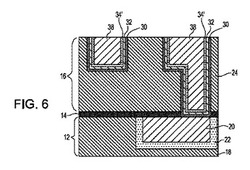

【課題】 ビア開口部の底部にガウジング構造部を含む相互接続構造体、及びその形成方法を提供する。

【解決手段】 本発明の方法は、ビア開口部の上に配置されるライン開口部内の堆積されたトレンチ拡散バリアの被覆率に影響を与えず、及び/又は、ビア開口部及びライン開口部を含む相互接続誘電体材料内にスパッタリングを行なうことによりビア開口部の底部にガウジング構造部を生成することに起因する損傷を生じさせない。こうした相互接続構造体は、最初に相互接続誘電体内にライン開口部を形成し、その後、ビア開口部、次いでガウジング構造部を形成することによって、ビア開口部の底部内にガウジング構造部を提供することにより達成される。

(もっと読む)

半導体装置

【課題】下層導電層の表面を十分保護することができ、信頼性が高く、配線容量が小さなデュアルダマシン配線を有する半導体装置の製造方法を提供する。

【解決手段】導電性領域11を有する下地と10、下地の表面を覆う絶縁性エッチストッパ膜12と、絶縁性エッチストッパ膜上に形成された層間絶縁膜と、層間絶縁膜表面から第1の深さで形成された配線用溝と、配線用溝底面から導電性領域に達する接続用孔と、配線用溝および接続用孔を埋め込んで形成されたデュアルダマシン配線である。層間絶縁膜が配線用溝の側面および底面を包む第1種の絶縁層15と、第1種の絶縁層よりも下に配置され、第1種の絶縁層とエッチング特性の異なる第2種の絶縁層56とを含む。接続用孔は、断面で見た時に第1種の絶縁層内で傾斜し、上方に向かって次第に開口が増大する部分を有する。

(もっと読む)

薄膜のパターニング方法、デバイス及びその製造方法

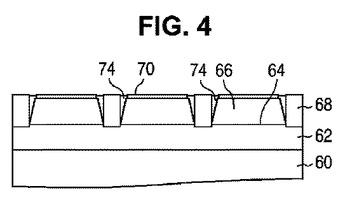

【課題】本発明は、表面エネルギーの低い薄膜に、ダメージなくパターニングを行う薄膜のパターニング方法、デバイス及びその製造方法を提供することを目的とする。

【解決手段】薄膜20上に、蒸着膜30を積層する工程と、

前記蒸着膜上に、フォトレジスト層40を積層する工程と、

フォトリソグラフィにより、前記フォトレジスト層をパターニングし、パターニングされた前記フォトレジスト層を用いて前記蒸着膜をエッチングしてパターニングする工程と、

パターニングされた前記蒸着膜をパターンマスクとして、前記薄膜をエッチングしてパターニングを行う工程と、を含むことを特徴とする。

(もっと読む)

半導体発光デバイス上に誘電体層を形成する方法

n型領域とp型領域との間に配置された発光層を有する半導体構造が形成される。n型領域の一部上に第1のメタルコンタクトが形成され、p型領域の一部上に第2のメタルコンタクトが形成される。第1及び第2のメタルコンタクトは半導体構造の同一面上に形成される。第1のメタルコンタクトと第2のメタルコンタクトとの間の誘電体材料が配置される。該誘電体材料は、半導体構造の一部、第1のメタルコンタクトの一部、及び第2のメタルコンタクトの一部と直接的に接触する。第1のメタルコンタクトの表面と、第2のメタルコンタクトの表面と、該誘電体材料の表面とを含む平坦面が形成される。  (もっと読む)

(もっと読む)

半導体構造体及びその形成方法

【課題】 相互接続構造の信頼性及び拡張性を改善する相互接続構造のための冗長金属拡散バリア層を提供する。

【解決手段】 冗長金属拡散バリア層は、誘電体材料内に設けられた開口内に配置され、且つ開口内に存在する拡散バリア層及び導電性材料の間に配置される。冗長拡散バリア層は、Ru並びに純粋なCo若しくはN,B及びPのうちの少なくとも1つを含むCo合金からなる単層若しくは多層構造である。

(もっと読む)

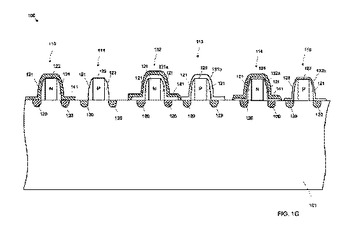

ストレス低減層を有する集積回路装置

集積回路装置が開示され、集積回路装置はNMOSゲート薄膜スタック(122)を覆う張力ストレス層(141)を有するデュアルストレスライナーNMOSデバイス(110)と、PMOSゲート薄膜スタック(123)を覆う圧縮ストレス層(142)を有するデュアルストレスライナーPMOSデバイス(111)と、張力ストレス層(141)とNMOSゲート薄膜スタック(124)との間に延在するストレス低減層(131a)を有する低減ストレスのデュアルストレスライナーNMOSデバイス(112)と、圧縮ストレス層(142)とPMOSゲート薄膜スタック(125)との間に延在するストレス低減層(131b)を有する低減ストレスのデュアルストレスライナーPMOSデバイス(113)とを含む。発明の実施形態において、追加の低減ストレスのデュアルストレスライナーNMOSデバイス(114)と低減ストレスのPMOSデバイス(115)とは、ストレス低減層(132a,132b)の厚みおよび/または材料特性を変更することによって形成される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】低コストでウエハ周辺部における歩留まりを向上させる。

【解決手段】基板上に層間絶縁膜を形成する層間絶縁膜工程と、層間絶縁膜上にポジレジストを塗布するレジスト塗布工程と、配線パターンを露光する際の露光エネルギーよりも高いエネルギーの光を基板の周辺領域に照射し、ポジレジストをネガ化させる周辺露光と、ポジレジストに配線パターンを露光するパターン露光とを行う露光工程と、ネガ化させたポジレジストを残して、パターン露光により露光された領域のポジレジストを現像により除去する現像工程と、現像工程後に残ったポジレジストをマスクとして、前記層間絶縁膜をエッチングするエッチング工程と、ポジレジストを除去し、層間絶縁膜のエッチングされた領域に配線材料を埋め込む埋込工程と、研磨により層間絶縁膜表面を平坦化し配線材料の配線層を形成する平坦化工程と、を有する半導体装置の製造方法により上記課題を解決する。

(もっと読む)

金属−絶縁体相転移材料を用いた機能要素の形成方法及びこれによって形成された機能要素、並びに機能デバイスの製造方法及びこれによって製造された機能デバイス

【課題】金属−絶縁体相転移材料として二酸化バナジウム(VO2)を用いた機能要素の形成方法及びこれによって形成された機能要素、並びに機能デバイスの製造方法及びこれによって製造された機能デバイスを提供すること。

【解決手段】基板40の面に、金属−絶縁体相転移材料10としてVO2薄膜が形成されており、平行な2つの電極15a、15bがVO2薄膜の面に形成されている。両電極を結ぶ複数の機能要素としての金属配線20a〜20eは、レーザ光源30からのレーザ35がVO2薄膜に走査方向37で走査され、レーザ35によって照射されたVO2薄膜の部分が絶縁相から金属相に相転移して金属化されるにことよって形成される。金属配線が形成された領域の少なくとも一部にレーザを照射し、高温(例えば、100℃)とした後、低温(例えば、室温)に冷却して絶縁体化させて、金属配線が形成された領域の少なくとも一部を消去することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通孔(接続孔)内に形成された絶縁膜上に設けられる配線層と半導体基板との間の電気的絶縁性の不良の発生が低減された半導体装置の製造方法を提供する。

【解決手段】半導体基板11の一方の面上に第1の絶縁層12を介して位置する第1の配線層13と、半導体基板の他方の面から第1の配線層に至る接続孔19を形成する。接続孔の側面から他方の面に亘って半導体基板上に位置し、接続孔内で第1の配線層に接する第2の絶縁層14を形成する。接続孔の側面上から他方の面上に亘って第2の絶縁層上に位置し、接続孔内で第1の配線層に接する第2の配線層16を形成する。この形成において、第2の絶縁層を、膜質の異なる2種の絶縁膜14a、14b又はそれ以上の絶縁膜の積層体から構成する。

(もっと読む)

機能性有機物素子及び機能性有機物装置

【課題】 薄くて軽く、しかも、酸素や水などの外部物質の侵入を阻止する封止性能に優れた封止部材を備えた、カラ−ディスプレイなどに好適な機能性有機物素子及び機能性有機物装置を提供すること。

【解決手段】 まず、絶縁性基板1の上に、有機半導体層4を有する有機薄膜トランジスタを形成する。次に、有機半導体層4への外部物質の侵入を阻止する第1の封止層31を、形成時に有機半導体層4にダメージを与えることが少ない蒸着法や塗布法などで、有機薄膜トランジスタを被覆するように形成する。これとは別に、プラズマCVD法などによって、封止性能の高い第2の封止層33を有機高分子樹脂材32に形成する。次に、第1の封止層31が設けられた基板1に、第2の封止層33が設けられた有機高分子樹脂材32を、防湿性樹脂34によって貼り付ける。

(もっと読む)

電子デバイスの製造方法

【課題】成膜時に生じる反りを緩和しうる電子デバイスの製造方法を提供する。

【解決手段】まず、4H−SiC基板10の第1面10aの上に、第1タングステン膜11を堆積する。堆積は、基板温度を400℃〜600℃に保持した状態で、スパッタによって行われる。スパッタ後に室温まで冷却すると、基板全体が上方に凹になるように反る。その後、4H−SiC基板10の第2面10bの上に、同じ材質、厚さの第2タングステン膜12を堆積する。4H−SiC基板10に対する,第1,第2タングステン膜11,12の収縮による応力が互いに釣り合い、反りがなくなる。その後、平坦な基板上にレジスト膜Reを形成して、第1タングステン膜11から注入マスク11aを形成する。正確な注入マスク11aを用いて、高い精度で不純物拡散領域15を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】配線層間の正常な電気的導通が取れている半導体装置を提供することを課題とする。

【解決手段】基板上又は基板の表面層に少なくとも2層の配線層を備え、前記2層の配線層の内、下層配線層がシリコンからなる際に、前記下層配線層と上層配線層間に炭化珪素層を備えたことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

透明薄膜トランジスタ及び画像表示装置

【課題】配線抵抗を低下させて、均一かつ確実に動作させる透明薄膜トランジスタ及び画像表示装置を提供すること。

【解決手段】実質的に透明な基板と、基板上に実質的に透明な導電材料の第1の薄膜と金属材料の第2の薄膜とを2層以上積層して形成されたゲート配線と、ゲート配線上に形成された実質的に透明なゲート絶縁膜と、ゲート絶縁膜上に形成された実質的に透明な半導体活性層と、実質的に透明な半導体活性層を挟んで離間して形成された実質的に透明な導電材料の第5の薄膜と金属材料の第6の薄膜とを2層以上積層して形成されたソース配線と、実質的に透明な半導体活性層を挟み、ソース配線に離間して実質的に透明な導電材料の第7の薄膜で形成されたドレイン電極と、を備えることを特徴とする透明薄膜トランジスタ。

(もっと読む)

アクティブマトリクス基板、ディスプレイパネル、表示装置およびアクティブマトリクス基板の製造方法

【課題】アクティブマトリクス基板の開口率と消費電力とを向上させる。

【解決手段】アクティブマトリクス基板101Aは、透明基板10と、透明基板10上に形成された配線(LG,LD,LP,L1,L2等)と、この配線(LG,LD,LP,L1,L2等)の少なくとも一部を覆う透明半導体層44と、配線(LG,LD,LP,L1,L2等)および透明半導体層44の少なくとも一部を覆う透明な絶縁膜と、を備える。配線(LG,LD,LP,L1,L2等)は、主配線としての第1メタル配線41Mと、これから分岐する副配線としての透明な配線(41,42,43等)と、を含む。主配線としての第1メタル配線41Mは、少なくとも一部が副配線としての配線(41,42,43等)よりも高い導電性を備えた材料を用いて形成される。

(もっと読む)

液晶表示装置用アレイ基板製造用のエッチングテープ

【課題】本発明は液晶表示装置用アレイ基板製造用のエッチングテープを提供する。

【解決手段】本発明のエッチングテープは、ベースシート及びベースシート上にゲルタイプのエッチング物質が塗布されて形成されたエッチング物質層を含む。このエッチングテープは、透明絶縁基板上にゲート電極、ストレージキャパシターの第1電極、ゲート配線を形成する段階、ゲート絶縁膜、アクティブ層、オーミック接触層、ソース電極及びドレーン電極を形成し、誘電体層及びストレージキャパシターの第2電極を形成し、データ配線を形成する段階、画素電極を形成し、ゲートパッド電極を形成し、データパッド電極を形成する段階、保護層を形成する段階及びゲートパッド電極上に形成された保護層とデータパッド電極上に形成された保護層をエッチングすることでコンタクトホールを形成する段階を含む液晶表示装置用アレイ基板の製造方法に利用される。

(もっと読む)

銅めっきされた高アスペクト比のビア、及びその製造する方法

【課題】 最新のスケーリング技術の要件に適応することができ、適切に機能する実行可能なビアを一貫して生成できる、改善されたビア製造プロセスを提供すること。

【解決手段】 改善された高アスペクト比ビア及びそれを形成するための技術が提供される。1つの態様において、銅めっきされた高アスペクト比ビアを製造する方法が提供される。この方法は、以下のステップを含む。誘電体層内に高アスペクト比ビアをエッチングする。高アスペクト比ビア内及び誘電体層の1つ又は複数の表面の上に、拡散バリア領域を堆積させる。拡散バリア層の上に銅層を堆積させる。銅層の上にルテニウム層を堆積させる。高アスペクト比ビアを、ルテニウム層の上にめっきされた銅で充填する。この方法によって形成される銅めっきされた高アスペクト比ビアも提供される。

(もっと読む)

半導体装置及び回路基板

【課題】小型の半導体装置においても静電容量の大きなキャパシタを配置することが可能な構造を有する半導体装置を提供する。

【解決手段】半導体装置1は、半導体素子8が形成された半導体基板2と、半導体基板2のパッシベーション膜12を介して配置され1方向に長く形成された開口部4aを有する平面型のスロットアンテナ4と、スロットアンテナ4と並列接続する共振用キャパシタ15とを備え、共振用キャパシタ15はチップ型素子となっている。

(もっと読む)

相互接続構造体およびその形成方法(エレクトロマイグレーション耐性強化のための相互接続構造体)

【課題】 ビア開口の下部分を多層ライナで内側を覆うことにより強化したエレクトロマイグレーション耐性を有する相互接続構造体を提供する。

【解決手段】 多層ライナは、誘電体材料のパターン付けされた表面から外側に、拡散障壁、マルチ材料層、及び金属含有ハード・マスクを含む。マルチ材料層は、下層の誘電体キャッピング層からの残留物からなる第1材料層と、下層の金属キャッピング層からの残留物からなる第2材料層とを含む。本発明はまた、誘電体材料内に形成されたビア開口の下部分内に多層ライナを含む相互接続構造体を形成する方法を提供する。

(もっと読む)

三次元構造体の製造方法および三次元構造体

【課題】導電体内の欠陥の発生を抑制し、導電体が連続的に形成される三次元構造体の製造方法および三次元構造体を提供する。

【解決手段】第1の導電体上に、絶縁体と、この絶縁体内に、第1の導電体と異なる第2の導電体で構成される縦構造体と横構造体が組み合わされた三次元の擬似導電体構造とを形成する工程と、擬似導電体構造を溶解除去して三次元の空洞を形成し、第1の導電体を露出させる工程と、第1の導電体をシード層として、電解めっき法により第3の導電体を空洞に充填し、三次元の導電体構造を形成する工程を有することを特徴とする三次元構造体の製造方法およびこれによる三次元構造体。

(もっと読む)

21 - 40 / 77

[ Back to top ]