Fターム[5F033TT06]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の構造、形状 (4,088) | 側壁絶縁膜 (2,038)

Fターム[5F033TT06]の下位に属するFターム

コンタクトホールの側壁 (799)

電極、配線の側壁 (1,106)

Fターム[5F033TT06]に分類される特許

81 - 100 / 133

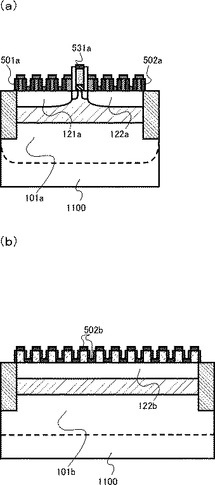

半導体装置の製造方法および半導体装置

【課題】浅いソース、ドレイン接合位置を保ちつつ、ソース、ドレインがシリサイド化され、かつ、接合リークが低く抑えられた半導体装置の製造方法および半導体装置を提供する。

【解決手段】MISFET(金属絶縁物半導体電界効果トランジスタ)を有する半導体装置の製造方法であって、シリコン基板1100の表面に、このMISFETのゲート絶縁膜を形成し、このゲート絶縁膜上にゲート電極を形成し、このゲート電極の両側に、{110}面方位を有するシリコン面上に設けられ、このシリコン面上の<100>方向に垂直な長辺と、この<100>方向に平行で幅が0.5μm以下の短辺からなる矩形状を呈し、MISFETのソース、ドレイン領域の一部を構成する複数のニッケルシリサイド(NiSi)領域501a、502aを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置(チップ)の面積増大を抑制しつつ内部への水分の侵入を防止する。

【解決手段】低誘電性を確保するために多孔質な構造を有するLow‐k膜を用いた層間絶縁膜15,17,19を多層に積層して多層配線構造を形成し、スクライブラインに沿ってレーザーダイシングを半導体基板11表面が露出するまで行う。そして、上記Low‐k膜よりも水分の浸透し難い膜で全体に側壁保護膜22を成膜した後、側壁保護膜22をエッチバックして金属パッド20を露出させると共に、半導体装置側面に成膜された側壁保護膜22を残して、半導体装置側面を側壁保護膜22で保護する。こうして、半導体装置の側面からの水分の浸入を側壁保護膜22によって抑制することにより、半導体装置の回路形成領域の周囲にシールリングを形成する必要を無くし、半導体チップの縮小化を図る。

(もっと読む)

微細コンタクトホールを有する半導体素子の製造方法

【課題】微細コンタクトホールを有する半導体素子の製造方法を提供する。

【解決手段】半導体基板に活性領域を画定する素子分離膜を形成する。前記素子分離膜を有する半導体基板上に層間絶縁膜を形成する。前記層間絶縁膜上に第1モールディングパターンを形成する。前記第1モールディングパターン間に位置して前記第1モールディングパターンと離隔された第2モールディングパターンを形成する。前記第1及び第2モールディングパターンの側壁を囲むマスクパターンを形成する。前記マスクパターン内に開口部を形成するために前記第1及び第2モールディングパターンを除去する。前記マスクパターンをエッチングマスクとして用いて前記層間絶縁膜をエッチングしてコンタクトホールを形成する。

(もっと読む)

半導体素子の金属配線形成方法

【課題】ダマシン構造の金属配線形成において、バリアメタル膜形成工程を省略し、タングステンのグレインサイズを大きくし、電気抵抗の低いタングステン配線を形成する方法を提供する。

【解決手段】半導体基板の上部に絶縁膜及びグルー膜を形成する段階と、上記グルー膜及び絶縁膜の一部を除去してトレンチを形成する段階と、トレンチ側壁に絶縁膜を形成する段階と、トレンチ内部をクリーニングする段階と、ALD法により核生成を行う段階と、トレンチ及びグルー膜を含む上記半導体基板の上部にCVD法によりタングステン膜を形成する段階と、上記絶縁膜が露出されるまで研磨工程を実施してダマシン構造のタングステン配線を形成する段階からなる。

(もっと読む)

貫通シリコンビア及びその形成方法

【課題】積層パッケージの製作時絶縁膜形成費用を節減し、かつ、絶縁膜の絶縁特性を確保し、さらに、絶縁膜の均一度及び低い荒さを確保し、そして、絶縁膜自体の欠陥による素子不良発生を防止する構造を提供する。

【解決手段】多数の半導体チップで構成されたウェハ110の各チップに溝を形成するステップと、前記溝を埋め込むようにウェハ110上に液状のポリマーを形成するステップと、前記ポリマーをパタニングして溝の側壁にポリマーからなる絶縁膜140aを形成するステップと、前記側壁に絶縁膜140aが形成された溝を埋め込むように金属膜170を形成するステップと、前記溝内に埋め込まれている金属膜170が露出されるようにウェハ110の後面をバックグラインディングするステップと、を含む。

(もっと読む)

半導体装置

【課題】本発明は、半導体装置において、装置の性能を向上できるようにすることを最も主要な特徴とする。

【解決手段】たとえば、Si基板11の主表面上には、その垂直方向に対し、板状(あるいは、棒状)のSiポスト11aが形成されている。Siポスト11aでのキャリア移動度を向上させるために、Siポスト11aの各側面には、Si基板11の主表面と直交する垂直方向に伸び応力を与えるための、ストレス印加層21が設置されてなる構成となっている。

(もっと読む)

半導体装置及びその製造方法

【課題】耐湿性が優れた半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1において、シリコンからなる基板2と、基板2上に設けられ金属配線を含まない下地絶縁層3と、下地絶縁層3上に設けられ金属配線6を含む配線層4とを設ける。下地絶縁層3及び配線層4は、基板2の周辺領域Sを除く駆動領域Cのみに形成する。そして、窒化シリコンからなり、駆動領域Cと周辺領域Sとの境界において下地絶縁層3及び配線層4の側面を覆う側壁7を設ける。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電流の局所集中による半導体基板への部分放電を抑制し得る半導体装置を提供する。

【解決手段】半導体装置は、半導体基板(1,5)と、半導体基板(1,5)に埋め込まれたゲート電極(9A,9B)と、ゲート電極(9A,9B)の更に内側に埋め込まれた導電体(15A,15B)と、導電体(15A,15B)と接続されるように半導体基板(1,5)の内部に形成された配線層(3)と、ゲート電極(9A,9B)と導電体(15A,15B)との間に配置された絶縁膜(14)とを備える。導電体(15A,15B)は、半導体基板(1,5)の表面よりも高くなるように形成されている。

(もっと読む)

個別電子コンポーネントのマトリクスを形成する方法および形成されるマトリクス

本発明は、基板(100)上にアクティブ層(101)を形成する段階および少なくとも基板(100)が出現するまで、トレンチ(102)をアクティブ層(101)内に形成することでコンポーネントを個別化する段階を含む、電子コンポーネント(111)のマトリクスを製造する方法に関する。この方法は、アクティブ層(101)上に機能材料の層(102)を蒸着する段階と、前記トレンチ(102)を充填し、電子コンポーネント(111)の上側面に薄膜(115)を形成するように、材料の層(103)上に感光性樹脂(104)を蒸着する段階と、トレンチの樹脂の部分の露光を少なくしつつ樹脂(104)を放射線に少なくとも部分的に曝露する段階と、適切に露光された部分を除去するように樹脂(104)を現像する段階と、現像段階の後、外面に現われる機能材料の層(103)の部分を除去する段階と、樹脂の残り部分を除去する段階とを含む。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 シリコン基板上にBCB等の低誘電率材料からなる絶縁膜と配線とが各々2層交互に積層されて設けられた半導体装置において、絶縁膜間で剥離が生じにくいようにする。

【解決手段】 シリコン基板1の上面に設けられた酸化シリコン等からなるパッシベーション膜3の上面の周辺部を除く領域にはBCB等の低誘電率材料からなる第1、第2の絶縁膜5、9と第1、第2の配線8、12とが交互に積層されて設けられている。第2の配線12を含む第2の絶縁膜9の上面および第1、第2の絶縁膜5、9の側面はエポキシ系樹脂等からなる封止膜14によって覆われている。これにより、第1、第2の絶縁膜5、9間で剥離が生じにくいようにすることができる。

(もっと読む)

半導体装置

【課題】金属配線層の信頼性を向上出来る半導体装置を提供すること。

【解決手段】半導体装置1は、層間絶縁膜7と、前記層間絶縁膜7に形成された溝12内の底面及び側面上に形成されたバリアメタル層8と、前記バリアメタル層8上に形成され且つ上面が前記溝12の開口部上面より低く、前記溝12内の一部を埋め込む導電層9と、前記導電層9上及び前記溝12開口部における前記バリアメタル層8の側面上に、前記層間絶縁膜7よりも誘電率の高い材料により形成された第1絶縁膜10とを具備する。

(もっと読む)

表面疎水化用組成物、表面疎水化方法、および半導体装置

【課題】層の表面をより簡便にかつ効果的に疎水化することができ、かつ、層のより深い領域を疎水化することができる表面疎水化用組成物、表面疎水化方法、および該表面疎水化方法が施された半導体装置を提供する。

【解決手段】表面疎水化用組成物は、(A)下記一般式(1)で表される化合物および下記一般式(2)で表される化合物の群から選ばれた少なくとも1種の化合物と、(B)沸点が30〜350℃である溶媒とを含む。

【化1】

・・・・・(1)

【化2】

・・・・・(2)

(もっと読む)

半導体装置、集積回路、及び電子機器

【課題】複数のデバイス層を積層配置してなる半導体装置におけるデバイス層間の接続構造をチップ面積の増大や製造工程の複雑化を招くことなく実現し、好ましくは前記層間接続の信頼性の向上も実現した半導体装置を提供する。

【解決手段】デバイス層101,102が積層され、第2のデバイス層102は、表面に複数の微細孔G1を有する起点部層211と、起点部層211を起点として形成された略単結晶粒を含む半導体膜を用いて形成されたトランジスタQ12(デバイス)を有するデバイス形成層212とを備えており、トランジスタQ12等を構成する結晶化半導体膜201,202の側端面に絶縁材料からなるサイドウォール201s、202sが設けられており、トランジスタ(デバイス)Q11とトランジスタQ12とを接続するコンタクト部C5は、結晶化半導体膜201,202の間の領域に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、接合リーク電流の発生を抑制し、トランジスタ特性を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の表面部分において選択的に形成された溝40と、溝の上部の内側面に形成された側壁絶縁膜60と、側壁絶縁膜が形成された溝を埋め込むように形成された絶縁膜50及び80と、溝に埋め込まれた側壁絶縁膜及び絶縁膜によって分離される素子領域100において、半導体基板上にゲート絶縁膜130を介して形成されたゲート電極140と、ゲート電極の側面に形成されたゲート電極側壁160と、半導体基板の表面部分において、ゲート電極の下方に位置するチャネル領域230の両側に、溝に隣接するようにそれぞれ形成されたソース領域及びドレイン領域150及び170とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ビア・配線間の重ね合わせがずれた場合にもTDDBを抑制できる半導体装置およびその製造方法を提供する。

【解決手段】順次積層された絶縁膜1,2内に形成された溝11内には、バリアメタル3およびCuからなる配線4が埋め込まれている。配線4上にはメタルキャップ9が配置され、メタルキャップ9上には、絶縁膜5,6が順次積層されている。絶縁膜5,6内に形成された溝14内には、バリアメタル7およびCuからなる配線8が埋め込まれている。この絶縁膜5は、Cuが拡散されないものとする。バリアメタル7は、ビア・配線間の重ね合わせにおいて位置ずれが生じた場合にも、メタルキャップ9には接触するが配線層21の絶縁膜2やバリアメタル3には接触しないように形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】耐湿性を低下させずに、コレクタ電極とベース電極パッド間の寄生容量(帰還容量)を小さくし、高周波特性を劣化させないようにする。

【解決手段】低抵抗のN型半導体基板101の上に絶縁層102を形成し、バイポーラトランジスタのベース107,エミッタ108上に表面保護膜104を形成する。この表面保護膜104の開口はボンディングパッド103よりも大きくし、ボンディングパッド103の側壁には側壁保護膜106を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極を備えた半導体装置を積層した3次元半導体装置において、貫通電極の抵抗と容量が大きく、高速データ転送ができないという問題がある。

【解決手段】貫通電極をゲート電極の第1導電膜をマスクとして形成する。第1導電膜の上に成膜されたゲート電極の第2導電膜を、貫通電極の配線電極とする。ゲート電極形成工程において貫通電極を形成することで高融点金属およびその化合物が使用でき、低抵抗化が図れる。さらに貫通電極からの配線工程をゲート電極からの配線工程と共有化する等、半導体標準プロセスに適合させることで工程を短縮することができる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極にドライエッチングが困難な低抵抗材料を用いて、自己整合コンタクト構造を有する半導体装置を製造する。

【解決手段】シリコン基板上に、ゲート絶縁膜、ポリシリコン膜および第1絶縁膜を形成する工程と、第1絶縁膜をパターニングする工程と、金属膜を形成する工程と、ポリシリコン膜と金属膜と反応させてシリサイド層を形成する工程と、未反応の金属膜の除去後に、第2絶縁膜を形成する工程と、第1絶縁膜が露出し且つ第1絶縁膜で覆われていない領域に第2絶縁膜が残るように第2絶縁膜を除去する工程と、第1絶縁膜の除去後に、第2絶縁膜をマスクに用いてエッチングを行い、上層側にシリサイド層および下層側にポリシリコン層を有するゲート電極を形成する工程と、ゲート電極の側面に第3絶縁膜を形成する工程と、層間絶縁膜を形成し、コンタクトホールを形成する工程とを有する半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】裏面に接続する配線構造を低コストな工程で形成することが可能な半導体装置の製造方法およびその半導体装置を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、シリコン基板100の素子領域101が形成されている表面側からスクライブエリアに対してハーフカットのダイシングを行って、シリコン基板100に溝を形成するハーフカット工程と、溝のカット面に保護膜を形成する保護膜形成工程と、シリコン基板100の表面側に金属膜を形成する金属膜形成工程と、金属膜をパターニングして配線構造を形成する配線構造形成工程と、シリコン基板100の裏面をグランディングして配線構造を裏面に露出させるグランディング工程とを備えている。

(もっと読む)

半導体素子の微細パターン形成方法

【課題】 CD制御を可能にし且つセルのライン間のスペースを異にするための半導体素子の微細パターン形成方法の提供。

【解決手段】 半導体基板の上部に第1酸化膜、下部反射防止膜及び第1感光膜パターンを形成した後、前記第1感光膜パターンをマスクとして前記下部反射防止膜及び前記第1酸化膜をエッチングする段階と、前記第1感光膜パターン及び前記下部反射防止膜を除去した後、全体構造の上部に窒化膜を蒸着する段階と、前記窒化膜を全面エッチングして前記第1酸化膜の側壁にスペーサを形成する段階と、全体構造の上部に第2酸化膜を蒸着した後、研磨して平坦化させる段階と、全体構造の上部に第2感光膜パターンを形成した後、前記第2感光膜パターンをマスクとして前記窒化膜を除去して酸化膜パターンを形成する段階とを含む、半導体素子の微細パターン形成方法を提供する。

(もっと読む)

81 - 100 / 133

[ Back to top ]