Fターム[5F033TT06]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の構造、形状 (4,088) | 側壁絶縁膜 (2,038)

Fターム[5F033TT06]の下位に属するFターム

コンタクトホールの側壁 (799)

電極、配線の側壁 (1,106)

Fターム[5F033TT06]に分類される特許

121 - 133 / 133

表面疎水化用組成物、表面疎水化方法、半導体装置およびその製造方法

【課題】 半導体装置等の電子デバイスに用いられる絶縁層の表面疎水化用組成物、表面疎水化方法、ならびに半導体装置およびその製造方法を得る。

【解決手段】 1,1,3,3−テトラメトキシジシラシクロブタン、ビス(ジメチルメトキシシリル)メタン、1,3−ジメトキシ−1,1,3,3−テトラメチルジシロキサンなどのシラン化合物と有機溶媒とからなる組成物。

(もっと読む)

表面疎水化用組成物、表面疎水化方法、半導体装置およびその製造方法

【課題】 半導体装置等の電子デバイスに用いられるエッチング/アッシング後のシロキサン系絶縁層のダメージを修復することを目的とした表面疎水化用組成物、表面疎水化方法、ならびに半導体装置およびその製造方法を得る。

【解決手段】 (A)ポリシランと、(B)有機溶媒を含む、表面疎水化用組成物。(A)下記一般式(1)で表わされる化合物の群から選ばれた少なくとも1種のポリシランと、(B)有機溶媒を含む、表面疎水化用組成物、および該組成物を用いた表面疎水化方法、半導体装置。

[式中、R1,R2は水素原子、アルキル基、ビニル基、アリル基またはフェニル基を示す(ただし、R1,R2のうち水素原子は1個または0個である)。]

(もっと読む)

表面疎水化用組成物、表面疎水化方法、半導体装置およびその製造方法

【課題】 半導体装置等の電子デバイスに用いられるエッチング/アッシング後のシロキサン系絶縁層のダメージを修復することを目的とした表面疎水化用組成物、表面疎水化方法、ならびに半導体装置およびその製造方法を得る。

【解決手段】 マロン酸ビス(トリメチルシリル)、1,2−ビス(トリメチルシロキシ)エタン、テトラキス(トリメチルシロキシ)チタニウムなどのシラン化合物と有機溶媒とからなる組成物。

(もっと読む)

半導体装置およびその製造方法

【課題】 貫通電極を有する半導体装置において、信頼性の高い貫通電極を、容易に低コストで形成する。

【解決手段】 第1面に第1の絶縁膜2と電極パッド3とが形成された半導体ウエハ1に対し、電極パッド3の直下にて半導体ウエハ1に貫通孔を形成し、この貫通孔の内壁、および半導体ウエハ1の第2面に第2の絶縁膜5を形成する。この第2の絶縁膜5の形成においては、半導体ウエハ1を陰極とする電着を用いる。第2の絶縁膜5の形成後は、この第2の絶縁膜をマスクとして第1の絶縁膜2をエッチングし、電極パッド3裏面を露出させ、上記貫通孔内に貫通電極となる導電層6を形成する。

(もっと読む)

半導体装置

【課題】絶縁膜に形成された凹部に保護膜を形成することで、凹部の側壁が後退することなく水素プラズマによる凹部底部のクリーニングを可能とする。

【解決手段】有機絶縁膜(低誘電率有機膜17,19)を備えた絶縁膜16に形成された凹部23の側壁に、窒素と、前記低誘電率有機膜17,19から解離された炭素との化合物からなる保護膜31が形成されているものである。

(もっと読む)

半導体装置

【課題】 半導体装置中のクラックの伝播を抑制し、他の領域に影響を与えないようにする。

【解決手段】 シリコン基板101上に設けられたSiCN膜105およびSiOC膜107を貫通する凹部の側面を覆う界面補強膜115を設ける。界面補強膜115はSiOC膜113と連続一体に形成され、エアギャップ117を有する。

(もっと読む)

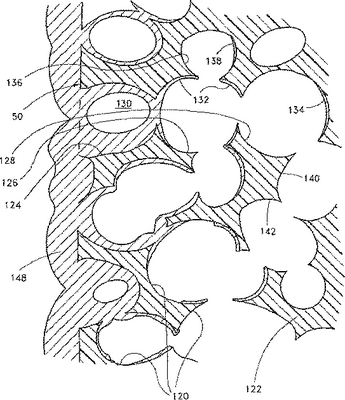

シーリング多孔質構造

集積回路中のデュアルダマシン(dual damascene)構造、特に多孔質材料中に形成された開口部のコンフォーマリティの裏張り(lining)のための方法及び構造が提供される。トレンチ(trench)及びコンタクトビア(contact via)が絶縁層中に形成される。これらのトレンチ及びビアの側壁上のポアがブロックされ、次いでこの構造は、所望のライニング材料の単層を形成するために交互に化学物質に曝される。例示的なプロセスフローにおいて、シーリング層の化学または物理気相成長法(chemical or physical vapor deposition)(CVDまたはPVD)により、不完全なコンフォーマリティに起因してポアをブロックする。交互のプロセスも、自己飽和(self−saturating)、自己制御(self−limiting)原子層堆積(atomic layer deposition)(ALD)プロセスと比較して減少されたコンフォーマリティを達成するようなパルス間隔及びパルス幅の選択によって構成され得る。なお別の構成において、異方性多孔質構造を有する層が、上部表面を選択的に溶融することによってシールされ得る。次いで、自己制御、自己飽和原子層堆積(ALD)反応により、有意にポアを充填することなくブロッキングが行われる。  (もっと読む)

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 半導体集積回路チップに基板貫通孔を短時間に効率よく形成する。

【解決手段】 チップ表面に拡散層15を形成して配線14と接続させ、貫通孔底部の中心が拡散層15と配線14との接続部分の中心にくるようにし、且つ貫通孔底部径が配線14と拡散層15との接合部分の径と同一かそれよりもやや大きな径になるように径を制御しながら、半導体集積回路チップ裏面13よりドライエッチングを開始して、貫通孔16を形成する。本発明の半導体チップ構造では、ドライエッチングの際に使用するエッチングガスはシリコンを選択的にエッチングするガスだけでよい。従ってエッチング工程の途中でエッチングガスを他の種類のエッチングガスに交換する必要がなく、基板貫通孔を短時間に効率よく形成することができる。

(もっと読む)

パターン形成方法を含む半導体装置の製造方法

【課題】 本発明は半導体装置の製造工程において、レジストなどのマスクパターンを用いる際に発生する反応生成物等のレジスト等への不均一な付着によるパターン形状等の不良を生じさせず、また、寸法精度が良好な微細パターンの形成方法を提供することを目的とする。

【解決手段】 パターン形成方法を含む半導体装置の製造方法として、第1の薄膜の側壁に第2の薄膜を形成し、その側壁に形成された第2の薄膜の先端部が不均一にならないように、平坦化法により、精度良くエッチバックして揃える。

(もっと読む)

半導体チップの製造方法および半導体装置の製造方法

【課題】 貫通電極用の貫通孔の形成時間を短縮化することで生産性を向上させた半導体チップの製造方法を提供する。

【解決手段】 まず、第1の絶縁膜3をマスク部材としてシリコン基板1の上面側に第1のトレンチ7aを例えばボッシュプロセスを用いて形成する。次に、第2の絶縁膜5をマスク部材としてシリコン基板1の裏面側に、第1のトレンチ7aに連通する第2のトレンチ7bを同じくボッシュプロセスを用いて形成する。そして、これにより形成された貫通孔8内に絶縁膜を形成した後、その貫通孔8内に導電性材料を充填して貫通電極2を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 寄生容量の増加を抑制しつつ、所望のゲート耐圧を有するパワーMISFETを製造できる技術を提供する。

【解決手段】 基板上に多結晶シリコン膜を堆積し、その多結晶シリコン膜で溝部7、8を埋め込んだ後、その多結晶シリコン膜をパターニングすることにより、活性セル領域においては溝部7内にてゲート電極11を形成し、ゲート配線領域においては溝部8内を埋め込み、一部が溝部8内から連続して溝部8の外部に延在し、ゲート電極11と電気的に接続するゲート引き出し電極12を形成し、溝部8外のゲート引き出し電極12には、ゲート引き出し電極12の端部から延在するスリット14を形成する。その後、基板上に酸化シリコン膜19およびBPSG膜20を堆積する。

(もっと読む)

半導体装置及びその製造方法

【課題】 多孔質絶縁膜を含む層間絶縁膜の誘電率を実効的に低減させ、微細で高信頼性のダマシン配線を有する半導体装置の実用化を容易にする。

【解決手段】 下層配線1上に多孔質の第1低誘電率膜2bを含む第1層間絶縁膜2が形成され、第1層間絶縁膜2に設けられたビアホール3内にその側壁に設けられた第1側壁保護膜4を介して第1バリア層5およびビアプラグ6が形成される。同様に、多孔質の第2低誘電率膜7bを含む第2層間絶縁膜7のトレンチ8内にその側壁に設けられた第2側壁保護膜9を介して第2バリア層10および上層配線11が形成される。ここで、第1側壁保護膜4および第2側壁保護膜9は多孔質の低誘電率膜で成り、その空孔の含有率は30%以下であり、空孔の寸法は2nm以下である。

(もっと読む)

低静電容量配線のための調節可能な自己整合型エアーギャップ誘電体

【課題】 低静電容量配線のための調節可能な自己整合型エアーギャップ誘電体を形成すること。

【解決手段】 調節可能で自己整合型の低静電容量集積回路のエアーギャップ構造は、相互接続層上で第二相互接続部に隣接する第一相互接続部と、該第一相互接続部及び該第二相互接続部の隣接する側部に沿って形成されたスペーサと、該第一相互接続部と該第二相互接続部との間に形成されたエアーギャップとを含む。エアーギャップは、第一相互接続部及び第二相互接続部の少なくとも一方の上面より上方で、かつ、該第一相互接続部及び該第二相互接続部の少なくとも一方の下面より下方に延び、スペーサ間の距離が該エアーギャップの幅を定める。エアーギャップは、第一相互接続部及び第二相互接続部の隣接する側部に自己整合する。

(もっと読む)

121 - 133 / 133

[ Back to top ]