半導体装置およびその製造方法

【課題】ビア・配線間の重ね合わせがずれた場合にもTDDBを抑制できる半導体装置およびその製造方法を提供する。

【解決手段】順次積層された絶縁膜1,2内に形成された溝11内には、バリアメタル3およびCuからなる配線4が埋め込まれている。配線4上にはメタルキャップ9が配置され、メタルキャップ9上には、絶縁膜5,6が順次積層されている。絶縁膜5,6内に形成された溝14内には、バリアメタル7およびCuからなる配線8が埋め込まれている。この絶縁膜5は、Cuが拡散されないものとする。バリアメタル7は、ビア・配線間の重ね合わせにおいて位置ずれが生じた場合にも、メタルキャップ9には接触するが配線層21の絶縁膜2やバリアメタル3には接触しないように形成される。

【解決手段】順次積層された絶縁膜1,2内に形成された溝11内には、バリアメタル3およびCuからなる配線4が埋め込まれている。配線4上にはメタルキャップ9が配置され、メタルキャップ9上には、絶縁膜5,6が順次積層されている。絶縁膜5,6内に形成された溝14内には、バリアメタル7およびCuからなる配線8が埋め込まれている。この絶縁膜5は、Cuが拡散されないものとする。バリアメタル7は、ビア・配線間の重ね合わせにおいて位置ずれが生じた場合にも、メタルキャップ9には接触するが配線層21の絶縁膜2やバリアメタル3には接触しないように形成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関し、特に、TDDB(Time Dependent Dielectric Breakdown:経時的絶縁膜破壊)を低減するための技術に関する。

【背景技術】

【0002】

半導体装置は集積性や高速性を追い求め、どんどん微細化が進んでいる。その一部である配線工程においても微細化が進んでいる。ところが微細化に従って信頼性の問題が深刻なものとなってきた。それら信頼性問題の一つに配線間のTDDBがある。配線間TDDBは通常配線間の距離に依存している。つまり微細化に伴い配線間の距離、または配線とビアとの距離が小さくなり、それにより配線間TDDBの問題も深刻化しているのである。微細化を進めるにはこの問題を解決する必要がある。

【0003】

一般に、配線間TDDBは、界面をメタルが拡散することにより生じると考えられており、また、電界強度に依存することが実験的に分かっている。従って、メタルが拡散すると考えられる界面上の距離(分離寸法)を大きくすることにより、配線間TDDBを抑制できると考えられる。

【0004】

ところで45nmノード世代より適用されると思われる技術にメタルキャップの技術がある。これは信頼性の問題の一つであるエレクトロマイグレーション(EM)の耐性を向上させる技術として注目を集めている。メタルキャップは無電界メッキ技術を用いることで、Cu配線上に選択的に形成されるメタルである。このメタルキャップはCuのバリアとしての役割を持っているだけでなく、これまで用いられてきた絶縁膜のバリアに比べてCuへの密着性が高いので、EMの耐性を向上させることができる。Cu配線やメタルキャップを用いた半導体装置は、例えば、特許文献1〜5に開示されている。

【0005】

【特許文献1】特開2004−152956号公報

【特許文献2】特開2004−015028号公報

【特許文献3】特開2002−151518号公報

【特許文献4】特開2002−118111号公報

【特許文献5】特開2001−230220号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

従来の半導体装置の構造においては、隣り合う2個の配線のうち一方配線の上層にビアが形成されているときに、一方配線とビアとの重ね合わせがずれると、ビア・他方配線間の分離寸法が、一方配線・他方配線間の分離寸法より小さくなる。このような場合には、一方配線・他方配線間のTDDBは、一方配線・他方配線間の分離寸法ではなくビア・他方配線間の分離寸法で決定されることとなる。従って、ビア・一方配線間の重ね合わせのずれ量が大きくなるにつれてTDDBが進行するという問題点があった。

【0007】

本発明は、以上の問題点を解決するためになされたものであり、ビア・配線間の重ね合わせがずれた場合にもTDDBを抑制できる半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明に係る半導体装置の製造方法は、第1絶縁膜に第1バリア層および第1配線を順次埋め込む工程と、第1配線上のみにメタルキャップを形成するメタルキャップ形成工程と、第1配線を構成する所定の金属に対してバリア性を有する第2絶縁膜を第1絶縁膜上およびメタルキャップ上に形成する工程と、第2絶縁膜にエッチングを行うことにより溝を形成する溝形成工程と、溝に第2バリア層および第2配線を順次埋め込む工程とを備え、溝形成工程において、エッチングは、位置ずれが生じた場合には第1バリア層および第1絶縁膜を露出させず且つメタルキャップの側面を部分的に露出させるような条件で行われる。

【発明の効果】

【0009】

本発明に係る半導体装置の製造方法は、第1絶縁膜に第1バリア層および第1配線を順次埋め込む工程と、第1配線上のみにメタルキャップを形成するメタルキャップ形成工程と、第1配線を構成する所定の金属に対してバリア性を有する第2絶縁膜を第1絶縁膜上およびメタルキャップ上に形成する工程と、第2絶縁膜にエッチングを行うことにより溝を形成する溝形成工程と、溝に第2バリア層および第2配線を順次埋め込む工程とを備え、溝形成工程において、エッチングは、位置ずれが生じた場合には第1バリア層および第1絶縁膜を露出させず且つメタルキャップの側面を部分的に露出させるような条件で行われる。従って、位置ずれが生じた場合においても、隣り合う第1配線間のTDDBを抑制することができる。

【発明を実施するための最良の形態】

【0010】

本発明に係る半導体装置の製造方法は、第1配線上に第2配線を重ね合わせるときに位置ずれが生じた場合においても、隣り合う第1配線間で分離寸法が小さくならないような構造が形成されることを特徴とする。以下、位置ずれが生じた場合の本発明の各実施の形態について、図面を用いて詳細に説明する。なお、一部の図面においては、図示の都合上、部材の幅等を部分的に異ならせている。

【0011】

<実施の形態1>

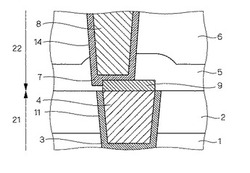

図1は、実施の形態1に係る半導体装置の構造を示す概略断面図である。

【0012】

図1に示されるように、順次積層された絶縁膜1,2内に形成された溝11内には、バリアメタル3およびCuからなる配線4が埋め込まれている(配線層21)。

【0013】

また、配線4上にはメタルキャップ9が配置され、メタルキャップ9上には、絶縁膜5,6が順次積層されている。絶縁膜5,6内に形成された溝14内には、バリアメタル7およびCuからなる配線8が埋め込まれている(配線層22)。この絶縁膜5は、Cuが拡散されない(Cuに対してバリア性を有する)ものとする。以下では、このような絶縁膜をライナー膜とも呼ぶ。

【0014】

図1に示されるように、本実施の形態に係る半導体装置は、配線8が配線4に対してずれて重ね合わせられた場合に、バリアメタル7が、メタルキャップ9には接するが絶縁膜2やバリアメタル3には接しないように形成されていることを特徴とする。このような溝14を形成するように絶縁膜5のエッチング量を調節することにより、図15を用いて後述するように、配線8が配線4に対してずれて重ね合わせられた場合においても、隣り合う配線4間で分離寸法が小さくならないようにすることが可能となる。なお、重ね合わせにおいて位置ずれが生じない場合には、溝14を形成するための絶縁膜5のエッチングは、メタルキャップ9上の領域のみで行われるので、メタルキャップ9で止まることになる。従って、このような場合には、エッチング量を調節しなくても、バリアメタル7が絶縁膜2やバリアメタル3に接することはない。

【0015】

図2〜11は、図1の半導体装置の製造方法を示す断面図である。Cu配線を形成する手法としてはさまざまな手法があるが、ここでは、レジストパターンをマスクに用いてビアファーストのデュアルダマシン法で形成する手法を例に説明する。なお、本発明は、ビアファーストのデュアルダマシン法に限らず、シングルダマシン法や、トレンチファーストのデュアルダマシン法、ハードマスクを用いる手法等へも適用可能である。

【0016】

まず、図2〜5を用いて、ダマシン法により配線層21を形成する工程を説明する。図2〜5に示されるように、配線層21に形成される配線4は、ビア部を有さず配線部のみからなるものとする。

【0017】

まず、図2に示されるように、下層配線10上に、下層配線10を構成する金属に対してバリア性を有し且つ後の工程においてエッチングストッパーとして機能する絶縁膜1を形成する。絶縁膜1としては、SiNや、SiON、SiCN、SiCO等を用いる。そして、絶縁膜1上に、絶縁膜2を形成する。絶縁膜2としては、シリコン酸化膜や、SiOF、SiOC、有機膜等を用いる。なお、絶縁膜2の中央部には、後の工程で配線4のエッチングストッパーとして機能する層を必要に応じて形成してもよい。

【0018】

次に、図3に示されるように、ダマシン法を用いて、絶縁膜2を開口させることにより、溝11を形成する。この溝11は、次のような工程で形成される。

【0019】

すなわち、まず、通常の写真製版プロセスにより配線部用のレジストパターン(図示しない)を形成する(上述したように、配線4はビア部を有さず配線部のみからなるので、このレジストパターンは配線4全体に対応している)。次に、このレジストパターンをマスクとして、絶縁膜2を、配線部の高さ(すなわち配線4の高さ)分だけ加工することにより、溝11を形成する。次に、レジストパターンを、アッシング法や薬液を用いたウェットエッチング法で除去する。

【0020】

次に、図4に示されるように、通常のダマシンプロセスに従い、溝11へのメタルの埋め込みを行う。この埋め込みは、次のような工程で行われる。

【0021】

すなわち、まず、溝11内に、例えばTaやTaNを用いて、拡散バリアとなるバリアメタル3およびメッキ法でのシードとなるシード層を、スパッタ法により形成する。次に、メッキ法によりCuを埋め込む。次に、CMPにより、余分なCuおよびバリアメタルを除去する。これにより、溝11内にバリアメタル3および配線4が形成される。

【0022】

次に、図5に示されるように、CoWPやCoWB、NiWP等を用いて、無電解メッキ法により、配線4上にメタルキャップ9を形成する。メタルキャップ9は、配線4のCu上に選択的に成長するので、配線4上にのみ形成される。これにより、配線層21が形成される。

【0023】

次に、図6〜11を用いて、ダマシン法により配線層22を形成する工程を説明する。図6〜11に示されるように、配線層22に形成される配線8は、ビア部および配線部を有するものとする。

【0024】

まず、図6に示されるように、メタルキャップ9、バリアメタル3、および絶縁膜2上に、Cuに対してバリア性を有する絶縁膜5を形成する。絶縁膜5としては、SiNや、SiON、SiCN、SiCO等を用いる。この絶縁膜5は、CVD等を用いて、コンフォーマルに(すなわち、メタルキャップ9等の下方の形状に忠実に成長するように)形成させる。これにより、絶縁膜5は、メタルキャップ9上方の領域が部分的に盛り上がった形状となる。

【0025】

次に、図7に示されるように、絶縁膜5上に、絶縁膜6を形成する。絶縁膜6としては、シリコン酸化膜や、SiOF、SiOC、有機膜等を用いる。この絶縁膜6は、メタルキャップ9上方の領域が部分的に盛り上がった形状となるので、CMP法により平坦化する。

【0026】

次に、図8〜10に示されるように、絶縁膜6を開口させることにより、溝14を形成する。この溝14は、次のような工程で形成される。

【0027】

すなわち、まず、図8に示されるように、通常の写真製版プロセスによりビア部用のレジストパターン12を形成する。次に、このレジストパターン12をマスクとして、絶縁膜6を加工することにより、溝14を形成する。この加工は、通常、絶縁膜5をエッチングストッパーとしたドライエッチング法により行われる。次に、レジストパターン12を、アッシング法や薬液を用いたウェットエッチング法で除去する。次に、図9に示されるように、通常の写真製版プロセスにより配線部用のレジストパターン13を形成する。次に、このレジストパターン13をマスクとして、絶縁膜6を、配線部の高さ分だけ加工することにより、溝14を拡げる。次に、レジストパターン13を、アッシング法や薬液を用いたウェットエッチング法で除去する。

【0028】

次に、図10に示されるように、絶縁膜5をドライエッチング法で加工することにより、溝14を部分的に深くする。これにより、ビア部および配線部を有する(配線8用の)溝14が完成する。このドライエッチングは、図13〜14を用いて後述するような手法でエッチング量を調節することにより、メタルキャップ9の側面が部分的に露出し絶縁膜2およびバリアメタル3が露出しないように行う。

【0029】

次に、図11に示されるように、通常のダマシンプロセスに従い、溝14へのメタルの埋め込みを行う。この埋め込みは、次のような工程で行われる。

【0030】

すなわち、まず、溝14内に、例えばTaやTaNを用いて、拡散バリアとなるバリアメタル7およびメッキ法でのシードとなるシード層を、スパッタ法により形成する。次に、メッキ法によりCuを埋め込む。次に、CMPにより、余分なCuおよびバリアメタルを除去する。これにより、溝14内にバリアメタル7および配線8が形成される。次に、CoWPやCoWB、NiWP等を用いて、無電解メッキ法により、配線8上にメタルキャップ15を形成する。メタルキャップ15は、配線8のCu上に選択的に成長するので、配線8上にのみ形成される。これにより、配線層22が形成される。

【0031】

以上の工程を繰り返すことにより、所望の配線層数を有する半導体装置が形成される。

【0032】

なお、上述においては、下層の配線層21には配線部のみを有する配線4をを埋め込み上層の配線層22にはビア部および配線部を有する配線8埋め込む場合について説明したが、あるいは、配線8と同様に、配線4にもビア部を設けてもよい。

【0033】

また、本明細書では、配線4を第1配線、バリアメタル3を第1バリア層、絶縁膜2を第1絶縁膜、配線8を第2配線、バリアメタル7を第2バリア層、絶縁膜5を第2絶縁膜、絶縁膜6を第3絶縁膜とそれぞれ呼ぶ。また、第1配線(配線4)と第1バリア層(バリアメタル3)とをまとめて第1配線部材と呼ぶとともに、第2配線(配線8)と第2バリア層(バリアメタル7)とをまとめて第2配線部材と呼ぶ。

【0034】

図12は、Cuに対してバリア性を有する絶縁膜5を形成することによる有効性を示すために、図1において絶縁膜5を形成せずに絶縁膜6を形成した場合の構造を比較用に示す断面図である。図12(a)においては、点線で示されるように、メタルキャップ9は配線4上に選択的に成長するので、メタルキャップ9と配線4とバリアメタル3との3種類の材料が互いに接する境界線(図12においては点)が存在する。従って、図12(b)に示されるように、この境界線から絶縁膜6にCuが拡散してしまう。一方、本実施の形態に係る半導体装置においては、図1等に示されるように、この境界線にはCuに対してバリア性を有する絶縁膜5が形成されるので、絶縁膜5にCuが拡散することはない。

【0035】

次に、図13〜14を用いて、メタルキャップ9の側面が部分的に露出し絶縁膜2およびバリアメタル3が露出しないようにエッチング量を調節する手法について説明する。以下では、65nmノードプロセスを例にとり説明する。また、本実施の形態においては、メタルキャップ9は、配線4上で、反応性を一定に保つことにより断面が矩形状となるように成長するものとする。

【0036】

図13〜14に示されるように、メタルキャップ9の膜厚が20nmであり、絶縁膜5(盛り上がった領域の端部すなわち表面が平らでない部分を除く)の膜厚が50nmであり、配線4,8間の重ね合わせのずれ量が30nmであるとする(この30nmのずれ量は、65nmノードプロセスにおいては十分に可能な値である)。図13には、重ね合わせのずれ量が0nmである場合が示されており、図14には、重ね合わせのずれ量が30nmである(配線8が配線4に対して右方向に30nmずれている)場合が示されている。

【0037】

65nmノードプロセスにおいては、配線幅、分離幅(配線間隔)、およびビア径は、いずれも100nmに設定される場合が多い。しかし、図13〜14に示されるように、実際の構造においては配線部材およびビア部材はいずれもテーパー形状となるので、それぞれの幅(図における横方向の長さ)は、第1配線部材の上面では110nm程度となり、第2配線部材の底面では90nm程度となる。また、配線4,8に隣接するようにバリアメタル3,7がそれぞれ配置されているが、ここでは、バリアメタル3,7の膜厚を10nmとする(一般的なバリアメタルの膜厚は5〜10nm)。

【0038】

上述したように、メタルキャップ9は、配線4上にのみ形成され断面が矩形状であるので、メタルキャップ9の幅は、(第1配線部材の上面の幅)−(バリアメタル3の膜厚)×2=110−10×2=90nmとなる。図13に示されるように、重ね合わせのずれ量が0nmである場合には、メタルキャップ9の幅が90nmで第2配線部材の底面の幅が90nmであるので、メタルキャップ9の端と第2配線部材の底面の端とが横方向で同じ位置となる。

【0039】

図13において、メタルキャップ9の膜厚を表す長さa=20nmであり、重ね合わせが最も大きくずれた位置とメタルキャップ9の右端との距離d=30nmである。また、上述したように、絶縁膜5はコンフォーマルに形成されているので、長さd=30nmずれた位置における絶縁膜5の最上部とメタルキャップ9の右端との距離c=50nmとなる。従って、重ね合わせが30nmずれた位置(言い換えれば重ね合わせが最も大きくずれた位置)における絶縁膜5の膜厚は、b+a=√(c2−d2)+a=√(502−302)+20=40+20=60nmとなる。

【0040】

上述したように、絶縁膜5(盛り上がった領域の端部すなわち表面が平らでない部分を除く)の膜厚は50nmであるので、メタルキャップ9が露出するように溝14を形成するときには、絶縁膜5を少なくとも50nm分はエッチングする必要がある。また、ばらつきを考慮して10%のオーバーエッチングを行うとすると、55nm分エッチングすることとなる。しかし、上述したように、重ね合わせが最も大きくずれた位置であっても、絶縁膜5の膜厚は60nmであるので、このようなオーバーエッチングを行った場合においても、5nm分の絶縁膜5が残存することより、絶縁膜2およびバリアメタル3は露出しない。なお、図14に示されるように、重ね合わせのずれ量が0nmより大きく30nmより小さい場合においても、絶縁膜5は、60nmより大きい(且つ50+20=70nmより小さい)膜厚を有するので、オーバーエッチングを行った場合においても、絶縁膜2およびバリアメタル3は露出しない。このような条件を満たすようにエッチング量を調節することにより、絶縁膜2およびバリアメタル3が露出せずメタルキャップ9の側面が部分的に露出するようなエッチングを行うことが可能となる。

【0041】

図15は、本実施の形態に係る半導体装置の有効性を示す断面図である。図15に示されるように、本実施の形態に係る半導体装置においては、バリアメタル7が絶縁膜2およびバリアメタル3に接さない。上述したように、配線間TDDBは、界面をCuが拡散することにより生じると考えられるので、配線間TDDBを抑制するためには、Cuが拡散すると考えられる界面上の距離(分離寸法)を小さくする必要がある。図15においては、左側の配線4と配線8との分離寸法は、互いに隣り合う2個のバリアメタル3間の距離を表す長さe、バリアメタル3の膜厚を表す長さf、およびエッチング後に残存する絶縁膜5の膜厚を表す長さgを用いて、長さ(e+f+g)となる。一方、左側の配線4と右側の配線4との分離寸法は、長さeであるので、配線8が配線4に対してずれて重ね合わせられた場合においても、隣り合う配線4間のTDDBは、より小さい方の長さeに依存する。従って、位置ずれが生じた場合にも、配線間TDDBが大きくなることはない。

【0042】

図16〜19は、バリアメタル7が絶縁膜2およびバリアメタル3に接触するように形成された半導体装置を比較用に示す断面図である。図16〜19においては、配線8が配線4に対して左方向にずれている場合が示されている。図16〜17はメタルキャップ9が配置されない場合を示しており、図18〜19はメタルキャップ9が配置された場合を示している。また、図17,19は、それぞれ、図16,18において第1配線部材と第2配線部材との境界付近を拡大するとともに隣り合う第2配線部材を追加し示したものである。

【0043】

図17,19に示されるように、バリアメタル7が絶縁膜2およびバリアメタル3に接するように形成されている場合においては、左側の配線4と配線8との分離寸法は長さhとなる。長さhは、左側の配線4と右側の配線4との分離寸法(図15の長さeに相当)より小さいので、隣り合う配線4間のTDDBは、長さhに依存する。従って、位置ずれが生じた場合には、配線間TDDBが大きくなる。

【0044】

図20には、重ね合わせのずれ量を20nm,25nm,30nm,35nmと変化させ且つバリアメタル7・メタルキャップ9間における絶縁膜5(盛り上がった領域の端部すなわち表面が平らでない部分を除く)の膜厚(ライナー膜厚)を70nm,60nm,50nm,40nmと変化させた場合において、エッチングの後に残存する絶縁膜5の膜厚(エッチングの前の絶縁膜5の膜厚−必要とされるエッチング量)が示されている。図20(a)〜(d)は、それぞれ、オーバーエッチング(OE)量を10%または20%とし且つメタルキャップ9の膜厚を20nmまたは30nmとした場合に対応している。図20において、エッチングの後に残存する絶縁膜5の膜厚が正の値となるような条件を選択することにより、絶縁膜2およびバリアメタル3が露出せずメタルキャップ9の側面が部分的に露出するようなエッチングを行うことが可能となる。

【0045】

なお、微細化が進んだ場合には、図20の各パラメータを同率にシュリンクしていくことにより、適切な条件を選択することが可能となる。例えば、図20(a)では、0.1倍にシュリンクすることにより、オーバーエッチング量が10%、メタルキャップ9の膜厚が2nm、重ね合わせのずれ量が3nm、ライナー膜厚が5nmという条件においては、エッチングの後に残存する絶縁膜5の膜厚は0.5nmとなる。

【0046】

このように、本実施の形態においては、配線4,8の重ね合わせ(配線4の配線部と配線8のビア部との重ね合わせ)において位置ずれが生じた場合においても、配線4,8間の分離寸法は、図17,19の長さhではなく図15の長さ(e+f+g)で決定するので、隣り合う配線4間のTDDBは、図15の長さeに依存する。従って、ビア・配線間の重ね合わせにおいて位置ずれが生じた場合にも、隣り合う配線4間のTDDBを抑制することができる。

【0047】

なお、上述においては、配線4がCuからなり且つ絶縁膜5がCuに対してバリア性を有する場合について説明したが、Cuに限らず、他の金属であってもよい。

【0048】

また、上述においては、図1に示されるような構造を、図13〜14に示されるような手法を用いてエッチング量を調節することにより形成する場合について説明したが、図13〜14に示されるような手法に限らず、あるいは、他の既存の手法を用いてエッチング量を調節してもよい。

【0049】

<実施の形態2>

実施の形態1においては、図13等を用いて、メタルキャップ9が、断面が矩形状となるように形成されている場合について説明した。しかし、これに限らず、例えば、メタルキャップ9は、断面が逆テーパー形状となるように形成されてもよい。

【0050】

図21は、実施の形態2に係る半導体装置の構造を示す断面図である。図21は、図13において、メタルキャップ9を、断面が逆テーパー形状(言い換えれば、上面の面積が底面の面積より大きい形状)となるように形成させたものである。このような形状のメタルキャップ9は、反応性を徐々に高めながら配線4のCu上に成膜させていく等の手法により形成できる。図21のメタルキャップ9は、膜厚および底面の幅は、図13と同様に、それぞれ、20nmおよび90nmであり、上面の幅は、図13より10nm大きく、100nmであるとする。上述したように、絶縁膜5はコンフォーマルに形成されるので、メタルキャップ9の上面の幅を拡げることにより、絶縁膜5を横方向に拡げることが可能となる。

【0051】

図21においては、図13に比較して、メタルキャップ9の膜厚を表す長さaは20nmで変わらない。また、絶縁膜5はコンフォーマルに形成されるので、重ね合わせが最も大きく(30nm)ずれた位置における絶縁膜5の最上部とメタルキャップ9の右端との距離cは50nmで変わらない。しかし、重ね合わせが最も大きく(30nm)ずれた位置とメタルキャップ9の右端との距離dは、メタルキャップ9の上面の幅を10nm拡げたことにより減少し、この減少量は、10/2=(100−90)/2=5となる。従って、d=30−5=25nmとなるので、b+a=√(c2−d2)+a≒43+20=63nmとなる。この値は、実施の形態1における60nmに比較して、約3nm大きい。

【0052】

すなわち、本実施の形態においては、実施の形態1に比較して、重ね合わせが最も大きくずれた位置における絶縁膜5の膜厚を、大きくすることが可能となる。これにより、オーバーエッチング量などを大きく設定することが可能となるので、プロセスマージンを拡大することができる。また、ばらつきが大きくなった場合においても、実施の形態1に比較して許容範囲が広いので、デバイスの故障に繋がらない。

【0053】

例えば、何らかの要因でエッチングが5nm過剰に行われた場合には、実施の形態1においては、残存する絶縁膜5の膜厚は0nmとなるので、第2部材を溝14に埋め込んだときにバリアメタル7がバリアメタル3または絶縁膜5に接することになる。一方、本実施の形態においては、このような場合においても、3nmの絶縁膜5が残存しているので、第2部材を溝14に埋め込んだときにバリアメタル7がバリアメタル3または絶縁膜5に接することはない。

【0054】

このように、本実施の形態においては、メタルキャップ9を、上面の面積が底面の面積より大きい形状となるように形成させることにより、絶縁膜5を横方向に拡げ、重ね合わせが最も大きくずれた位置における絶縁膜5の膜厚を大きくしている。従って、実施の形態1の効果に加えて、オーバーエッチング量などを大きく設定できるという効果を奏する。

【0055】

<実施の形態3>

実施の形態1では、図7に示されるように、絶縁膜5上に、絶縁膜6を形成する。しかし、図12を用いて上述したように、絶縁膜5は、メタルキャップ9と配線4とバリアメタル3とが互いに接する境界線においてCuの拡散を防ぐことができればよいので、あるいは、メタルキャップ9の側面のみにサイドウォールとして配置されていてもよい。

【0056】

図21〜25は、実施の形態3に係る半導体装置の製造方法を示す断面図である。なお、メタルキャップ9を形成するまでの工程については、実施の形態1で図2〜5を用いて説明したものと同様であるのでここでは説明を省略する。

【0057】

まず、図22に示されるように、メタルキャップ9上に、絶縁膜5を形成する。

【0058】

次に、図23に示されるように、絶縁膜5を全面エッチングすることにより、メタルキャップ9の上面を露出させる。このとき、指向性の強いドライエッチング法を用いることにより、メタルキャップ9の両側面のみに絶縁膜5を残存させサイドウォール17を形成することができる。

【0059】

次に、図24に示されるように、メタルキャップ9、サイドウォール17、および絶縁膜2上に、絶縁膜6を形成する。この絶縁膜6は、メタルキャップ9上方の領域が部分的に盛り上がった形状となるので、CMP法により平坦化する。

【0060】

次に、図25に示されるように、絶縁膜6を開口させることにより、溝14を形成する。この溝14は、次のような工程で形成される。

【0061】

すなわち、通常の写真製版プロセスによりビア部用のレジストパターン(図示しない)を形成する。次に、このレジストパターンをマスクとして、絶縁膜6を加工することにより溝14を形成する。この加工は、メタルキャップ9およびサイドウォール17をエッチングストッパーとしたドライエッチング法により行う。この際、絶縁膜6とサイドウォール17の選択比を有する条件に設定することで、サイドウォール17を、上部が部分的に除去されても完全には除去されないようにする。次に、レジストパターンを、アッシング法や薬液を用いたウェットエッチング法で除去する。次に、通常の写真製版プロセスにより配線部用のレジストパターンを形成する。次に、このレジストパターンをマスクとして、絶縁膜6を、配線部の高さ分だけ加工することにより、溝14を拡げる。次に、レジストパターンを、アッシング法や薬液を用いたウェットエッチング法で除去する。

【0062】

次に、図25に示されるように、通常のダマシンプロセスに従い、溝14へのメタルの埋め込みを行う。この埋め込みは、次のような工程で行われる。

【0063】

すなわち、まず、溝14内に、例えばTaやTaNを用いて、拡散バリアとなるバリアメタル7およびメッキ法でのシードとなるシード層を、スパッタ法により形成する。次に、メッキ法によりCuを埋め込む。次に、CMPにより、余分なCuおよびバリアメタルを除去する。これにより、溝14内にバリアメタル7および配線8が形成される。次に、CoWPやCoWB、NiWP等を用いて、無電解メッキ法により、配線8上にメタルキャップ15を形成する。メタルキャップ15は、配線8のCu上に選択的に成長するので、配線8上にのみ形成される。これにより、配線層22が形成される。

【0064】

SiNや、SiON、SiCN、SiCO等からなる絶縁膜5は、Cuに対してバリア性を有する反面、高い誘電率を有するので、半導体装置に含まれる絶縁膜5の量が多いと、チップの動作速度が低下する。本実施の形態に係る半導体装置においては、絶縁膜5を、サイドウォール16としてメタルキャップ9の側面にのみに残存させることにより、必要最小限の量に留めている。これにより、Cuの拡散を防止しつつチップの動作速度の低下を防止することができる。

【0065】

このように、本実施の形態は、実施の形態1の効果に加えて、チップの動作速度の低下を防止することができるという効果を奏する。

【0066】

<実施の形態4>

実施の形態3においては、図23に示されるように、絶縁膜5を、メタルキャップ9の両側面のみに残存するように全面エッチングする。このとき、さらにオーバーエッチングを行うことにより、絶縁膜5上に形成された異物を除去してもよい。

【0067】

図27〜30は、実施の形態4に係る半導体装置の製造方法を示す断面図である。図27〜30においては、絶縁膜5中に2個の配線4が互いに隣り合うように形成された場合について説明する。なお、メタルキャップ9を形成するまでの工程については、実施の形態1で図2〜5を用いて説明したものと同様であるのでここでは説明を省略する。

【0068】

まず、図27に示されるように、メタルキャップ9上に、絶縁膜5を形成する。

【0069】

次に、図28に示されるように、絶縁膜5を全面エッチングすることにより、メタルキャップ9の上面を露出させる。このとき、指向性の強いドライエッチング法を用いることにより、メタルキャップ9の両側面のみに絶縁膜5を残存させサイドウォール17を形成することができる。そして、さらにオーバーエッチングを行うことにより、絶縁膜2のうちサイドウォール17に覆われていない領域を5nm程度窪ませ凹部を形成する。

【0070】

次に、図29に示されるように、メタルキャップ9、サイドウォール17、および絶縁膜2上に、絶縁膜6を形成する。この絶縁膜6は、メタルキャップ9上方の領域が部分的に盛り上がった形状となるので、CMP法により平坦化する。

【0071】

次に、図30に示されるように、溝14を完成させるとともに溝14内にバリアメタル7および配線8を形成し配線8上にメタルキャップ15を形成する。なお、この手順は、実施の形態3で図25〜25を用いて説明したものと同様であるのでここでは説明を省略する。

【0072】

上述したように、メタルキャップ15は配線8のCu上に選択的に成長するが、図31に示されるように、選択性が破れることにより、異物18として絶縁膜2上に部分的に成膜する場合がある。このような場合には、この異物18がリークパスになる等の理由により、TDDB耐性が低くなる。本実施の形態に係る半導体装置の製造方法においては、サイドウォール17を形成するときに絶縁膜2をオーバーエッチングすることにより、絶縁膜2上の異物18を除去できる。これにより、異物18に起因するTDDB耐性の低下を防ぐことができる。

【0073】

このように、本実施の形態は、実施の形態3の効果に加えて、絶縁膜2上の異物18を除去することによりTDDB耐性の低下を防ぐことができるという効果を奏する。

【図面の簡単な説明】

【0074】

【図1】実施の形態1に係る半導体装置の構造を示す断面図である。

【図2】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図3】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図4】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図5】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図6】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図7】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図8】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図9】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図10】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図11】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図12】実施の形態1に係る半導体装置の有効性を示す比較用の断面図である。

【図13】実施の形態1に係るエッチング量の調節手法を示す断面図である。

【図14】実施の形態1に係るエッチング量の調節手法を示す断面図である。

【図15】実施の形態1に係る半導体装置の有効性を示す断面図である。

【図16】実施の形態1に係る半導体装置の有効性を示す比較用の断面図である。

【図17】実施の形態1に係る半導体装置の有効性を示す比較用の断面図である。

【図18】実施の形態1に係る半導体装置の有効性を示す比較用の断面図である。

【図19】実施の形態1に係る半導体装置の有効性を示す比較用の断面図である。

【図20】実施の形態1に係るエッチング量の調節手法に基づき残存するライナー膜厚を示す図である。

【図21】実施の形態2に係るエッチング量の調節手法を示す断面図である。

【図22】実施の形態3に係る半導体装置の製造方法を示す断面図である。

【図23】実施の形態3に係る半導体装置の製造方法を示す断面図である。

【図24】実施の形態3に係る半導体装置の製造方法を示す断面図である。

【図25】実施の形態3に係る半導体装置の製造方法を示す断面図である。

【図26】実施の形態3に係る半導体装置の製造方法を示す断面図である。

【図27】実施の形態4に係る半導体装置の製造方法を示す断面図である。

【図28】実施の形態4に係る半導体装置の製造方法を示す断面図である。

【図29】実施の形態4に係る半導体装置の製造方法を示す断面図である。

【図30】実施の形態4に係る半導体装置の製造方法を示す断面図である。

【図31】実施の形態4に係る半導体装置の製造方法の有効性を示す比較用の断面図である。

【符号の説明】

【0075】

1,2,5,6 絶縁膜、3,7 バリアメタル、4,8 配線、9,15 メタルキャップ、10 下層配線、11,14 溝、12,13 レジストパターン、17 サイドウォール、18 異物、21,22 配線層。

【技術分野】

【0001】

本発明は、半導体装置およびその製造方法に関し、特に、TDDB(Time Dependent Dielectric Breakdown:経時的絶縁膜破壊)を低減するための技術に関する。

【背景技術】

【0002】

半導体装置は集積性や高速性を追い求め、どんどん微細化が進んでいる。その一部である配線工程においても微細化が進んでいる。ところが微細化に従って信頼性の問題が深刻なものとなってきた。それら信頼性問題の一つに配線間のTDDBがある。配線間TDDBは通常配線間の距離に依存している。つまり微細化に伴い配線間の距離、または配線とビアとの距離が小さくなり、それにより配線間TDDBの問題も深刻化しているのである。微細化を進めるにはこの問題を解決する必要がある。

【0003】

一般に、配線間TDDBは、界面をメタルが拡散することにより生じると考えられており、また、電界強度に依存することが実験的に分かっている。従って、メタルが拡散すると考えられる界面上の距離(分離寸法)を大きくすることにより、配線間TDDBを抑制できると考えられる。

【0004】

ところで45nmノード世代より適用されると思われる技術にメタルキャップの技術がある。これは信頼性の問題の一つであるエレクトロマイグレーション(EM)の耐性を向上させる技術として注目を集めている。メタルキャップは無電界メッキ技術を用いることで、Cu配線上に選択的に形成されるメタルである。このメタルキャップはCuのバリアとしての役割を持っているだけでなく、これまで用いられてきた絶縁膜のバリアに比べてCuへの密着性が高いので、EMの耐性を向上させることができる。Cu配線やメタルキャップを用いた半導体装置は、例えば、特許文献1〜5に開示されている。

【0005】

【特許文献1】特開2004−152956号公報

【特許文献2】特開2004−015028号公報

【特許文献3】特開2002−151518号公報

【特許文献4】特開2002−118111号公報

【特許文献5】特開2001−230220号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

従来の半導体装置の構造においては、隣り合う2個の配線のうち一方配線の上層にビアが形成されているときに、一方配線とビアとの重ね合わせがずれると、ビア・他方配線間の分離寸法が、一方配線・他方配線間の分離寸法より小さくなる。このような場合には、一方配線・他方配線間のTDDBは、一方配線・他方配線間の分離寸法ではなくビア・他方配線間の分離寸法で決定されることとなる。従って、ビア・一方配線間の重ね合わせのずれ量が大きくなるにつれてTDDBが進行するという問題点があった。

【0007】

本発明は、以上の問題点を解決するためになされたものであり、ビア・配線間の重ね合わせがずれた場合にもTDDBを抑制できる半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明に係る半導体装置の製造方法は、第1絶縁膜に第1バリア層および第1配線を順次埋め込む工程と、第1配線上のみにメタルキャップを形成するメタルキャップ形成工程と、第1配線を構成する所定の金属に対してバリア性を有する第2絶縁膜を第1絶縁膜上およびメタルキャップ上に形成する工程と、第2絶縁膜にエッチングを行うことにより溝を形成する溝形成工程と、溝に第2バリア層および第2配線を順次埋め込む工程とを備え、溝形成工程において、エッチングは、位置ずれが生じた場合には第1バリア層および第1絶縁膜を露出させず且つメタルキャップの側面を部分的に露出させるような条件で行われる。

【発明の効果】

【0009】

本発明に係る半導体装置の製造方法は、第1絶縁膜に第1バリア層および第1配線を順次埋め込む工程と、第1配線上のみにメタルキャップを形成するメタルキャップ形成工程と、第1配線を構成する所定の金属に対してバリア性を有する第2絶縁膜を第1絶縁膜上およびメタルキャップ上に形成する工程と、第2絶縁膜にエッチングを行うことにより溝を形成する溝形成工程と、溝に第2バリア層および第2配線を順次埋め込む工程とを備え、溝形成工程において、エッチングは、位置ずれが生じた場合には第1バリア層および第1絶縁膜を露出させず且つメタルキャップの側面を部分的に露出させるような条件で行われる。従って、位置ずれが生じた場合においても、隣り合う第1配線間のTDDBを抑制することができる。

【発明を実施するための最良の形態】

【0010】

本発明に係る半導体装置の製造方法は、第1配線上に第2配線を重ね合わせるときに位置ずれが生じた場合においても、隣り合う第1配線間で分離寸法が小さくならないような構造が形成されることを特徴とする。以下、位置ずれが生じた場合の本発明の各実施の形態について、図面を用いて詳細に説明する。なお、一部の図面においては、図示の都合上、部材の幅等を部分的に異ならせている。

【0011】

<実施の形態1>

図1は、実施の形態1に係る半導体装置の構造を示す概略断面図である。

【0012】

図1に示されるように、順次積層された絶縁膜1,2内に形成された溝11内には、バリアメタル3およびCuからなる配線4が埋め込まれている(配線層21)。

【0013】

また、配線4上にはメタルキャップ9が配置され、メタルキャップ9上には、絶縁膜5,6が順次積層されている。絶縁膜5,6内に形成された溝14内には、バリアメタル7およびCuからなる配線8が埋め込まれている(配線層22)。この絶縁膜5は、Cuが拡散されない(Cuに対してバリア性を有する)ものとする。以下では、このような絶縁膜をライナー膜とも呼ぶ。

【0014】

図1に示されるように、本実施の形態に係る半導体装置は、配線8が配線4に対してずれて重ね合わせられた場合に、バリアメタル7が、メタルキャップ9には接するが絶縁膜2やバリアメタル3には接しないように形成されていることを特徴とする。このような溝14を形成するように絶縁膜5のエッチング量を調節することにより、図15を用いて後述するように、配線8が配線4に対してずれて重ね合わせられた場合においても、隣り合う配線4間で分離寸法が小さくならないようにすることが可能となる。なお、重ね合わせにおいて位置ずれが生じない場合には、溝14を形成するための絶縁膜5のエッチングは、メタルキャップ9上の領域のみで行われるので、メタルキャップ9で止まることになる。従って、このような場合には、エッチング量を調節しなくても、バリアメタル7が絶縁膜2やバリアメタル3に接することはない。

【0015】

図2〜11は、図1の半導体装置の製造方法を示す断面図である。Cu配線を形成する手法としてはさまざまな手法があるが、ここでは、レジストパターンをマスクに用いてビアファーストのデュアルダマシン法で形成する手法を例に説明する。なお、本発明は、ビアファーストのデュアルダマシン法に限らず、シングルダマシン法や、トレンチファーストのデュアルダマシン法、ハードマスクを用いる手法等へも適用可能である。

【0016】

まず、図2〜5を用いて、ダマシン法により配線層21を形成する工程を説明する。図2〜5に示されるように、配線層21に形成される配線4は、ビア部を有さず配線部のみからなるものとする。

【0017】

まず、図2に示されるように、下層配線10上に、下層配線10を構成する金属に対してバリア性を有し且つ後の工程においてエッチングストッパーとして機能する絶縁膜1を形成する。絶縁膜1としては、SiNや、SiON、SiCN、SiCO等を用いる。そして、絶縁膜1上に、絶縁膜2を形成する。絶縁膜2としては、シリコン酸化膜や、SiOF、SiOC、有機膜等を用いる。なお、絶縁膜2の中央部には、後の工程で配線4のエッチングストッパーとして機能する層を必要に応じて形成してもよい。

【0018】

次に、図3に示されるように、ダマシン法を用いて、絶縁膜2を開口させることにより、溝11を形成する。この溝11は、次のような工程で形成される。

【0019】

すなわち、まず、通常の写真製版プロセスにより配線部用のレジストパターン(図示しない)を形成する(上述したように、配線4はビア部を有さず配線部のみからなるので、このレジストパターンは配線4全体に対応している)。次に、このレジストパターンをマスクとして、絶縁膜2を、配線部の高さ(すなわち配線4の高さ)分だけ加工することにより、溝11を形成する。次に、レジストパターンを、アッシング法や薬液を用いたウェットエッチング法で除去する。

【0020】

次に、図4に示されるように、通常のダマシンプロセスに従い、溝11へのメタルの埋め込みを行う。この埋め込みは、次のような工程で行われる。

【0021】

すなわち、まず、溝11内に、例えばTaやTaNを用いて、拡散バリアとなるバリアメタル3およびメッキ法でのシードとなるシード層を、スパッタ法により形成する。次に、メッキ法によりCuを埋め込む。次に、CMPにより、余分なCuおよびバリアメタルを除去する。これにより、溝11内にバリアメタル3および配線4が形成される。

【0022】

次に、図5に示されるように、CoWPやCoWB、NiWP等を用いて、無電解メッキ法により、配線4上にメタルキャップ9を形成する。メタルキャップ9は、配線4のCu上に選択的に成長するので、配線4上にのみ形成される。これにより、配線層21が形成される。

【0023】

次に、図6〜11を用いて、ダマシン法により配線層22を形成する工程を説明する。図6〜11に示されるように、配線層22に形成される配線8は、ビア部および配線部を有するものとする。

【0024】

まず、図6に示されるように、メタルキャップ9、バリアメタル3、および絶縁膜2上に、Cuに対してバリア性を有する絶縁膜5を形成する。絶縁膜5としては、SiNや、SiON、SiCN、SiCO等を用いる。この絶縁膜5は、CVD等を用いて、コンフォーマルに(すなわち、メタルキャップ9等の下方の形状に忠実に成長するように)形成させる。これにより、絶縁膜5は、メタルキャップ9上方の領域が部分的に盛り上がった形状となる。

【0025】

次に、図7に示されるように、絶縁膜5上に、絶縁膜6を形成する。絶縁膜6としては、シリコン酸化膜や、SiOF、SiOC、有機膜等を用いる。この絶縁膜6は、メタルキャップ9上方の領域が部分的に盛り上がった形状となるので、CMP法により平坦化する。

【0026】

次に、図8〜10に示されるように、絶縁膜6を開口させることにより、溝14を形成する。この溝14は、次のような工程で形成される。

【0027】

すなわち、まず、図8に示されるように、通常の写真製版プロセスによりビア部用のレジストパターン12を形成する。次に、このレジストパターン12をマスクとして、絶縁膜6を加工することにより、溝14を形成する。この加工は、通常、絶縁膜5をエッチングストッパーとしたドライエッチング法により行われる。次に、レジストパターン12を、アッシング法や薬液を用いたウェットエッチング法で除去する。次に、図9に示されるように、通常の写真製版プロセスにより配線部用のレジストパターン13を形成する。次に、このレジストパターン13をマスクとして、絶縁膜6を、配線部の高さ分だけ加工することにより、溝14を拡げる。次に、レジストパターン13を、アッシング法や薬液を用いたウェットエッチング法で除去する。

【0028】

次に、図10に示されるように、絶縁膜5をドライエッチング法で加工することにより、溝14を部分的に深くする。これにより、ビア部および配線部を有する(配線8用の)溝14が完成する。このドライエッチングは、図13〜14を用いて後述するような手法でエッチング量を調節することにより、メタルキャップ9の側面が部分的に露出し絶縁膜2およびバリアメタル3が露出しないように行う。

【0029】

次に、図11に示されるように、通常のダマシンプロセスに従い、溝14へのメタルの埋め込みを行う。この埋め込みは、次のような工程で行われる。

【0030】

すなわち、まず、溝14内に、例えばTaやTaNを用いて、拡散バリアとなるバリアメタル7およびメッキ法でのシードとなるシード層を、スパッタ法により形成する。次に、メッキ法によりCuを埋め込む。次に、CMPにより、余分なCuおよびバリアメタルを除去する。これにより、溝14内にバリアメタル7および配線8が形成される。次に、CoWPやCoWB、NiWP等を用いて、無電解メッキ法により、配線8上にメタルキャップ15を形成する。メタルキャップ15は、配線8のCu上に選択的に成長するので、配線8上にのみ形成される。これにより、配線層22が形成される。

【0031】

以上の工程を繰り返すことにより、所望の配線層数を有する半導体装置が形成される。

【0032】

なお、上述においては、下層の配線層21には配線部のみを有する配線4をを埋め込み上層の配線層22にはビア部および配線部を有する配線8埋め込む場合について説明したが、あるいは、配線8と同様に、配線4にもビア部を設けてもよい。

【0033】

また、本明細書では、配線4を第1配線、バリアメタル3を第1バリア層、絶縁膜2を第1絶縁膜、配線8を第2配線、バリアメタル7を第2バリア層、絶縁膜5を第2絶縁膜、絶縁膜6を第3絶縁膜とそれぞれ呼ぶ。また、第1配線(配線4)と第1バリア層(バリアメタル3)とをまとめて第1配線部材と呼ぶとともに、第2配線(配線8)と第2バリア層(バリアメタル7)とをまとめて第2配線部材と呼ぶ。

【0034】

図12は、Cuに対してバリア性を有する絶縁膜5を形成することによる有効性を示すために、図1において絶縁膜5を形成せずに絶縁膜6を形成した場合の構造を比較用に示す断面図である。図12(a)においては、点線で示されるように、メタルキャップ9は配線4上に選択的に成長するので、メタルキャップ9と配線4とバリアメタル3との3種類の材料が互いに接する境界線(図12においては点)が存在する。従って、図12(b)に示されるように、この境界線から絶縁膜6にCuが拡散してしまう。一方、本実施の形態に係る半導体装置においては、図1等に示されるように、この境界線にはCuに対してバリア性を有する絶縁膜5が形成されるので、絶縁膜5にCuが拡散することはない。

【0035】

次に、図13〜14を用いて、メタルキャップ9の側面が部分的に露出し絶縁膜2およびバリアメタル3が露出しないようにエッチング量を調節する手法について説明する。以下では、65nmノードプロセスを例にとり説明する。また、本実施の形態においては、メタルキャップ9は、配線4上で、反応性を一定に保つことにより断面が矩形状となるように成長するものとする。

【0036】

図13〜14に示されるように、メタルキャップ9の膜厚が20nmであり、絶縁膜5(盛り上がった領域の端部すなわち表面が平らでない部分を除く)の膜厚が50nmであり、配線4,8間の重ね合わせのずれ量が30nmであるとする(この30nmのずれ量は、65nmノードプロセスにおいては十分に可能な値である)。図13には、重ね合わせのずれ量が0nmである場合が示されており、図14には、重ね合わせのずれ量が30nmである(配線8が配線4に対して右方向に30nmずれている)場合が示されている。

【0037】

65nmノードプロセスにおいては、配線幅、分離幅(配線間隔)、およびビア径は、いずれも100nmに設定される場合が多い。しかし、図13〜14に示されるように、実際の構造においては配線部材およびビア部材はいずれもテーパー形状となるので、それぞれの幅(図における横方向の長さ)は、第1配線部材の上面では110nm程度となり、第2配線部材の底面では90nm程度となる。また、配線4,8に隣接するようにバリアメタル3,7がそれぞれ配置されているが、ここでは、バリアメタル3,7の膜厚を10nmとする(一般的なバリアメタルの膜厚は5〜10nm)。

【0038】

上述したように、メタルキャップ9は、配線4上にのみ形成され断面が矩形状であるので、メタルキャップ9の幅は、(第1配線部材の上面の幅)−(バリアメタル3の膜厚)×2=110−10×2=90nmとなる。図13に示されるように、重ね合わせのずれ量が0nmである場合には、メタルキャップ9の幅が90nmで第2配線部材の底面の幅が90nmであるので、メタルキャップ9の端と第2配線部材の底面の端とが横方向で同じ位置となる。

【0039】

図13において、メタルキャップ9の膜厚を表す長さa=20nmであり、重ね合わせが最も大きくずれた位置とメタルキャップ9の右端との距離d=30nmである。また、上述したように、絶縁膜5はコンフォーマルに形成されているので、長さd=30nmずれた位置における絶縁膜5の最上部とメタルキャップ9の右端との距離c=50nmとなる。従って、重ね合わせが30nmずれた位置(言い換えれば重ね合わせが最も大きくずれた位置)における絶縁膜5の膜厚は、b+a=√(c2−d2)+a=√(502−302)+20=40+20=60nmとなる。

【0040】

上述したように、絶縁膜5(盛り上がった領域の端部すなわち表面が平らでない部分を除く)の膜厚は50nmであるので、メタルキャップ9が露出するように溝14を形成するときには、絶縁膜5を少なくとも50nm分はエッチングする必要がある。また、ばらつきを考慮して10%のオーバーエッチングを行うとすると、55nm分エッチングすることとなる。しかし、上述したように、重ね合わせが最も大きくずれた位置であっても、絶縁膜5の膜厚は60nmであるので、このようなオーバーエッチングを行った場合においても、5nm分の絶縁膜5が残存することより、絶縁膜2およびバリアメタル3は露出しない。なお、図14に示されるように、重ね合わせのずれ量が0nmより大きく30nmより小さい場合においても、絶縁膜5は、60nmより大きい(且つ50+20=70nmより小さい)膜厚を有するので、オーバーエッチングを行った場合においても、絶縁膜2およびバリアメタル3は露出しない。このような条件を満たすようにエッチング量を調節することにより、絶縁膜2およびバリアメタル3が露出せずメタルキャップ9の側面が部分的に露出するようなエッチングを行うことが可能となる。

【0041】

図15は、本実施の形態に係る半導体装置の有効性を示す断面図である。図15に示されるように、本実施の形態に係る半導体装置においては、バリアメタル7が絶縁膜2およびバリアメタル3に接さない。上述したように、配線間TDDBは、界面をCuが拡散することにより生じると考えられるので、配線間TDDBを抑制するためには、Cuが拡散すると考えられる界面上の距離(分離寸法)を小さくする必要がある。図15においては、左側の配線4と配線8との分離寸法は、互いに隣り合う2個のバリアメタル3間の距離を表す長さe、バリアメタル3の膜厚を表す長さf、およびエッチング後に残存する絶縁膜5の膜厚を表す長さgを用いて、長さ(e+f+g)となる。一方、左側の配線4と右側の配線4との分離寸法は、長さeであるので、配線8が配線4に対してずれて重ね合わせられた場合においても、隣り合う配線4間のTDDBは、より小さい方の長さeに依存する。従って、位置ずれが生じた場合にも、配線間TDDBが大きくなることはない。

【0042】

図16〜19は、バリアメタル7が絶縁膜2およびバリアメタル3に接触するように形成された半導体装置を比較用に示す断面図である。図16〜19においては、配線8が配線4に対して左方向にずれている場合が示されている。図16〜17はメタルキャップ9が配置されない場合を示しており、図18〜19はメタルキャップ9が配置された場合を示している。また、図17,19は、それぞれ、図16,18において第1配線部材と第2配線部材との境界付近を拡大するとともに隣り合う第2配線部材を追加し示したものである。

【0043】

図17,19に示されるように、バリアメタル7が絶縁膜2およびバリアメタル3に接するように形成されている場合においては、左側の配線4と配線8との分離寸法は長さhとなる。長さhは、左側の配線4と右側の配線4との分離寸法(図15の長さeに相当)より小さいので、隣り合う配線4間のTDDBは、長さhに依存する。従って、位置ずれが生じた場合には、配線間TDDBが大きくなる。

【0044】

図20には、重ね合わせのずれ量を20nm,25nm,30nm,35nmと変化させ且つバリアメタル7・メタルキャップ9間における絶縁膜5(盛り上がった領域の端部すなわち表面が平らでない部分を除く)の膜厚(ライナー膜厚)を70nm,60nm,50nm,40nmと変化させた場合において、エッチングの後に残存する絶縁膜5の膜厚(エッチングの前の絶縁膜5の膜厚−必要とされるエッチング量)が示されている。図20(a)〜(d)は、それぞれ、オーバーエッチング(OE)量を10%または20%とし且つメタルキャップ9の膜厚を20nmまたは30nmとした場合に対応している。図20において、エッチングの後に残存する絶縁膜5の膜厚が正の値となるような条件を選択することにより、絶縁膜2およびバリアメタル3が露出せずメタルキャップ9の側面が部分的に露出するようなエッチングを行うことが可能となる。

【0045】

なお、微細化が進んだ場合には、図20の各パラメータを同率にシュリンクしていくことにより、適切な条件を選択することが可能となる。例えば、図20(a)では、0.1倍にシュリンクすることにより、オーバーエッチング量が10%、メタルキャップ9の膜厚が2nm、重ね合わせのずれ量が3nm、ライナー膜厚が5nmという条件においては、エッチングの後に残存する絶縁膜5の膜厚は0.5nmとなる。

【0046】

このように、本実施の形態においては、配線4,8の重ね合わせ(配線4の配線部と配線8のビア部との重ね合わせ)において位置ずれが生じた場合においても、配線4,8間の分離寸法は、図17,19の長さhではなく図15の長さ(e+f+g)で決定するので、隣り合う配線4間のTDDBは、図15の長さeに依存する。従って、ビア・配線間の重ね合わせにおいて位置ずれが生じた場合にも、隣り合う配線4間のTDDBを抑制することができる。

【0047】

なお、上述においては、配線4がCuからなり且つ絶縁膜5がCuに対してバリア性を有する場合について説明したが、Cuに限らず、他の金属であってもよい。

【0048】

また、上述においては、図1に示されるような構造を、図13〜14に示されるような手法を用いてエッチング量を調節することにより形成する場合について説明したが、図13〜14に示されるような手法に限らず、あるいは、他の既存の手法を用いてエッチング量を調節してもよい。

【0049】

<実施の形態2>

実施の形態1においては、図13等を用いて、メタルキャップ9が、断面が矩形状となるように形成されている場合について説明した。しかし、これに限らず、例えば、メタルキャップ9は、断面が逆テーパー形状となるように形成されてもよい。

【0050】

図21は、実施の形態2に係る半導体装置の構造を示す断面図である。図21は、図13において、メタルキャップ9を、断面が逆テーパー形状(言い換えれば、上面の面積が底面の面積より大きい形状)となるように形成させたものである。このような形状のメタルキャップ9は、反応性を徐々に高めながら配線4のCu上に成膜させていく等の手法により形成できる。図21のメタルキャップ9は、膜厚および底面の幅は、図13と同様に、それぞれ、20nmおよび90nmであり、上面の幅は、図13より10nm大きく、100nmであるとする。上述したように、絶縁膜5はコンフォーマルに形成されるので、メタルキャップ9の上面の幅を拡げることにより、絶縁膜5を横方向に拡げることが可能となる。

【0051】

図21においては、図13に比較して、メタルキャップ9の膜厚を表す長さaは20nmで変わらない。また、絶縁膜5はコンフォーマルに形成されるので、重ね合わせが最も大きく(30nm)ずれた位置における絶縁膜5の最上部とメタルキャップ9の右端との距離cは50nmで変わらない。しかし、重ね合わせが最も大きく(30nm)ずれた位置とメタルキャップ9の右端との距離dは、メタルキャップ9の上面の幅を10nm拡げたことにより減少し、この減少量は、10/2=(100−90)/2=5となる。従って、d=30−5=25nmとなるので、b+a=√(c2−d2)+a≒43+20=63nmとなる。この値は、実施の形態1における60nmに比較して、約3nm大きい。

【0052】

すなわち、本実施の形態においては、実施の形態1に比較して、重ね合わせが最も大きくずれた位置における絶縁膜5の膜厚を、大きくすることが可能となる。これにより、オーバーエッチング量などを大きく設定することが可能となるので、プロセスマージンを拡大することができる。また、ばらつきが大きくなった場合においても、実施の形態1に比較して許容範囲が広いので、デバイスの故障に繋がらない。

【0053】

例えば、何らかの要因でエッチングが5nm過剰に行われた場合には、実施の形態1においては、残存する絶縁膜5の膜厚は0nmとなるので、第2部材を溝14に埋め込んだときにバリアメタル7がバリアメタル3または絶縁膜5に接することになる。一方、本実施の形態においては、このような場合においても、3nmの絶縁膜5が残存しているので、第2部材を溝14に埋め込んだときにバリアメタル7がバリアメタル3または絶縁膜5に接することはない。

【0054】

このように、本実施の形態においては、メタルキャップ9を、上面の面積が底面の面積より大きい形状となるように形成させることにより、絶縁膜5を横方向に拡げ、重ね合わせが最も大きくずれた位置における絶縁膜5の膜厚を大きくしている。従って、実施の形態1の効果に加えて、オーバーエッチング量などを大きく設定できるという効果を奏する。

【0055】

<実施の形態3>

実施の形態1では、図7に示されるように、絶縁膜5上に、絶縁膜6を形成する。しかし、図12を用いて上述したように、絶縁膜5は、メタルキャップ9と配線4とバリアメタル3とが互いに接する境界線においてCuの拡散を防ぐことができればよいので、あるいは、メタルキャップ9の側面のみにサイドウォールとして配置されていてもよい。

【0056】

図21〜25は、実施の形態3に係る半導体装置の製造方法を示す断面図である。なお、メタルキャップ9を形成するまでの工程については、実施の形態1で図2〜5を用いて説明したものと同様であるのでここでは説明を省略する。

【0057】

まず、図22に示されるように、メタルキャップ9上に、絶縁膜5を形成する。

【0058】

次に、図23に示されるように、絶縁膜5を全面エッチングすることにより、メタルキャップ9の上面を露出させる。このとき、指向性の強いドライエッチング法を用いることにより、メタルキャップ9の両側面のみに絶縁膜5を残存させサイドウォール17を形成することができる。

【0059】

次に、図24に示されるように、メタルキャップ9、サイドウォール17、および絶縁膜2上に、絶縁膜6を形成する。この絶縁膜6は、メタルキャップ9上方の領域が部分的に盛り上がった形状となるので、CMP法により平坦化する。

【0060】

次に、図25に示されるように、絶縁膜6を開口させることにより、溝14を形成する。この溝14は、次のような工程で形成される。

【0061】

すなわち、通常の写真製版プロセスによりビア部用のレジストパターン(図示しない)を形成する。次に、このレジストパターンをマスクとして、絶縁膜6を加工することにより溝14を形成する。この加工は、メタルキャップ9およびサイドウォール17をエッチングストッパーとしたドライエッチング法により行う。この際、絶縁膜6とサイドウォール17の選択比を有する条件に設定することで、サイドウォール17を、上部が部分的に除去されても完全には除去されないようにする。次に、レジストパターンを、アッシング法や薬液を用いたウェットエッチング法で除去する。次に、通常の写真製版プロセスにより配線部用のレジストパターンを形成する。次に、このレジストパターンをマスクとして、絶縁膜6を、配線部の高さ分だけ加工することにより、溝14を拡げる。次に、レジストパターンを、アッシング法や薬液を用いたウェットエッチング法で除去する。

【0062】

次に、図25に示されるように、通常のダマシンプロセスに従い、溝14へのメタルの埋め込みを行う。この埋め込みは、次のような工程で行われる。

【0063】

すなわち、まず、溝14内に、例えばTaやTaNを用いて、拡散バリアとなるバリアメタル7およびメッキ法でのシードとなるシード層を、スパッタ法により形成する。次に、メッキ法によりCuを埋め込む。次に、CMPにより、余分なCuおよびバリアメタルを除去する。これにより、溝14内にバリアメタル7および配線8が形成される。次に、CoWPやCoWB、NiWP等を用いて、無電解メッキ法により、配線8上にメタルキャップ15を形成する。メタルキャップ15は、配線8のCu上に選択的に成長するので、配線8上にのみ形成される。これにより、配線層22が形成される。

【0064】

SiNや、SiON、SiCN、SiCO等からなる絶縁膜5は、Cuに対してバリア性を有する反面、高い誘電率を有するので、半導体装置に含まれる絶縁膜5の量が多いと、チップの動作速度が低下する。本実施の形態に係る半導体装置においては、絶縁膜5を、サイドウォール16としてメタルキャップ9の側面にのみに残存させることにより、必要最小限の量に留めている。これにより、Cuの拡散を防止しつつチップの動作速度の低下を防止することができる。

【0065】

このように、本実施の形態は、実施の形態1の効果に加えて、チップの動作速度の低下を防止することができるという効果を奏する。

【0066】

<実施の形態4>

実施の形態3においては、図23に示されるように、絶縁膜5を、メタルキャップ9の両側面のみに残存するように全面エッチングする。このとき、さらにオーバーエッチングを行うことにより、絶縁膜5上に形成された異物を除去してもよい。

【0067】

図27〜30は、実施の形態4に係る半導体装置の製造方法を示す断面図である。図27〜30においては、絶縁膜5中に2個の配線4が互いに隣り合うように形成された場合について説明する。なお、メタルキャップ9を形成するまでの工程については、実施の形態1で図2〜5を用いて説明したものと同様であるのでここでは説明を省略する。

【0068】

まず、図27に示されるように、メタルキャップ9上に、絶縁膜5を形成する。

【0069】

次に、図28に示されるように、絶縁膜5を全面エッチングすることにより、メタルキャップ9の上面を露出させる。このとき、指向性の強いドライエッチング法を用いることにより、メタルキャップ9の両側面のみに絶縁膜5を残存させサイドウォール17を形成することができる。そして、さらにオーバーエッチングを行うことにより、絶縁膜2のうちサイドウォール17に覆われていない領域を5nm程度窪ませ凹部を形成する。

【0070】

次に、図29に示されるように、メタルキャップ9、サイドウォール17、および絶縁膜2上に、絶縁膜6を形成する。この絶縁膜6は、メタルキャップ9上方の領域が部分的に盛り上がった形状となるので、CMP法により平坦化する。

【0071】

次に、図30に示されるように、溝14を完成させるとともに溝14内にバリアメタル7および配線8を形成し配線8上にメタルキャップ15を形成する。なお、この手順は、実施の形態3で図25〜25を用いて説明したものと同様であるのでここでは説明を省略する。

【0072】

上述したように、メタルキャップ15は配線8のCu上に選択的に成長するが、図31に示されるように、選択性が破れることにより、異物18として絶縁膜2上に部分的に成膜する場合がある。このような場合には、この異物18がリークパスになる等の理由により、TDDB耐性が低くなる。本実施の形態に係る半導体装置の製造方法においては、サイドウォール17を形成するときに絶縁膜2をオーバーエッチングすることにより、絶縁膜2上の異物18を除去できる。これにより、異物18に起因するTDDB耐性の低下を防ぐことができる。

【0073】

このように、本実施の形態は、実施の形態3の効果に加えて、絶縁膜2上の異物18を除去することによりTDDB耐性の低下を防ぐことができるという効果を奏する。

【図面の簡単な説明】

【0074】

【図1】実施の形態1に係る半導体装置の構造を示す断面図である。

【図2】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図3】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図4】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図5】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図6】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図7】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図8】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図9】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図10】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図11】実施の形態1に係る半導体装置の製造方法を示す断面図である。

【図12】実施の形態1に係る半導体装置の有効性を示す比較用の断面図である。

【図13】実施の形態1に係るエッチング量の調節手法を示す断面図である。

【図14】実施の形態1に係るエッチング量の調節手法を示す断面図である。

【図15】実施の形態1に係る半導体装置の有効性を示す断面図である。

【図16】実施の形態1に係る半導体装置の有効性を示す比較用の断面図である。

【図17】実施の形態1に係る半導体装置の有効性を示す比較用の断面図である。

【図18】実施の形態1に係る半導体装置の有効性を示す比較用の断面図である。

【図19】実施の形態1に係る半導体装置の有効性を示す比較用の断面図である。

【図20】実施の形態1に係るエッチング量の調節手法に基づき残存するライナー膜厚を示す図である。

【図21】実施の形態2に係るエッチング量の調節手法を示す断面図である。

【図22】実施の形態3に係る半導体装置の製造方法を示す断面図である。

【図23】実施の形態3に係る半導体装置の製造方法を示す断面図である。

【図24】実施の形態3に係る半導体装置の製造方法を示す断面図である。

【図25】実施の形態3に係る半導体装置の製造方法を示す断面図である。

【図26】実施の形態3に係る半導体装置の製造方法を示す断面図である。

【図27】実施の形態4に係る半導体装置の製造方法を示す断面図である。

【図28】実施の形態4に係る半導体装置の製造方法を示す断面図である。

【図29】実施の形態4に係る半導体装置の製造方法を示す断面図である。

【図30】実施の形態4に係る半導体装置の製造方法を示す断面図である。

【図31】実施の形態4に係る半導体装置の製造方法の有効性を示す比較用の断面図である。

【符号の説明】

【0075】

1,2,5,6 絶縁膜、3,7 バリアメタル、4,8 配線、9,15 メタルキャップ、10 下層配線、11,14 溝、12,13 レジストパターン、17 サイドウォール、18 異物、21,22 配線層。

【特許請求の範囲】

【請求項1】

第1絶縁膜に第1バリア層および第1配線を順次埋め込む工程と、

前記第1配線上のみにメタルキャップを形成するメタルキャップ形成工程と、

前記第1配線を構成する所定の金属に対してバリア性を有する第2絶縁膜を前記第1絶縁膜上および前記メタルキャップ上に形成する工程と、

前記第2絶縁膜にエッチングを行うことにより溝を形成する溝形成工程と、

前記溝に第2バリア層および第2配線を順次埋め込む工程と

を備え、

前記溝形成工程において、前記エッチングは、位置ずれが生じた場合には前記第1バリア層および前記第1絶縁膜を露出させず且つ前記メタルキャップの側面を部分的に露出させるような条件で行われる

半導体装置の製造方法。

【請求項2】

請求項1に記載の半導体装置の製造方法であって、

前記メタルキャップ形成工程においては、前記メタルキャップは、成膜における反応性を徐々に高めながら形成される

半導体装置の製造方法。

【請求項3】

第1絶縁膜に第1バリア層および第1配線を順次埋め込む工程と、

前記第1配線上のみにメタルキャップを形成する工程と、

前記第1配線を構成する所定の金属に対してバリア性を有する第2絶縁膜を前記第1絶縁膜上および前記メタルキャップ上に形成する工程と、

前記第2絶縁膜にエッチングを行うことにより前記メタルキャップ側面のみに前記第2絶縁膜を残しサイドウォールを形成するサイドウォール形成工程と、

前記メタルキャップおよび前記第1絶縁膜および前記サイドウォール上に第3絶縁膜を形成する工程と、

前記第3絶縁膜にエッチングを行うことにより溝を形成する溝形成工程と、

前記溝に第2バリア層および第2配線を順次埋め込む工程と

を備え、

前記溝形成工程において、前記エッチングは、位置ずれが生じた場合には前記第1バリア層および前記第1絶縁膜を露出させず且つ前記メタルキャップの側面を部分的に露出させるような条件で行われる

半導体装置の製造方法。

【請求項4】

請求項3に記載の半導体装置の製造方法であって、

前記サイドウォール形成工程において、オーバーエッチングを行うことにより前記第1絶縁膜のうち上方に前記第2絶縁膜が形成されていない領域に凹部を形成する工程

を備える半導体装置の製造方法。

【請求項5】

請求項1乃至請求項4のいずれかに記載の半導体装置の製造方法であって、

前記所定の金属は、Cuを含む

半導体装置の製造方法。

【請求項6】

第1絶縁膜と、

前記第1絶縁膜に第1バリア層を介して埋め込まれた第1配線と、

前記第1配線上のみに配置されたメタルキャップと、

前記第1配線を構成する所定の金属に対してバリア性を有し前記第1絶縁膜上および前記メタルキャップ上に配置された第2絶縁膜と、

前記第2絶縁膜に第2バリア層を介して埋め込まれた第2配線と

を備え、

前記第2バリア層は、前記第1バリア層および前記第1絶縁膜に接することなく前記メタルキャップの側面に接している

半導体装置。

【請求項7】

請求項6に記載の半導体装置であって、

前記メタルキャップは、上面の面積が底面の面積より大きい

半導体装置。

【請求項8】

第1絶縁膜と、

前記第1絶縁膜に第1バリア層を介して埋め込まれた第1配線と、

前記第1配線上のみに配置されたメタルキャップと、

前記第1配線を構成する所定の金属に対してバリア性を有し前記メタルキャップ側面にサイドウォールとして配置された第2絶縁膜と、

前記メタルキャップおよび前記第1絶縁膜および前記第2絶縁膜上に配置された第3絶縁膜と、

前記第2絶縁膜および前記第3絶縁膜に第2バリア層を介して埋め込まれた第2配線と

を備え、

前記第2バリア層は、前記第1バリア層および前記第1絶縁膜に接することなく前記メタルキャップの側面に接している

半導体装置。

【請求項9】

請求項8に記載の半導体装置であって、

前記第1絶縁膜は、上方に前記第2絶縁膜が配置されていない領域に凹部を有する

半導体装置。

【請求項10】

請求項6乃至請求項9のいずれかに記載の半導体装置であって、

前記所定の金属は、Cuを含む

半導体装置。

【請求項1】

第1絶縁膜に第1バリア層および第1配線を順次埋め込む工程と、

前記第1配線上のみにメタルキャップを形成するメタルキャップ形成工程と、

前記第1配線を構成する所定の金属に対してバリア性を有する第2絶縁膜を前記第1絶縁膜上および前記メタルキャップ上に形成する工程と、

前記第2絶縁膜にエッチングを行うことにより溝を形成する溝形成工程と、

前記溝に第2バリア層および第2配線を順次埋め込む工程と

を備え、

前記溝形成工程において、前記エッチングは、位置ずれが生じた場合には前記第1バリア層および前記第1絶縁膜を露出させず且つ前記メタルキャップの側面を部分的に露出させるような条件で行われる

半導体装置の製造方法。

【請求項2】

請求項1に記載の半導体装置の製造方法であって、

前記メタルキャップ形成工程においては、前記メタルキャップは、成膜における反応性を徐々に高めながら形成される

半導体装置の製造方法。

【請求項3】

第1絶縁膜に第1バリア層および第1配線を順次埋め込む工程と、

前記第1配線上のみにメタルキャップを形成する工程と、

前記第1配線を構成する所定の金属に対してバリア性を有する第2絶縁膜を前記第1絶縁膜上および前記メタルキャップ上に形成する工程と、

前記第2絶縁膜にエッチングを行うことにより前記メタルキャップ側面のみに前記第2絶縁膜を残しサイドウォールを形成するサイドウォール形成工程と、

前記メタルキャップおよび前記第1絶縁膜および前記サイドウォール上に第3絶縁膜を形成する工程と、

前記第3絶縁膜にエッチングを行うことにより溝を形成する溝形成工程と、

前記溝に第2バリア層および第2配線を順次埋め込む工程と

を備え、

前記溝形成工程において、前記エッチングは、位置ずれが生じた場合には前記第1バリア層および前記第1絶縁膜を露出させず且つ前記メタルキャップの側面を部分的に露出させるような条件で行われる

半導体装置の製造方法。

【請求項4】

請求項3に記載の半導体装置の製造方法であって、

前記サイドウォール形成工程において、オーバーエッチングを行うことにより前記第1絶縁膜のうち上方に前記第2絶縁膜が形成されていない領域に凹部を形成する工程

を備える半導体装置の製造方法。

【請求項5】

請求項1乃至請求項4のいずれかに記載の半導体装置の製造方法であって、

前記所定の金属は、Cuを含む

半導体装置の製造方法。

【請求項6】

第1絶縁膜と、

前記第1絶縁膜に第1バリア層を介して埋め込まれた第1配線と、

前記第1配線上のみに配置されたメタルキャップと、

前記第1配線を構成する所定の金属に対してバリア性を有し前記第1絶縁膜上および前記メタルキャップ上に配置された第2絶縁膜と、

前記第2絶縁膜に第2バリア層を介して埋め込まれた第2配線と

を備え、

前記第2バリア層は、前記第1バリア層および前記第1絶縁膜に接することなく前記メタルキャップの側面に接している

半導体装置。

【請求項7】

請求項6に記載の半導体装置であって、

前記メタルキャップは、上面の面積が底面の面積より大きい

半導体装置。

【請求項8】

第1絶縁膜と、

前記第1絶縁膜に第1バリア層を介して埋め込まれた第1配線と、

前記第1配線上のみに配置されたメタルキャップと、

前記第1配線を構成する所定の金属に対してバリア性を有し前記メタルキャップ側面にサイドウォールとして配置された第2絶縁膜と、

前記メタルキャップおよび前記第1絶縁膜および前記第2絶縁膜上に配置された第3絶縁膜と、

前記第2絶縁膜および前記第3絶縁膜に第2バリア層を介して埋め込まれた第2配線と

を備え、

前記第2バリア層は、前記第1バリア層および前記第1絶縁膜に接することなく前記メタルキャップの側面に接している

半導体装置。

【請求項9】

請求項8に記載の半導体装置であって、

前記第1絶縁膜は、上方に前記第2絶縁膜が配置されていない領域に凹部を有する

半導体装置。

【請求項10】

請求項6乃至請求項9のいずれかに記載の半導体装置であって、

前記所定の金属は、Cuを含む

半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【公開番号】特開2007−184347(P2007−184347A)

【公開日】平成19年7月19日(2007.7.19)

【国際特許分類】

【出願番号】特願2006−470(P2006−470)

【出願日】平成18年1月5日(2006.1.5)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

【公開日】平成19年7月19日(2007.7.19)

【国際特許分類】

【出願日】平成18年1月5日(2006.1.5)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

[ Back to top ]