Fターム[5F033PP15]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | PVD(物理的気相成長法) (5,261) | スパッタ (4,083)

Fターム[5F033PP15]の下位に属するFターム

反応性スパッタ (196)

バイアススパッタ (67)

高温スパッタ、リフロースパッタ (56)

Fターム[5F033PP15]に分類される特許

1 - 20 / 3,764

Cu層形成方法及び半導体装置の製造方法

リフロー法及び半導体装置の製造方法

半導体装置およびその製造方法

半導体ウェハ、半導体装置及びその製造方法

半導体ウェハ、半導体装置及びその製造方法

半導体装置及びその製造方法

半導体装置、半導体装置の製造方法、および電子機器

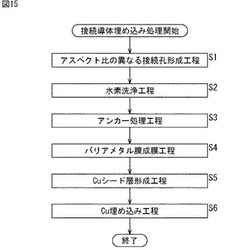

【課題】アスペクト比の異なる複数の開口下部に接続される配線に対して最適な処理を施すことができるようにする。

【解決手段】半導体装置の製造方法において、第1の半導体基板と第2の半導体基板が接合された半導体基板の第1の開口の下部配線と、貫通接続孔と異なるアスペクト比の第2の開口の下部配線に対して、バリアメタル膜の成膜と、スパッタガスによる物理エッチングを同時に行うアンカー処理工程が含まれる。本技術は、例えば、固体撮像装置などの半導体装置に適用できる。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極の形成時スループットやコスト悪化を回避する。

【解決手段】シリコン基板1に、貫通電極用のホール26を形成する。さらにホール26

上を含んで絶縁膜22,23をエッチングして溝35を形成する。この後、バリアメタル

層41とシード層42を積層させてから、CMP法による研磨でホール26の内壁及び溝

35内のみにシード層42を残す。シリコン基板1をめっき槽に浸漬させ、溝35を介し

てホール26内に電流を供給すると、ホール26内と溝35のみにCu膜47が成長する

。

(もっと読む)

半導体装置およびその製造方法ならびに表示装置および電子機器

【課題】配線層の膜応力を低減し、製造歩留まりを向上することが可能な半導体装置およびその製造方法並びに表示装置および電子機器を提供する。

【解決手段】本技術の半導体装置は、一方向に延在する複数の第1配線層と、第1配線層の間に設けられた第1配線層よりも膜厚が薄いゲート電極と、第1配線層およびゲート電極上に形成された絶縁膜と、絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、半導体層上に設けられた層間膜と、層間膜上に形成されると共に、層間膜に設けられた貫通孔を介して半導体層と接続された第2配線層とを備えている。

(もっと読む)

半導体装置の設計方法、半導体装置の製造方法および半導体装置

【課題】半導体装置の性能を向上させる。

【解決手段】半導体装置の設計フローは、プラグPGに接続された配線M1を含むチップレイアウトを設計するステップと、設計されたチップレイアウトにおけるプラグPGに対する配線M1のマージンを、プラグPGに対する配線M1のリセス量に応じて修正するステップとを有している。この修正ステップは、テストウエハに試験用プラグとそれに3次元的に接続された試験用配線とを含むテストパターンを形成するサブステップと、試験用配線の配線幅および配線密度と試験用プラグに対する試験用配線のリセス量との相関を調べるサブステップを有している。更に、得られた相関に基づいてプラグPGに対する配線M1のリセス量を予測するサブステップと、予測されたリセス量に応じてプラグPGに対する配線M1のマージンを修正するサブステップを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】下層の銅配線と上層のアルミニウム配線とを接続するコンタクトプラグのコンタクト抵抗を均一化する。

【解決手段】銅配線8と、銅配線9上の層間絶縁膜10と、層間絶縁膜10上に形成されたアルミニウム配線17と、銅配線9とアルミニウム配線17とを電気的に接続するプラグ13とを備える半導体装置であって、プラグ13は銅とアルミニウムの合金からなり、銅配線9上のコンタクトホールにバリアメタルを設けずに第1のアルミニウム膜を充填し、熱処理して合金化し、未反応の第1のアルミニウム膜を除去した後、アルミニウム配線用の第2のアルミニウム膜を成膜する。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜上に良質のグラフェンを形成しうる半導体装置の製造方法を提供する。

【解決手段】第1の基板上に触媒金属膜を形成する工程と、触媒金属膜を触媒としてグラフェンを形成する工程と、グラフェン上に第1の絶縁膜を形成する工程と、第1の絶縁膜上に第1の金属膜を形成する工程と、第2の基板上に、第2の金属膜を形成する工程と、第1の金属膜の表面と第2の金属膜の表面とを対向させ、第1の金属膜と第2の金属膜とを接合する工程と、第1の基板を除去する工程とを有する。

(もっと読む)

ラインエッジ粗さを低減させた特徴のエッチング

【課題】ラインエッジ粗さを低減させて特徴をエッチングする

【解決手段】ラインエッジ粗さを低減させて層内に特徴を形成するための方法が提供される。層の上に、フォトレジスト層が形成される。フォトレジスト層は、フォトレジスト側壁をともなうフォトレジスト特徴を形成するために、パターン形成される。複数のサイクルを実施することによって、フォトレジスト特徴の側壁の上に、厚さ100nm未満の側壁層が形成される。各サイクルは、単分子層から20nmまでの厚さを有する層をフォトレジスト層上に堆積させることを含む。フォトレジスト特徴を通して、層内に特徴がエッチングされる。フォトレジスト層および側壁層は、剥ぎ取られる。

(もっと読む)

半導体装置の製造方法

【課題】接続孔部分における電気的特性のばらつきを低減することにより、半導体装置の信頼性および製造歩留まりを向上させることのできる技術を提供する。

【解決手段】成膜装置のドライクリーニング処理用のチャンバ57に備わるウエハステージ57a上に半導体ウエハSWを置いた後、還元ガスを供給して半導体ウエハSWの主面上をドライクリーニング処理し、続いて180℃に維持されたシャワーヘッド57cにより半導体ウエハSWを100から150℃の第1の温度で熱処理する。次いで半導体ウエハSWをチャンバ57から熱処理用のチャンバへ真空搬送した後、そのチャンバ57において150から400℃の第2の温度で半導体ウエハSWを熱処理することにより、半導体ウエハSWの主面上に残留する生成物を除去する。

(もっと読む)

半導体集積回路装置

【課題】チップあたりの端子数の増大に伴って、フリップチップ実装が種々の形態で実施されている。しかし、バンプピッチの微細化およびバンプの鉛フリー化によって、エレクトロマイグレーション耐性の確保がますます重要となっている。

【解決手段】本願の発明は、フリップチップ型の半導体集積回路装置において、チップの第1の主面上に形成された多数のUBMパッド状の各々に設けられた半田バンプの中間部には、上下を分割する前記半田バンプとは異なる材質の金属隔壁が設けられているものである。

(もっと読む)

半導体ウェハ、半導体装置及びその製造方法

【課題】アライメントマークに集中する応力の方向依存性を低減して、クラックを発生しにくくする。

【解決手段】基板の第1の主面に、環状の第1の溝及びドット形状の第2の溝を形成する。第1及び第2の溝を埋め込むように絶縁膜を形成した後、基板の第1の主面にフォトレジスト膜を形成する。絶縁膜で埋め込まれた第2の溝の基板上での位置を基準として位置合わせした第1のパターンを、フォトレジスト膜に転写する。絶縁膜で埋め込まれた環状の第1の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する。

(もっと読む)

貫通電極基板の製造方法

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板の製造方法は、ウェハ状の基板に前記基板を貫通しない複数の有底孔を形成し、前記基板及び前記有底孔の表面に絶縁膜を形成し、前記有底孔が開口する側の前記基板及び前記有底孔の絶縁膜上に金属からなるシード膜を形成し、前記シード膜に第1の時間直流電流を供給する電解めっき法により、前記シード層が形成されている面の前記有底孔の底部に金属層を形成し、前記シード膜及び前記金属層にパルス電流を供給する電解めっき法により、前記有底孔内に金属材料を充填して導通部を形成し、前記有底孔が形成されている側と反対側の前記基板の表面を、前記導通部の表面が露出するまで研磨する。

(もっと読む)

半導体装置、及びその製造方法

【課題】TSV付き半導体装置において、貫通孔側面すべてにバリア及びシード層を成膜しないことで、空隙の発生を防止する。

【解決手段】

第1の溝部、及び前記第1の溝部より水平断面積が小さい第2の溝部からなる凸状溝部を画成し、且つ、前記第1及び第2の溝部により両端を開口する貫通ビアホールが形成される半導体基板と、前記第1の溝部の内面から、前記第2の溝部の側面の一部まで被覆して、前記貫通ビアホールの側面に隆起するバリア層およびシード層と、前記シード層の表面上、及び、前記シード層で被覆されていない前記第2の溝部内部に形成されて、前記半導体基板の両表面から露出する電極と、を備える半導体装置が提供される。

(もっと読む)

半導体装置およびその製造方法、電子部品

【課題】貫通電極の微細化と表面電極の縮小化とを両立することができる半導体装置、および表面電極の大きさに関わらず、表面電極に対して貫通電極を確実にコンタクトさせることができる半導体装置の製造方法を提供すること。

【解決手段】Si基板29の表面13に複数の絶縁膜リング32を選択的に形成し、絶縁膜リング32の開口42に対向するように表面パッド33を形成する。次に、Si基板29を裏面14からエッチングすることにより、絶縁膜リング32の開口42を通過して表面パッド33に達する貫通孔56を形成し、貫通孔56の側面にビア絶縁膜35を形成した後、貫通孔56に電極材料を充填することにより、表面パッド33に電気的に接続されるように貫通電極17を形成する。

(もっと読む)

半導体装置およびその製造方法、電子部品

【課題】貫通電極におけるボイドの発生を防止することができ、従来に比べて信頼性の高い半導体装置およびその製造方法、ならびに電子部品を提供すること。

【解決手段】Si基板29上のゲート絶縁膜30上に電極層51を形成する。ゲート絶縁膜30上に層間絶縁膜31を形成した後、ダマシン法により電極層51と同一パターンの下側配線42と、反対パターンの下側絶縁膜43を含む下側パッド40を形成する。次に、貫通孔59を形成し、同時に、貫通孔59内に下側絶縁膜43と同一パターンの突出部60が形成された第1層間絶縁膜32を露出させる。そして、突出部60の一部がエッチング残渣として残るように第1層間絶縁膜32をエッチングした後、ビア絶縁膜38を形成し、貫通孔59の底面のビア絶縁膜38をエッチングする。次に、貫通孔59のビア絶縁膜38の内側に電極材料をめっき成長させることにより、貫通電極17を形成する。

(もっと読む)

1 - 20 / 3,764

[ Back to top ]