Fターム[5F033VV10]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | 受動素子 (1,084) | 容量 (664)

Fターム[5F033VV10]に分類される特許

201 - 220 / 664

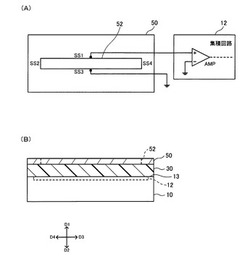

半導体装置及び電子機器

【課題】アンテナが半導体チップの回路に及ぼす悪影響を最小限に抑えることができる半導体装置、電子機器の提供。

【解決手段】半導体装置は、集積回路12が形成される半導体チップ10と、少なくとも1つのスロット52を有し、半導体チップ10の主面13に直交する方向を第1の方向D1とした場合に半導体チップ10の第1の方向D1に少なくとも絶縁層30を介して設けられ、半導体チップ10の集積回路12に電気的に接続されるスロットアンテナ50と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 1つの半導体チップに半導体集積回路部分と可動部を有する可動部分とを作り込んだMEMS構造を有し、チップの縮小化が可能になると共に動作感知と動作方向検知とが可能になる半導体装置及びその製造方法を提供する。

【解決手段】 MEMS部分の可動部10は、半導体層13上の梁28の上に形成される。梁28は絶縁膜26及びポリシリコン膜27から構成され、抵抗等を利用できる。可動部10は、層間絶縁膜8、14に形成された凹部6に配置され、下端が梁28のポリシリコン膜27に接合され、上端はフリーである。梁28が形成された部分には空洞7が形成されており、更に梁部分は中空構造になっている。可動部10は、チップの加速によって応力を受けて先端部が移動する。チップの移動により、可動部10と各電極91〜98との間の空間の距離が変化し、各電極と可動部10との間の容量の変化を検出することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体装置を提供する。

【解決手段】半導体基板101と、前記半導体基板の上方に設けられた、誘電体膜116を下部電極115と上部電極117とで挟んでなるキャパシタと、を備え、前記下部電極は、貴金属膜115aと、前記貴金属膜上に島状に複数形成された導電性酸化物膜115bと、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ダマシンプロセスで下部電極を形成する場合に高密度金属配線においても、エロージョンを抑制し、下部電極の平坦性を確保できるMIMキャパシタを備えた半導体装置及びその製造方法を提供する。

【解決手段】MIMキャパシタを備える半導体装置であって、MIMキャパシタは、半導体基板1上に形成された第1絶縁膜2と、第1絶縁膜2上の所定領域に埋め込まれ、前記第1絶縁膜に比べて研磨速度の遅い材料からなる第1導電膜4と、第1導電膜4を貫通して第1絶縁膜2に突出する複数の溝5bと、溝5bに埋め込まれた複数の金属配線8bと、金属配線8b上と第1導電膜4上に形成された誘電体膜11と、誘電体膜11上に形成された第2導電膜12とを備え、金属配線8bと第1導電膜4を電気的に導通して下部電極を構成するとともに、第2導電膜12にて上部電極を構成する。

(もっと読む)

半導体装置

【課題】SoCにDRAMを混載する場合に、プロセス、特性に影響することなく十分な容量のキャパシタを形成することが可能な半導体装置を提供する。

【解決手段】半導体基板11に形成され、素子分離されたトランジスタ領域と、半導体基板11上に形成された第1の層間膜19と、第1の層間膜19に形成され、それぞれトランジスタ領域に接続される第1および第2のコンタクトプラグ20、21と、第1のコンタクトプラグ20中に形成され、電極層22a/絶縁層22b/Cu層22cより構成されるMIM構造を有する第1のキャパシタと、第2のコンタクトプラグ21と接続されるビット線29を備える。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】コンタクトホールを容易且つ確実に効率よく形成することができる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】水素バリア膜7に、配線層9と、MOSトランジスタTのゲート電極3、ソース電極及びドレイン電極とを接続する第一のコンタクトホールH1を通すための除去領域7Aを形成し、この除去領域7Aの内側に、第一のコンタクトホールH1を形成する。

(もっと読む)

半導体装置の製造方法

【課題】強誘電体キャパシタを備えた半導体装置の歩留まりを改善することが可能な半導体装置の製造方法を提供すること。

【解決手段】シリコン基板20の上方に第1層間絶縁膜31を形成する工程と、第1層間絶縁膜31の上に、下部電極41a、強誘電体材料よりなるキャパシタ誘電体膜42a、及び導電性酸化物よりなる上部電極43aをこの順に積層してなるキャパシタQを形成する工程と、キャパシタQを覆う第2層間絶縁膜54を形成する工程と、上部電極43aの上の第2層間絶縁膜54に、該上部電極43aが露出するホール54aを形成する工程と、ホール54a内に、上部電極43aと接続された導電性窒化物よりなる単層のグルー膜58をスパッタ法で形成する工程と、グルー膜58をアニールする工程と、ホール54a内のグルー膜58上に導電性プラグ59aを形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置とその製造方法

【課題】水素等の還元性物質からキャパシタ誘電体膜を効果的に保護できる半導体装置とその製造方法を提供すること。

【解決手段】シリコン基板10の上方に形成された第1絶縁膜20と、第1絶縁膜20の上に形成された強誘電体キャパシタQと、キャパシタQを覆う第1絶縁性水素バリア膜31及び第2絶縁性水素バリア膜32と、第2絶縁性水素バリア膜32の上に形成され、前記第1、第2絶縁性水素バリア膜31、32を貫くホール46を上部電極28aの上に備えた第2絶縁膜33と、ホール46内に形成されて上部電極28aと電気的に接続された導電性部材47とを有し、所定のエッチングガスに対し、第2絶縁性水素バリア膜32のエッチング速度が第1絶縁性水素バリア膜31のエッチング速度よりも速いことを特徴とする半導体装置による。

(もっと読む)

半導体装置、及びその製造方法

【課題】特性を低下させることなく歩留まりを向上させた半導体装置、及びその製造方法を提供する。

【解決手段】半導体装置100は、基板10と、基板10上に形成された第1絶縁層33と、第1絶縁層33を貫通して形成された株コンタクトホール34、下部コンタクトホール34の内部に第1絶縁層33の表面まで形成された第1プラグ電極35、第1プラグ電極35上の第1領域Aに形成されたキャパシタ層、第1プラグ電極35上の第1領域Aと異なる第2領域Bに形成された第2プラグ電極39を備える。キャパシタ層は、順次積層された下部電極15、強誘電体膜16、及び上部電極17を有する。第1プラグ電極35は、基板10の表面から形成されたプラグ導電層351、プラグ導電層351上から第1絶縁層33の上面まで形成され且つ下部電極15よりもエッチングに対する選択比が高いプラグバリア層352を有する。

(もっと読む)

半導体記憶装置及び半導体記憶装置の製造方法

【課題】開孔歩留まりの低下を抑制可能なコンタクトプラグを有する半導体記憶装置を提供する。

【解決手段】半導体基板11の表面に形成された拡散層16を有するトランジスタ15、トランジスタ15の上方に配置された強誘電体キャパシタ30、強誘電体キャパシタ30の上方に配置された配線部50、拡散層16と強誘電体キャパシタ30と配線部50とをそれぞれ接続するコンタクトプラグ25、41、43、及び、強誘電体キャパシタ30を保護する下部の水素バリア膜21、上部の水素バリア膜37を有して、拡散層16と配線部50とを接続するコンタクトプラグ43は、上部の層間絶縁膜39、及び、下部の半導体基板11の表面に接して連続して形成された水素バリア膜21、37が開孔されて形成されている。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、配線の抵抗を高めることなく容量素子で発生した短絡に起因する配線の溶断を防止することができなかった。

【解決手段】本発明にかかる半導体装置は、互いに平行に配置される複数の第1配線11と、複数の第1配線11のそれぞれと直交し、互いに平行に配置される複数の第2配線12とを有する半導体装置であって、半導体装置は、複数の第1配線11のいずれか一つに接続される下部電極24と、複数の第2配線12のいずれか一つに接続される上部電極21と、下部電極24と上部電極21との間に形成される容量膜23とを備える容量素子20を有し、上部電極21と下部電極24とのうち少なくとも一方の電極は、その一部の領域に前記電極の幅が前記一部の領域以外よりも狭い幅狭部22を有するものである。

(もっと読む)

半導体装置

【課題】半導体基板の近くにインダクタが配置されるときにも、半導体基板の内部インダクタのインダクタンスに影響を与え難い半導体装置を提供する。

【解決手段】半導体基板2と、半導体基板2に形成される絶縁膜3と、絶縁膜3上に形成されるインダクタ7と、を備える半導体装置1にかかり、半導体基板2上には内部インダクタ9が形成され、内部インダクタ9と対向する場所には、インダクタ7が放出する磁力線を減衰させる内部用シールド膜5を有し、内部インダクタ9が内部用シールド膜5により変化するインダクタンスを補正する補正インダクタ6を有することを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】

ビルディングブロック方式では、電源ライン及びグランドラインの配置によって、半導体集積回路装置の微細化が困難であった。

【解決手段】

アナログ信号処理機能を担う電子回路ブロックが集積化された半導体集積回路装置であって、電源ラインは、電子回路ブロックを構成する半導体素子上の領域を含んで配置され、グランドラインは、電子回路ブロック間に位置する分離領域上に形成され、グランドラインは、コンタクト孔において分離領域とコンタクトされる。

(もっと読む)

半導体装置及びその製造方法

【課題】誘電体メモリの微細化が進むと、上部電極の電位を拡散層へ引き出す構造におけるアスペクト比が大きくなるため、上部電極のカバレッジが悪化し、誘電体を結晶化させる熱処理時に上部電極が断線してしまう。

【解決手段】半導体装置は、半導体基板の上方に形成された第1の導電膜及び第2の導電膜と、第1の導電膜を覆うように形成された第1の絶縁膜と、第2の導電膜を覆うように形成された第2の絶縁膜と、第1の絶縁膜に形成され、第1の導電膜に達する第1の開口部と、第1の開口部の壁部及び底部に沿って形成された第3の導電膜と、第3の導電膜、第1の絶縁膜、及び第2の絶縁膜上に形成された誘電体膜と、第2の絶縁膜及び誘電体膜の積層膜に形成され、第2の導電膜に達する第2の開口部と、誘電体膜の上並びに第2の開口部の壁部及び底部に沿って形成された第4の導電膜とを備える。第2の絶縁膜の膜厚が、第1の絶縁膜の膜厚よりも薄い。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体膜の劣化を防止する。

【解決手段】本発明の半導体装置1は、基板21上方に順次設けられた第1電極32、強誘電体膜33、及び第2電極34を有する強誘電体キャパシタ3と、強誘電体キャパシタ3の上面及び側面を覆う水素バリア膜4と、水素バリア膜4及び基板21を覆う層間絶縁膜6と、層間絶縁膜6及び水素バリア膜4を貫通して第2電極34を露出させるコンタクトホール70と、第2電極34上を含むコンタクトホール70の内壁面70aを覆い、水素バリア性を有する導電材料からなるバリアメタル75と、コンタクトホール70内に埋設されたプラグ導電部7と、を備えている。水素バリア膜4におけるコンタクトホール70の内壁面は、コンタクトホール70の内側に向かって凹となる湾曲面となっており、水素バリア膜4におけるコンタクトホール70の内径は第2電極34に向かって小さくなる。

(もっと読む)

強誘電体メモリ装置の製造方法及び強誘電体メモリ装置

【課題】強誘電体材料において酸素欠損が発生することをより確実に防止できる強誘電体メモリ装置の製造方法及び強誘電体メモリ装置を提供すること。

【解決手段】半導体基板上に強誘電体キャパシタ3を形成する工程と、強誘電体キャパシタ3を被覆する水素バリア膜12を形成する工程と、水素バリア膜12に貫通孔21を形成する工程と、強誘電体キャパシタ3及び水素バリア膜12を被覆する第2層間絶縁膜13を形成する工程と、第2層間絶縁膜13に貫通孔21を形成する工程と、貫通孔21の内壁面及び強誘電体キャパシタ3の上面それぞれに密着層24を形成する工程と、貫通孔21内にプラグを形成する工程とを備え、貫通孔21が、貫通孔21の内側に形成されると共に、貫通孔21の内壁面が、被覆層24で被覆される。

(もっと読む)

強誘電体メモリ装置の製造方法

【課題】水素バリア膜の下層との間においてエッチングの十分な選択比が得られると共に、コンタクトホールの形成工程を簡略化した強誘電体メモリ装置の製造方法を提供すること。

【解決手段】半導体基板上に強誘電体キャパシタ3を形成する工程と、強誘電体キャパシタ3を被覆する水素バリア膜12を形成する工程と、水素バリア膜12を被覆する層間絶縁膜13を形成する工程と、C4F8ガススとO2ガスとを少なくとも含む混合ガスを用いたエッチングにより層間絶縁膜13及び水素バリア膜12を貫通する貫通孔21を形成する工程とを備え、C4F8ガスの流量がO2ガスの流量に対して0.77倍以上3.8倍以下である。

(もっと読む)

半導体装置

【課題】絶縁膜上に形成した素子に対する寄生容量の影響を低減することが可能な技術を提供することを目的とする。

【解決手段】P型の半導体基板1の表面にN型のエピタキシャル層2が形成されている。エピタキシャル層2を複数の島領域に分離するためのP+分離層3が形成されている。P+分離層3の表面にはN−不純物層4が形成されている。N−不純物層4上にはフィールド絶縁膜5が形成され、当該フィールド絶縁膜5上には下部電極6が形成されている。下部電極6上には絶縁膜7を介して上部電極8が形成され、容量9が形成されている。絶縁膜7や上部電極8上には絶縁膜10が形成されている。絶縁膜10には、上部電極8及び下部電極6のそれぞれに至るコンタクトホール11a,11bが形成され、各コンタクトホール内には配線層12a,12bが形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体キャパシタの特性ばらつきを低減する。

【解決手段】本発明の製造方法は、基体上に第1電極32と強誘電体膜33と第2電極34とが順次積層された強誘電体キャパシタ3を形成する工程と、強誘電体キャパシタ3及び前記基体を覆って第1層間絶縁膜5を形成する工程と、第1層間絶縁膜5を覆って第2層間絶縁膜6の材料膜61を形成する工程と、材料膜61の上面側をCMP法で研磨することにより、強誘電体キャパシタ3上に位置する第1層間絶縁膜5を露出させる工程と、第1層間絶縁膜5を露出させる工程の後に、第1層間絶縁膜5を貫通して第2電極34を露出させるコンタクトホール70を形成する工程と、コンタクトホール70内に、第2電極34と導通するプラグ導電部を形成する工程と、を有する。第1層間絶縁膜5は、第2層間絶縁膜6と比して、CMP法による研磨速度が遅くなるようにする。

(もっと読む)

半導体装置、表示装置及びそれらの製造方法

【課題】耐熱性や接合強度等の信頼性を高めることができるとともに、高い生産性を得ることができる半導体装置、表示装置及びそれらの製造方法を提供する。

【解決手段】基板上に半導体素子を有する半導体装置であって、上記基板は、半導体素子が配置されている側の面に凸部を有し、上記半導体素子は、基板の凸部の上面に配置されている半導体装置、及び、上記半導体装置の製造方法であって、上記製造方法は、半導体素子又はその構成要素を基板の凸部の上面に転写する工程を含む半導体装置の製造方法。

(もっと読む)

201 - 220 / 664

[ Back to top ]