Fターム[5F033XX27]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 信号の遅延防止、伝達の同時化 (255)

Fターム[5F033XX27]に分類される特許

201 - 220 / 255

半導体装置、半導体本体並びにその製造方法

この発明は、内部にICが形成され、表面上にICのための多くの接続領域(1)を有し、少なくとも二つの接続領域(1A)が供給接続のためである半導体本体(11)を備えた半導体装置(10)であって、半導体本体(11)の下側に多くのさらなる電気的接続領域(2)が設けられ、これらは、半導体本体(11)の側面上に存在し、そこから電気的に絶縁されている電気的接続部(3)により接続領域(1)に接続され、半導体本体(11)はリードフレーム(4)に固定され、ワイヤ接続部(5)がリードフレーム(4)のリード(4A)と接続領域(1)との間に形成されている。この発明によれば、電気的接続部(3)は複数の平行で、等間隔で配置されたストリップ状導体(3A)を備え、そして、供給接続のための接続領域(1A)が、各々、二つ又はそれ以上のストリップ状導体(3A)により、さらなる接続領域(2)に接続され、このさらなる接続領域は直接フレーム(4)のリード(4B)に接続され、接続領域の残部(1B)はワイヤ接続部(5)により直接リード(4)に接続される。このような装置(10)は供給電圧が非常に安定であり、高周波での動作に優れており、供給電流も非常に大きくなる。この発明は、さらに、そのような装置(10)に用いるのに適した半導体本体(11)とそのような装置(10)を製造する方法を備える。  (もっと読む)

(もっと読む)

バリアで内側が覆われた半導体コンポーネントを製造する方法

薄い共形のマルチ層バリア構造を含むメタライゼーションシステムを有する半導体コンポーネント(10)およびこの半導体コンポーネント(10)を製造する方法である。下にある階層の相互接続構造上に絶縁材料(30)(34)を形成する。この絶縁材料(30)(34)上にハードマスク(36)を形成し、このハードマスク(36)を貫通して絶縁層(30)(34)中に開口部(50)(52)(54)をエッチングする。この開口部(50)(52)(54)を、原子層たい積を使用して薄い共形のマルチ層バリア(60)でその内側を覆う。このマルチ層バリアで内側が覆われた開口部を導電材料(66)で充てんする。この導電材料(66)はプレーナ化される。  (もっと読む)

(もっと読む)

半導体装置

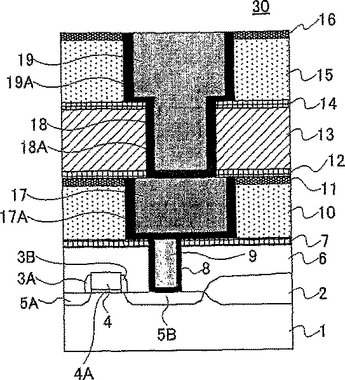

【課題】製造工程中にけるスループットの低下や膜剥がれ変形などの不具合を生じさせることなく、配線性能の向上をも図ることが可能な多層埋め込み配線構造を有する半導体装置を提供する。

【解決手段】層間絶縁膜の表面側に設けられた配線溝aと配線溝aの底部に設けられた接続孔bとの内部を導電性材料で埋め込んでなる埋め込み配線26aおよびヴィア26bを備えた配線層20-1,20-2,…を、基板の上部に複数層積層してなる多層配線構造の半導体装置であって、複数の配線層配線層20-1,20-2,…を構成する層間絶縁膜の機械的強度の強弱が、配線層20-1,20-2,…の積層方向において配線層20-1,20-2,…毎に交互となるように、各層間絶縁膜が構成されている。

(もっと読む)

絶縁膜、絶縁膜の形成方法、半導体素子、電子デバイスおよび電子機器

【課題】所望の比誘電率を有し、機械的強度に優れる絶縁膜、この絶縁膜を容易に形成し得る絶縁膜の形成方法、この絶縁膜を備える半導体素子、電子デバイスおよび電子機器を提供すること。

【解決手段】本発明の絶縁膜は、導電体同士を絶縁するものであって、絶縁性基材42中に、当該絶縁膜の膜強度を向上させる絶縁性粒子41を含有してなるものである。この絶縁膜は、絶縁性粒子41として、絶縁性基材42の比誘電率と異なる比誘電率の粒子を用いることにより、その比誘電率を調整したものである。例えば、絶縁性粒子41として、絶縁性基材42の比誘電率より低い比誘電率の粒子を用いることにより、絶縁膜全体の比誘電率を調整(低下)することができ、かかる絶縁膜は、層間絶縁膜に好適に適用される。

(もっと読む)

半導体装置およびその製造方法

【課題】

従来のアルミ配線の場合、上述の横応力がアルミ配線にかかり、次第にアルミ配線が傾く。さらに、大きな応力を受けると配線が根元からスライドし、クラックが入るなどして、期待する特性を得られなくなることがある。

【解決手段】

第1の厚さを有する周辺部及び第1の厚さよりも薄い第2の厚さを有する配線形成部を有し、底面が同一である半導体基板10と、半導体基板10の配線形成部上に形成されたアルミ配線層と、を有し、配線形成部が前記周辺部に隣接して配置されている半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】複数の異なる半導体チップ間を貫通電極を用いて最短の配線長で三次元的に接続し、低ノイズな高速動作を可能とする方法を提供する。

【解決手段】異なる上下の半導体チップ1a〜fの中間に上下チップ間を接続するためのインターポーザチップ11を配した三次元のチップ積層構造において、デバイス側(表層側)外部電極部に相当する裏面位置に、ドライエッチングにより表層電極に達するまでの孔を形成し、孔の側壁及び裏面側周囲に金属製のメッキ膜を施し、前記金属製のメッキ膜が施された貫通孔内部に、上段側に積層される別の半導体チップの金属製バンプを圧接によって変形注入させ、半導体チップ内に形成された貫通孔内部に前記金属製バンプを幾何学的にかしめて電気的に接続させる。

【効果】非常に低コスト・短TATなプロセスで接続が可能であり、常温接合が可能で、高い信頼性の接続構造を実現する。

(もっと読む)

低誘電率絶縁膜および半導体装置の製造方法

【課題】 半導体装置を構成する絶縁膜の比誘電率を低下させることができる方法を提供する。

【解決手段】 半導体装置を構成する絶縁膜2に不活性ガス、窒素および水素の内の少なくとも一種のイオン6を注入して絶縁膜2中に多数の空隙8を形成し、絶縁膜2の比誘電率をイオン注入前よりも低下させ、これによって低誘電率絶縁膜10を得る。

(もっと読む)

局所接続・導電ラインを形成する方法及びその構造体

【課題】局部接続を含む半導体集積回路及びその製造方法を提供する。

【解決手段】半導体基板の上に対向する側壁を有する導電ライン22,24,26を形成する。絶縁層34を堆積し、該絶縁層を、ラインの少なくとも一つの側壁の少なくとも一部分に沿ってエッチングする。絶縁スペーサ47,48,49,50,52を形成する。局所接続層56を導電ラインの少なくとも一部分上に横たわるように形成し、基板材料位置42,43,44を電気的に接続する。局所接続層内に導電性増強不純物の浅い注入と深い注入を行う。導電性増強不純物を局所接続層からその下の半導体基板材料内に拡散する。

(もっと読む)

低誘電率を有するシリコン酸化物をベースとする材料を生成する方法

本発明は、低誘電率を有する材料(60)を生成する方法に関し、ヘリウム及びネオン以外の希ガスの注入で二酸化ケイ素中に空孔(66)を形成するステップを含む。本発明は、また、1016原子/cm2 より多い注入量でのヘリウム及びネオン以外の希ガスの注入により形成された空孔(66)を有し、低誘電率を有する二酸化ケイ素を含む領域が互いを隔てるところの複数の金属トラックを備える素子に関する。  (もっと読む)

(もっと読む)

局所接続・導電ラインを形成する方法及びその構造体

【課題】局部接続を含む半導体集積回路及び局部接続を含む半導体集積回路の製造方法を提供する。

【解決手段】フィールド絶縁領域64及び活性エリア領域62が、半導体基板12上に形成される。トレンチが、フィールド絶縁材料66内に所望のライン形状となるようにエッチングされる。導電性材料は、トレンチを少なくとも一部分充填し、その中に導電ラインを形成するように堆積される。フィールド絶縁材料66はLOCOS酸化膜を有するように形成される。

(もっと読む)

電子部品用金属材料、電子部品、電子機器、金属材料の加工方法、電子部品の製造方法及び電子光学部品

【課題】 本発明は、電子部品および電子機器またはそれらの製品に使用される金属合金材料、電子および金属材料の加工方法及び電子光学部品に関し、例えば液晶表示素子、各種半導体製品あるいは部品、プリント配線基板、その他のICチップ部品等に適用して、従来に比して低抵抗率であり、更に製造工程中での優位性を保有した安定かつ加工性に優れた電子部品用金属合金材料、この金属材料を使用した電子部品、電子機器を提供する。

【解決手段】 Cuを主成分とし、Wを0.1〜7.0wt%含有し、Al、Au、Ag、Ti、Ni、Co、Siからなる群から選ばれた1又は複数の元素を合計で0.1〜3.0wt%含有してなる合金を金属材料として適用する。この金属材料によれば、CuにWを添加してCuの粒界にMoを均質に混入させることにより、Cu全体の耐候性を向上させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】 低誘電率絶縁体からなる層間絶縁膜を用いた半導体装置において、機械的及び熱的な耐性を向上できるようにする。

【解決手段】 半導体装置は、半導体基板10に形成された半導体素子と、半導体基板10の上方に形成され、半導体素子と電気的に接続された第1の配線41Aと、該第1の配線41Aの上方に誘電率が酸化シリコンよりも低い絶縁体からなる第3の層間絶縁膜23を介在させて形成された第2の配線42Aとを有している。さらに、半導体装置は、半導体基板10上における第1の配線41A又は第2の配線42Aの近傍領域に形成された第1のダミー配線41Bを有している。

(もっと読む)

半導体チップ及び半導体装置

【課題】 配線と半導体基板間の寄生容量を低減して、信号伝送の高速化や信号伝送時の消費電力の増大を防止できる半導体チップ及び半導体装置を提供する。

【解決手段】 半導体基板と、半導体基板に少なくとも一部が埋設された、伝送信号に応じて電流が流れる電流路となる配線と、配線の、半導体基板に埋設された部位を覆う絶縁膜と、半導体基板内に前記絶縁膜との界面から伸びる空乏層が形成されるように、半導体基板または配線にバイアス電圧を印加するための手段とを有する。または、絶縁膜を囲むように半導体基板内に形成される、半導体基板と導電型と異なる半導体層を有する構成とする。

(もっと読む)

半導体装置

多層配線構造を有する半導体装置において、Cuビアプラグ部への応力集中を抑制する多層配線構造を提供する。そのため、Cu配線部を含む第1の絶縁層と、前記基板上に形成された、前記Cu配線に電気的に接続されるCuビアプラグ部を含む第2の絶縁層とを有し、前記第1の絶縁層は弾性率が5GPa以上、硬度が0.6GPa以上である多孔質絶縁膜からなり、前記第2の絶縁層の弾性率が10GPa以上、硬度が1GPa以上であることを特徴とする半導体装置を用いる。  (もっと読む)

(もっと読む)

相互接続構造の金属エッチング方法およびそのような方法で得られた金属相互接続構造

金属相互接続構造であって、

基板(11)と、基板の上にある誘電体層(12)と、誘電体層の上にある金属エッチング用の停止層(13)と、停止層の上にある金属層(15’)とを備え、前記金属層が所望のパターンに従ってパターン形成される金属相互接続構造。  (もっと読む)

(もっと読む)

半導体集積回路装置の製造方法

【課題】半導体集積回路装置の高速化を図り、また、エレクトロマイグレーションやストレスマイグレーションの発生を抑え、配線寿命を長くする技術を提供する。

【解決手段】半導体基板1上に形成された酸化シリコン膜23および窒化シリコン膜22中の配線溝内を含む酸化シリコン膜23上にバリア層26aおよび銅膜26bを順次形成後、前記配線溝外部のバリア層26aおよび銅膜26bを除去することによって配線26を形成し、配線26上にタングステンを選択成長もしくは優先成長させることにより、配線26上にタングステン膜26cを形成する。

(もっと読む)

絶縁層の形成方法、熱処理装置及び記憶媒体

【課題】スループットを向上できると共に、比誘電率をより低減することが可能な絶縁層の形成方法を提供する。

【解決手段】被処理体Wの表面に、微少な空孔86が分散されている絶縁層88を形成する方法において、被処理体の表面に、空孔形成材料84が分散されている単量体、又は/及び有機低分子化合物を含む塗布膜82を形成する塗布膜形成工程と、複数枚の被処理体を、縦長の加熱可能になされた処理容器内で第1の温度帯域内の温度で加熱して所定の時間維持することにより前記単量体、又は/及び有機低分子化合物を一部重合させて骨格を形成する部分骨格形成工程と、引き続き前記処理容器内で前記複数枚の被処理体を、第1の温度帯域より高い第2の温度帯域内の温度に加熱して所定の時間維持することにより空孔形成材料を気化させて空孔を生ぜしめて絶縁層を形成する空孔形成工程とを有する。

(もっと読む)

積層配線デバイス及びその製造方法

【課題】 多層配線構造を有する積層配線デバイス及びその製造方法において、配線間の高い絶縁性を得ると共に信号遅延や信号交雑等の障害を回避すること。

【解決手段】 ベースウェーハ2と、ベースウェーハ2との間に中空領域8を形成して対向配置された封止ウェーハ6と、ベースウェーハ2上に導電性材料からなる第1配線層3a〜第5配線層3eが積層されて中空領域8内に設けられ上部が封止ウェーハ6に接合された積層配線部4と、を備えている。これにより、隣接する配線間に固体媒体が介在せず、非常に低い誘電率が得られる真空中又は不活性ガス等の気体によって配線間の絶縁を行うことができる。

(もっと読む)

半導体装置

【課題】銅ダマシン配線のエレクトロマイグレーション耐性の向上を図る。

【解決手段】本発明の例に関わる多層配線構造を有する半導体集積回路が形成される半導体装置は、銅配線14と、銅配線14の上面上に形成される絶縁層16とを備え、銅配線14は、銅配線14と絶縁層16との密着性を向上させる添加物を含み、その添加物のプロファイルは、銅配線14の上面から内部に向かうに従い、次第に濃度が減少する勾配を持ち、銅配線14の上面で最も高い濃度となる。

(もっと読む)

シリコンベータゼオライトを含んだ層間誘電体膜を調製するためのプロセス

シリコンウエハーなどの基板上に、ゼオライトベータ誘電体層を形成するためのプロセスが開発された。このゼオライトベータは、Si/Al比が少なくとも25であって、5〜40 nmの微結晶を有しているという点で特徴付けられる。このプロセスは、まず出発ゼオライトベータを脱アルミニウム化し、次にこの脱アルミニウム化ゼオライトベータのスラリーを調製し、続いてこのスラリーで例えばシリコンウエハーなどの基板を被覆し、加熱してゼオライトベータ膜を形成し、そしてシリル化剤でこのゼオライベータを処理するといった各ステップによって構成されている。 (もっと読む)

201 - 220 / 255

[ Back to top ]