Fターム[5F038AR19]の内容

Fターム[5F038AR19]に分類される特許

1 - 20 / 33

半導体装置の製造方法

【課題】エピ抵抗や抵抗チップを用いることなく、奇モードのループ発振を抑えること。

【解決手段】本発明は、金属層60を形成する工程と、複数のFETそれぞれのゲートフィンガー14を共通に接続するゲートバスライン26のパターンのうち一部分を除いたパターンを有するめっき層64と、一部分の領域を被覆する第2マスク層66と、をマスクにして金属層60をパターニングすることで、ゲートバスライン26を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体装置

【課題】半導体装置において、高電圧の配線層とその下方を横切るように配置された抵抗層との間の絶縁膜の耐圧を確保し、この配線層と抵抗層との間で破壊が起きるのを抑制することを目的とする。

【解決手段】第1半導体領域10に接続され第2半導体領域11上を通過するように第3配線層22が配置されている。第3配線層22と第2半導体領域11との間に配置される絶縁膜14内には、一端が第3配線層22に接続されると共に、他端が第1半導体領域11よりも電位の低い制御端子12に接続され、且つ第3配線層22とSOI層2との間において第3配線層22を少なくとも1回以上横切る構成で抵抗層25が配置されている。この抵抗層25は、第3配線層22を横切る部位の上面が他の部位よりも下方位置となるように段差状に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ(FUSE)を備えた半導体装置の信頼性を向上する。

【解決手段】半導体基板11の主面上に形成にされた多層配線を構成する層M1〜M6のうちの層M4に設けられた電気溶断型の救済用のヒューズ4aおよび試験用のヒューズ4bと、ヒューズ4aの近傍であって層M2および層M6に設けられた一対の導電板10aと、ヒューズ4bの近傍であって層M3および層M5に設けられた一対の導電板10bとから構成する。ヒューズ4bと導電板10bとの間が、ヒューズ4aと導電板10aとの間より近いものとする。

(もっと読む)

高周波デバイス

【課題】 渦電流や寄生容量の発生を抑制することができ、優れた高周波特性を示す小型の高周波デバイスを提供する。

【解決手段】 開口14を有する基板11上の誘電体層13にバンドパスフィルタBPFを備える。BPFは例えば第1誘導性素子L1および第1容量性素子C1の組と、第2誘導性素子L2および第2容量性素子C2の組と、第3誘導性素子L3および第3容量性素子C3の組とにより構成されている。開口14は第1誘導性素子L1に対向する位置に設けられている。基板11に対して開口14を設けることにより第1誘導性素子L1の直下での寄生容量および渦電流の発生が抑制され、これにより信号損失が低減されてフィルタ回路の特性が向上する。

(もっと読む)

半導体装置

【課題】抵抗値を調整可能な半導体装置をコンパクト化する。

【解決手段】基板接続領域と、外部配線接続領域と、基板接続領域と外部配線接続領域との間に設置される抵抗調整領域とを、1つの電極パッドに形成し、コンパクト化する。電極パッドの抵抗調整領域に対してトリミングを行うことによって、電極パッドの基板接続領域と外部配線接続領域との間の抵抗値を調整することができる。これによって、抵抗値を調整可能な半導体装置をコンパクト化することができる。

(もっと読む)

半導体装置

【課題】耐熱性に優れ、不均一動作が抑制される高周波高出力半導体装置を提供する。

【解決手段】半導体基板上に形成される複数の電界効果トランジスタが並列接続される単位セルを、さらに複数並列接続する半導体装置において、この単位セルを構成する電界効果トランジスタの複数のゲート電極同士を接続するゲートバス配線に接続され、複数の導電層が積層した構造を有するゲートパッド電極と、隣接するゲートパッド電極間同士を接続し、ゲートパッド電極外周部の少なくとも一辺に沿って形成され、ゲートパッド電極を構成する複数の導電層の少なくとも一つの導電層で形成される抵抗体とを有することを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】本発明は、配線抵抗成分をセンス抵抗として利用しながら、過電流保護回路の検出精度を向上することが可能な半導体装置を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、監視対象となる電流ラインの配線抵抗成分であるセンス抵抗Rsと、センス抵抗Rsでの降下電圧と所定の閾値電圧を比較して過電流保護信号Socpを生成する過電流保護回路OCPと、前記電流ラインの形成工程と同一の工程により、他の回路要素から電気的に分離して形成されたダミーラインの配線抵抗成分であって、センス抵抗Rsよりも大きな抵抗値を有するダミー抵抗Rdと;ダミー抵抗Rdの両端に各々接続されたダミーパッドT1、T2と;を集積化して成り、過電流保護回路OCPは、前記閾値電圧を調整するための閾値電圧調整部を有する構成とされている。

(もっと読む)

半導体集積回路装置

【課題】本発明は、電流検出精度の低下を抑制し安定した定電流制御を行う半導体集積回路装置を提供することを目的とする。

【解決手段】第1MOSトランジスタM1と、第2MOSトランジスタM2と、第1演算増幅器21と、第3MOSトランジスタM3と、第2演算増幅器22を有し、出力端子の電流を一定に制御する半導体集積回路装置であって、第2MOSトランジスタのドレイン配線の配線抵抗R2を位相補償容量C1と平面位置が同一の領域で位相補償容量を形成した第1層41と異なる第2層33に形成し、第1層と第2層との間に位置する第3層32に、位相補償容量の電極と対向し一定電圧を印加される電極43を形成した。

(もっと読む)

半導体集積回路装置における配線方法及び半導体集積回路装置

【課題】高速化を維持しつつ、レイアウトサイズを増大させることなしに配線間スキューを大幅に低減できる半導体集積回路装置の配線方法及び半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置において、第1コンポーネントと第2コンポーネントとを接続する信号線は、電気的に直列に接続された第1、第2、第3及び第4の部分を有する複数の第1の配線と、電気的に接続された第5及び第6の部分を有する複数の第2の配線とが交互に配置されて形成され、第2の部分の抵抗率は第1の抵抗率であり、第1、第3、第4、第5及び第6の部分の抵抗率は第1の抵抗率より低い第2または第3の抵抗率であって、且つ、第2の部分の抵抗値は複数の第1の配線ごとに異なり、複数の第1の配線は、配線長の和が小さい順に所定の位置から奇数番目に配置され、複数の第2の配線は、配線長の和が大きい順に前記所定の位置から偶数番目に配置される。

(もっと読む)

半導体装置、電気光学装置、及び電子機器

【課題】構造を複雑化させることなく安定した特性が得られ、さらには抵抗素子を含む回路の高集積化を実現できる半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、基板本体(基板)10Aと、基板本体10A上に形成された半導体素子(インバータINV1,INV2)と、半導体素子に接続された配線121,122と、配線121,122に形成された抵抗素子R1,R2とを備えており、配線121,122が、積層された複数の導電層131,132を有しており、異なる抵抗値を有する複数の抵抗素子R1,R2が、複数の導電層のうち少なくとも一部の導電層を用いて配線121,122に形成されていることを特徴とする。

(もっと読む)

電子基板及び電気光学装置並びに電子機器

【課題】高精度の抵抗部を容易に形成する。

【解決手段】基板P上に電極パッド及び配線パターン20、21が設けられる。配線パターンは、電極パッドの表面から樹脂突起の表面を越えて、電極パッドと逆側の方向に延び、且つ逆側において一部の配線諸元を、他の部分と異ならせて抵抗素子Rを形成する。

(もっと読む)

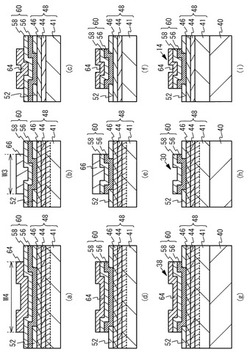

半導体装置およびその製造方法

【課題】抵抗素子として機能する配線を有し、かつ面積の小さな半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板SBと、半導体基板SB上に設けられた第2の配線層L2とを備えている。第2の配線層L2は、通常の配線WRと、高抵抗配線REと、通常の配線WRおよび高抵抗配線REを埋め込む絶縁膜8とを含んでいる。通常の配線WRは、第1の銅部10Wと、第1の銅部10Wの底面側および側面側を覆う第1のバリアメタル膜9Wとを有している。高抵抗配線REは、空洞部CVと、空洞部CVの底面側および側面側を覆う第2のバリアメタル膜19Rとを有している。

(もっと読む)

減衰器および電子デバイス

【課題】周波数特性に優れた、大電力の入力信号に対応できる、高減衰率の減衰器を提供する。

【解決手段】基板上に設けられた減衰器であって、信号の入力側の第1接点とグランドとの間に設けられた第1配線抵抗と、第1接点より信号の出力側の第2接点とグランドとの間に設けられた第2配線抵抗と、第1接点および第2接点の間に設けられた第3配線抵抗と、を備え、第1配線抵抗は、第2配線抵抗と比較して断面積が大きい、減衰器を提供する。

(もっと読む)

半導体装置

【課題】ESDから出力用のCMOS回路を確実に保護することができる半導体装置を提供する。

【解決手段】半導体装置1において、出力パッド6をNMOS5のドレインに接続する配線12に抵抗Rを付加する。これにより、出力パッド6からNMOS5を経由して低電位電源配線VSSに至る出力用NMOS経路の抵抗を、保護用NMOS7がスナップバックするような電圧が出力パッド6と低電位電源配線VSSとの間に印加されたときに、出力用NMOS経路に流れる電流がNMOS5の破壊電流よりも小さくなるような値とする。

(もっと読む)

半導体装置、電気光学装置並びに電子機器

【課題】構造を複雑化させることなく、安定した特性が得られる半導体装置を提供する。

【解決手段】本発明の半導体装置(第1基板)10は、絶縁層(下地絶縁膜)11と、前記絶縁層11上に設けられた薄膜トランジスタ30と、前記薄膜トランジスタ30に信号を供給するための配線(走査線)3aと、前記配線3aに設けられた抵抗素子107とを備え、前記配線3aは複数層の導電層131,132,133からなり、前記抵抗素子107は、前記複数層の導電層のうちの1又は2以上の導電層132,133を部分的に除去することにより形成されている。

(もっと読む)

半導体装置

【課題】キャパシタの信頼性や品質を確保しつつ、ウェハ工程完了後にキャパシタの容量を調整できる半導体装置を提供する。

【解決手段】容量調整用キャパシタを、同一の半導体基板に対して複数備え、容量調整用キャパシタがパッシベーション膜によって被覆された半導体装置であって、複数の容量調整用キャパシタは、同一層の電極間がそれぞれ層内繋ぎ配線によって連結されて1つのキャパシタブロックを構成しており、層内繋ぎ配線によって連結された各層の電極のうち、少なくとも1層の電極と当該電極間を繋ぐ層内繋ぎ配線とが、同一の導電材料からなる薄膜抵抗体として構成され、薄膜抵抗体のうち、層内繋ぎ配線に相当する部位の少なくとも1箇所に光を選択的に照射して部位を断線させることにより、キャパシタブロックの容量が調整可能である。

(もっと読む)

半導体装置

【課題】スパイラルインダクタの占有面積を小さくし、スパイラルインダクタの外力に対する強度を高める。

【解決手段】本発明に係る半導体装置は、スパイラルインダクタと他の回路が同一の半導体基板上に設けられた半導体装置であって、スパイラルインダクタは、互いに分割された第1の導体膜パターン及び第2の導体膜パターンと、第1の導体膜パターンと第2の導体膜パターンを直列に接続し、第1,第2の導体膜パターンよりも高抵抗である高抵抗配線とを有する。

(もっと読む)

オペレーション上の退化を反転する内蔵型加熱回路を有する集積回路

集積回路デバイス(100)は、使用に応じた性能劣化(例えば、フラッシュメモリセルのトンネル酸化物内で蓄積された欠陥、又は、電荷蓄積層内でトラップされた電荷)を示す構造(104)と、構造に近接して配置され、劣化を反転する温度に構造を加熱する加熱回路(101)とを備える。メモリデバイスのワード線又はビット線を加熱素子(107)として使用する。 (もっと読む)

電流検出装置及びこれを使用した電力供給装置

【課題】精度の高い電流検出装置を得ることが困難であった。

【解決手段】 本発明に従う電流検出装置は、被測定電流が流れる電流通路に接続され且つアルミニウムで形成された電流検出抵抗と、第1及び第2の入力端子を有し且つ第1の入力端子の信号と第2の入力端子の信号との差を示す出力を得るための出力端子を有する増幅器と、電流検出抵抗の一端と増幅器の前記第1の入力端子との間に接続され且つアルミニウムで形成された第1の入力抵抗と、

電流検出抵抗の他端と増幅器の第2の入力端子との間に接続され且つアルミニウム又はアルミニウムで形成された第2の入力抵抗と、増幅器の第2の入力端子と共通電源端子との間に接続された第3の入力抵抗と、増幅器の第1の入力端子と出力端子との間に接続された帰還抵抗とを有している。電流検出抵抗と第1及び第2の入力抵抗とは互いに同一の温度係数を有するので、電流検出精度が向上する。

(もっと読む)

半導体集積回路装置

【課題】制御される電流値の合わせ込みが可能で、比較的大きい電流を制御するものであっても組み立て前のウェハ検査を可能とする。

【解決手段】IC11のチップ12に、実使用時に使われるシャント抵抗Rmよりも高抵抗のシャント抵抗Rsを形成する。ウェハ検査ではスイッチ回路SW1、SW2をオフ、SW3、SW4をオンとし、制御信号生成回路16にシャント抵抗Rsの両端電圧を入力する。IC11の実使用時にはスイッチ回路SW1、SW2をオン、SW3、SW4をオフとし、制御信号生成回路16にシャント抵抗Rmの両端電圧を入力する。ウェハ検査の結果、シャント抵抗Rmの抵抗値が目標値に等しい場合、組み立て工程でパッドPmとリード電極Tbとを接続し、パッドPsをオープンとする。シャント抵抗Rmの抵抗値が目標値よりも高い場合、組み立て工程においてさらにパッドPsとリード電極Tbを接続する。

(もっと読む)

1 - 20 / 33

[ Back to top ]