Fターム[5F038AR21]の内容

Fターム[5F038AR21]の下位に属するFターム

単位抵抗 (89)

特性や抵抗値を異ならせたもの (83)

Fターム[5F038AR21]に分類される特許

1 - 20 / 187

ESD保護回路およびこれを備えた半導体装置

半導体装置

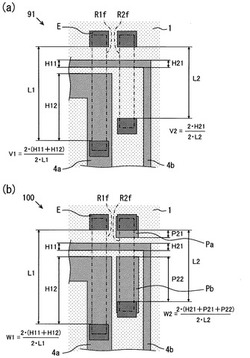

【課題】任意の配線設計に適用でき、高精度な抵抗比を有する2個の抵抗体を備えた小型の半導体装置を提供する。

【解決手段】抵抗体R1f,R2fの長さをL、配線4a,4bの直上にある抵抗体R1f,R2fの外辺の長さを配線上長さH、外辺配線被覆率Vを、V=H/2Lで定義したとき、2個の抵抗体R1f,R2fのうち少なくとも外辺配線被覆率Vの小さい抵抗体R2fの下方において、配線4a,4bと同じ配線層から形成された反射補正パッドPa,Pbが、外辺の直下に配置されてなり、反射補正パッドPa,Pbの直上にある抵抗体R2fの外辺の長さを補正パッド上長さPとし、抵抗体R1f,R2fの外辺配線層被覆率Wを、W=(H+P)/2Lで定義したとき、2個の抵抗体R1f,R2fについて、外辺配線層被覆率Wの差が、記外辺配線被覆率Vの差より小さく設定されてなる半導体装置100とする。

(もっと読む)

半導体装置

【課題】抵抗値が制御されることができる抵抗素子を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、絶縁膜14bと、半導体素子と、抵抗素子4tとを有する。絶縁膜14bは半導体基板101の少なくとも一部を被覆している。半導体素子は、半導体基板101の一部からなるチャネル領域と、電極とを有する。抵抗素子4tは、電極を流れる電流に対する抵抗となるように電極と電気的に接続され、かつ絶縁膜14bを介して半導体基板101上に設けられている。抵抗素子4tは半導体領域を含む。半導体基板101と抵抗素子4tとの間の電位差により半導体領域に空乏層が生じる。

(もっと読む)

半導体装置

【課題】次段回路で基準電圧として用いられる定電圧を生成する基準電圧回路について、ツェナーダイオードの製造ばらつき等が出力定電圧の温度特性に及ぼす影響を低減する。また、当該出力定電圧の温度特性の平坦性を向上する。また、回路規模の増大を抑制しつつ優れた起動性、応答性および安定性を実現する。

【解決手段】分圧回路332は直列接続されたダイオード304,306,308に対して並列的に設けられている。分圧回路332の低電位側接続点yの電圧は正の温度特性を示し、分圧回路332の高電位側接続点xの電圧は負の温度特性を示す。分圧点zにおける定電圧V0が平坦な温度特性を持つように分圧抵抗316,318の抵抗値が設定されている。分圧回路332の分圧点zは、フィードバックループに接続されることなく次段回路へ接続されることにより、次段回路へ定電圧V0を出力する。

(もっと読む)

R−2Rラダー抵抗回路、そのR−2Rラダー抵抗回路を備えるD/A変換器及びR−2Rラダー抵抗回路の製造方法

【課題】抵抗Rと抵抗2Rとの抵抗比を1:2に近付けることにより、D/A変換精度の悪化を抑制することを可能にするR−2Rラダー抵抗回路、そのR−2Rラダー抵抗回路を備えるD/A変換器及びR−2Rラダー抵抗回路の製造方法を提供すること

【解決手段】本発明にかかるR−2Rラダー抵抗回路10は、1ビットに対応する抵抗値Rの第1抵抗及び抵抗値2Rの第2抵抗を備える。第1抵抗及び第2抵抗は、1列に並んでいる複数の単位抵抗により構成される。R−2Rラダー抵抗回路10は、前記複数の単位抵抗が並設されて構成されており、第1抵抗に含まれる単位抵抗131がR−2Rラダー抵抗回路10の一端に配置され、単位抵抗131と第1抵抗に含まれる単位抵抗132との間に第2抵抗に含まれる単位抵抗121〜124が配置されている。

(もっと読む)

電圧調整回路、電圧調整方法および固体撮像装置

【課題】低消費電力で、かつ、発生する電圧に依存することなく消費電力が一定している電圧調整回路を提供する。

【解決手段】半導体基板上に形成され、発生する電圧を調整するための回路であって、直列に接続された複数の抵抗体(抵抗11、12、13a〜13f)と、複数の抵抗体の接続点のそれぞれに一端が接続され、他端がお互いに共通に接続された第1組の複数のヒューズ31a〜31gと、共通に接続された第1組の複数のヒューズ31a〜31gの他端に接続された第1の出力端子2とを備える。

(もっと読む)

縦構造キャパシタを備える半導体装置

【課題】縦構造キャパシタの剥離を防止し、チップサイズの増加を抑制した半導体装置を提供する。

【解決手段】半導体装置には、第1の回路の機能素子として使用される第1の縦構造キャパシタと、第2の回路の機能素子として使用され、第1の縦構造キャパシタよりも容量値の大きい第2の縦構造キャパシタと、が含まれている。半導体装置では、第1の縦構造キャパシタを、第2の縦構造キャパシタに隣接、又は、包含させるようにレイアウトする。

(もっと読む)

半導体集積装置

【課題】SiPのチップ間を接続するための端子数が増加する。

【解決手段】パッケージ内部に第1の半導体チップと第2の半導体チップが集積される半導体集積回路であって、前記第1の半導体チップは、第1の通信部と、複数のアナログ回路とを備え、前記第2の半導体チップは、第2の通信部と、前記複数のアナログ回路の特性調整用データを格納するメモリ部とを備え、前記第1の通信部と前記第2の通信部とがシリアルデータ通信線で接続され、前記シリアルデータ線を経由して前記第1の半導体チップが備える複数のアナログ回路の特性調整用データをそれぞれ複数のアナログ回路に転送する半導体集積回路。

(もっと読む)

電気回路の製造方法及び電気回路

【課題】所定の電圧値の検出に適した電気回路とその製造方法を提供する。

【解決手段】コンパレーターと、基準電圧生成回路と、第1の電源との接続側に設けられた第1のヒューズを有する第1のユニットと、第2の電源との接続側に設けられた第2のヒューズを有する第2のユニットと、を含み、前記第1のユニットと前記第2のユニットとが縦列接続され、前記第1の電圧は前記第1のユニットと前記第2のユニットとの間の所定の位置における電圧であり、前記基準電圧生成回路は、前記第1の電源及び前記第2の電源から前記基準電圧を生成し、前記第1のヒューズ及び前記第2のヒューズを切断しない状態で前記コンパレーターの出力が変化するときの前記第1の電源の電圧を測定する第1の工程と、前記第1の工程における測定結果に基づき、前記第1のヒューズ及び前記第2のヒューズの切断を行う第2の工程と、を有する。

(もっと読む)

トリミング回路及び半導体装置

【課題】ヒューズを切断するための電流を入力する専用の端子を必要としないトリミング回路及び半導体装置を提供する。

【解決手段】内部回路の外部端子であるパッドに接続された入力端子と、電源端子と出力端子との間に設けられたヒューズと、入力端子と出力端子との間に設けられたダイオードと、を備え、パッドにダイオードが順方向バイアスになるように電圧を印加して、トリミング回路のトリミングを行うように構成した。

(もっと読む)

半導体装置

【課題】抵抗素子を有する半導体装置に関し、集積度を低下することなく低消費電力化と高い回路精度とを実現しうる半導体装置を提供する。

【解決手段】半導体材料により形成された複数の抵抗素子と、複数の抵抗素子の近傍に配置された加熱用抵抗素子と、対向する2つの接続ノード間に加熱用抵抗素子が接続され、対向する他の2つの接続ノード間に電源線が接続された抵抗ブリッジ回路とを有する。

(もっと読む)

温度測定装置、温度校正装置及び温度校正方法

【課題】熱処理機構を用いて基板を所定の温度に熱処理する熱処理装置において、前記熱処理機構の温度を簡易な方法で適切に校正する。

【解決手段】温度校正装置の温度検査治具10は、熱処理板上に載置される被処理ウェハ70と、被処理ウェハ70上に設けられた複数のホイートストンブリッジ回路71とを有している。ホイートストンブリッジ回路71は、温度変化に応じて抵抗値が変化する4つの測温抵抗体72と、接触子41が接触する4つのコンタクトパッド73と有している。温度校正装置の制御部では、ホイートストンブリッジ回路71が平衡状態となるように、すなわちホイートストンブリッジ回路71のオフセット電圧がゼロになるように、熱処理板の温度を調節する。

(もっと読む)

半導体抵抗素子及び半導体抵抗素子を有する半導体モジュール

【課題】無駄な電流や信号の歪み等を発生させることなく、抵抗素子層の電位と、その周辺の半導体基板や電源線、信号線等の電位との電位差によって抵抗素子層の抵抗値が変化してしまうことを抑えることのできる半導体抵抗素子及び半導体抵抗素子を有する半導体モジュールを提供する。

【解決手段】抵抗素子層13は、抵抗値変化係数K1,K2によって、正極領域である領域13Aと負極領域である領域13Bとに分かれている。基準位置oから領域13Aの中心位置a又は領域13Bの中心位置bまでの間の抵抗値を量とする指標値r1,r2と、当該抵抗値R1,R2と、抵抗値変化係数K1,K2との積の総和が零になるように形成される。つまり、領域13Aの抵抗値変化成分dR1と領域13Bの抵抗値変化成分dR2とを相殺して、抵抗素子層13の抵抗値が変化してしまうのを抑えることができる。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を確保する。

【解決手段】基板と、基板に埋め込まれ、複数の開口部を有する絶縁膜と、複数の開口部内に位置する基板に設けられた複数のダミー拡散層20と、抵抗素子形成領域40において、平面視でダミー拡散層20と重ならないように絶縁膜上に設けられ、かつ第1方向に延伸する複数の抵抗素子10と、抵抗素子形成領域40において、絶縁膜上およびダミー拡散層20上に設けられ、かつ第1方向に延伸する複数のダミー抵抗素子12と、を備え、ダミー抵抗素子12は、平面視で、第1方向と基板に水平な面内において垂直な第2方向に並ぶ少なくとも二つのダミー拡散層20と重なっている。

(もっと読む)

半導体装置及びその製造方法

【課題】占有面積の小さい抵抗体を有する半導体装置を提供する。

【解決手段】半導体基板上のフィールド酸化膜の上に導電性多結晶シリコンを形成し、その上を覆う絶縁膜に多結晶シリコン5に達するコンタクトホールを形成する。コンタクトホールの中にはタングステンサイドウォール9、シリコン酸化膜サイドウォール10、抵抗体11があり、抵抗体の上には電極12を配置することで上下方向に縦長の抵抗体11とする。

(もっと読む)

抵抗分割回路及び電圧検出回路

【課題】スイッチ素子のオン抵抗の影響を排除することにより、トリミングの誤差が特定の条件において大きくなることを回避することができる抵抗分割回路、さらには精度がよい電圧検出回路を提供する。

【解決手段】直列接続した抵抗値に重み付けをした複数の抵抗素子と、抵抗素子とそれぞれ並列に接続されたスイッチ素子とを備えた抵抗分割回路で、対応する抵抗素子の抵抗値とスイッチ素子がショート状態のときの抵抗値との比を一定となるように構成した。

(もっと読む)

抵抗素子および抵抗素子の製造方法

【課題】膜厚のばらつきに起因する抵抗値の変動を抑制し、より高精度な抵抗素子を提供する。

【解決手段】第1膜厚(T1)(H1)で形成され、第1幅(W1)を有する抵抗素子第1部分(2)と、第1膜厚(T1)(H1)で形成され、第1幅(W1)に依存して決定する第2幅(W2)を有する抵抗素子第2部分(3)とを具備する抵抗素子を構成する。ここにおいて、第1幅(W1)と第2幅(W2)との和は一定である。また、抵抗素子第1部分(2)は、抵抗素子第1部分(2)の底面からの高さが第1高さ(H1)となる位置に、抵抗素子第1部分(2)の上面を有する。また、抵抗素子第2部分(3)は、抵抗素子第1部分(2)の底面を含む面からの高さが第1高さ(H1)となる位置に、抵抗素子第2部分(3)の上面を有する。そして、抵抗素子第1部分(2)と抵抗素子第2部分(3)とは、接続部を介して互いに接続されている。

(もっと読む)

有機抵抗による基準電圧発生回路、それを備えたA/D変換回路

【課題】アナログオプション回路を備えた半導体集積回路(A/D変換)を構成する抵抗を、簡便かつ大面積を専有されることなく作成する製造方法、及びその製造方法により作成されるAD変換回路を提供する。

【解決手段】高電源の電圧と低電源の電圧との間に直列に接続された複数個の抵抗からなるストリング抵抗を備えた基準電圧発生部と、入力アナログ電圧値と前記抵抗間の接続点の分圧電圧値とを比較する電圧比較部とを含むA/D変換回路において、

前記抵抗が有機材料で形成されていることを特徴とする。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】複数の基準電位を要する半導体装置、及び半導体装置の駆動において、より消費電力を軽減する。

【解決手段】電源線に直列に接続された複数の抵抗素子により、電源線に供給された電位を抵抗分割し、電源線と電気的に接続するスイッチトランジスタを介して所望の分割された電位を出力する電位分割回路を有する半導体装置であり、スイッチトランジスタのドレイン端子は出力側の回路に設けられたトランジスタのゲート端子(又は容量素子の一方の端子)と電気的に接続しノードを構成する。

(もっと読む)

半導体装置のトリミング方法、及びトリミング制御回路

【課題】スイッチ素子の製造バラツキを排除し、より均一で確実な溶断が行える半導体装置のトリミング方法、及びトリミング制御回路を提供すること。

【解決手段】電位が異なる第1電源(電源端子c)と第2電源(接地端子d)との間にて直列接続された第1スイッチ素子S1〜S3およびフューズF1〜F3を内蔵した半導体装置101における第1スイッチ素子S1〜S3をオン制御することでフューズF1〜F3に電圧を印加してフューズF1〜F3を溶断する半導体装置101のトリミング方法であって、第1スイッチ素子S1〜S3をターンオン制御することにより、第1電源(電源端子c)からフューズF1〜F3を溶断させない第1電圧値を所定時間印加するステップと、第1電圧値の印加が完了した後、第1電源(電源端子c)からフューズF1〜F3を溶断させる第2電圧値を印加するように切り替えるステップと、を含む。

(もっと読む)

1 - 20 / 187

[ Back to top ]