Fターム[5F038AR23]の内容

半導体集積回路 (75,215) | 固定抵抗 (2,429) | 拡散型薄膜型共通 (1,230) | 複数配置、直並列接続 (359) | 特性や抵抗値を異ならせたもの (83)

Fターム[5F038AR23]に分類される特許

1 - 20 / 83

半導体装置及びこれを備える半導体モジュール

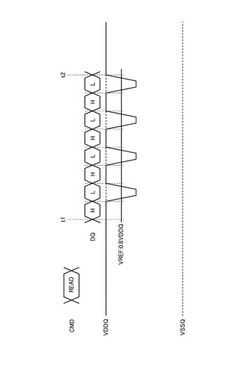

【課題】データ出力バッファの正確なインピーダンスキャリブレーション動作を行う。

【解決手段】電源ラインVL1とデータ端子24との間に接続されたP型トランジスタユニット201と、電源ラインVL1とキャリブレーション端子ZQとの間に接続されたP型トランジスタユニット111〜114と、キャリブレーション端子ZQの電位が基準電位VREFと一致するよう、P型トランジスタユニット111〜114インピーダンスを調整し、一致した状態におけるP型トランジスタユニット111〜114の一つのインピーダンスをP型トランジスタユニット201に反映させるインピーダンス制御回路とを備える。これにより、基準電位VREFが電源電位VDDの半分のレベルからオフセットしたレベルに設定されている場合であっても、正確なキャリブレーション動作を行うことができる。

(もっと読む)

半導体集積回路

【課題】半導体集積回路における抵抗の比精度の改善にある。

【解決手段】第1抵抗R1の第1抵抗体10は、長さL、幅Wを有する。第1コンタクト12aは、第1抵抗体10の一端に形成され、第2コンタクト12bは、第1抵抗体10の他端に形成される。第2抵抗R2の第2抵抗体10は、長さL/2、幅Wを有する。第2抵抗体10の一端には、N個の第1コンタクト12aが形成され、第2抵抗体10の他端には、N個の第2コンタクト12bが形成される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を製造することはできないから、高抵抗の拡散抵抗は実現できなかった。

【解決手段】一組の薄膜構造体の対向する間隔に、サイドウォール形成用の絶縁膜を形成する際に生じる空隙を利用して露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を形成する。薄膜構造体を配線抵抗として利用すれば、これらを接続して設けることにより温度特性に優れる抵抗素子を構成することもできる。

(もっと読む)

スタンダードセル回路、半導体集積回路、及び半導体集積回路装置

【課題】スタンダードセル回路のレイアウト面積を削減する。

【解決手段】配線導体Laは電源電圧VDDaを出力する電源に接続される。レギュレータ6aは、配線導体Laからの電源電圧VDDaを電源電圧VDDaより低い電源電圧VDDbに変換し、配線導体Lbを介してレベルシフタ2−1〜2−3,3,及びスタンダードセル4に出力する。レベルシフタ2−1は、入力されるデータの電圧レベルを電源電圧VDDaの電圧レベルから電源電圧VDDbの電圧レベルに電圧シフトしてスタンダードセル4に出力する。レベルシフタ3は、スタンダードセル4からの出力信号の電圧レベルを電源電圧VDDbの電圧レベルから電源電圧VDDaの電圧レベルに電圧シフトし、出力端子Tqを介して出力する。

(もっと読む)

R−2Rラダー抵抗回路、そのR−2Rラダー抵抗回路を備えるD/A変換器及びR−2Rラダー抵抗回路の製造方法

【課題】抵抗Rと抵抗2Rとの抵抗比を1:2に近付けることにより、D/A変換精度の悪化を抑制することを可能にするR−2Rラダー抵抗回路、そのR−2Rラダー抵抗回路を備えるD/A変換器及びR−2Rラダー抵抗回路の製造方法を提供すること

【解決手段】本発明にかかるR−2Rラダー抵抗回路10は、1ビットに対応する抵抗値Rの第1抵抗及び抵抗値2Rの第2抵抗を備える。第1抵抗及び第2抵抗は、1列に並んでいる複数の単位抵抗により構成される。R−2Rラダー抵抗回路10は、前記複数の単位抵抗が並設されて構成されており、第1抵抗に含まれる単位抵抗131がR−2Rラダー抵抗回路10の一端に配置され、単位抵抗131と第1抵抗に含まれる単位抵抗132との間に第2抵抗に含まれる単位抵抗121〜124が配置されている。

(もっと読む)

半導体装置

【課題】回路規模が増大化する。

【解決手段】抵抗値が順に小さい値となって直列接続される複数のヒューズを備えるヒューズ部と、前記ヒューズ部の複数のヒューズのそれぞれ一端と、第1の電源電圧との間に接続される複数の選択スイッチと、前記第1の電源電圧から所定の電位差を有するヒューズ溶断用電圧を、前記ヒューズ部の最も小さい抵抗値のヒューズ側に出力するヒューズ溶融電圧出力回路と、ヒューズ溶断時に、前記ヒューズ溶融電圧出力回路が前記ヒューズ溶断用電圧を出力し、前記ヒューズ部の最も大きい抵抗値のヒューズに接続される選択スイッチから最も小さい抵抗値のヒューズに接続される選択スイッチまでを順に導通させる制御回路と、を備える半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体集積回路内の抵抗素子の抵抗値のばらつきを抑制した半導体装置を提供する。

【解決手段】半導体装置は基板を備える。第1の絶縁膜は基板上に設けられる。第1の抵抗部は第1の絶縁膜上に設けられる。境界膜は第1の抵抗部上に設けられる。第2の抵抗部は境界膜上に設けられる。第2の絶縁膜は、第2の抵抗部上に設けられている。第1の導電部および第2の導電部は、第2の絶縁膜上に設けられ、互いに絶縁されている。第1の導電部は、第2の絶縁膜および第2の抵抗部を貫通して境界膜の表面に接触する第1のコネクト部を含む。第2の導電部は、第2の絶縁膜および第2の抵抗部を貫通して境界膜の表面に接触する第2のコネクト部を含む。第1の抵抗部は、一端において第1のコネクト部を介して第1の導電部に電気的に接続され、かつ、他端において第2のコネクト部を介して第2の導電部に電気的に接続された抵抗素子である。

(もっと読む)

半導体装置

【課題】広範囲、光分解能に周波数を可変することのできるクロック信号を生成する。

【解決手段】オペアンプAMP1は、正入力部と負入力部が等しい電圧となるようフィードバックがかかり、回路ノードfbckは、参照電圧VREFIに等しい電圧となる。デコーダDECは、制御信号CNT7,CNT6をデコードし、トランジスタT2〜T5のいずれか1つをオンさせる。この構成によって、回路ノードfbckが、参照電圧VREFIと同電位となるようフィードバック制御がかかるため、トランジスタT2〜T5のON抵抗を大幅に低減することができ、周波数精度の悪化を防止することができる。

(もっと読む)

抵抗素子および抵抗素子の製造方法

【課題】膜厚のばらつきに起因する抵抗値の変動を抑制し、より高精度な抵抗素子を提供する。

【解決手段】第1膜厚(T1)(H1)で形成され、第1幅(W1)を有する抵抗素子第1部分(2)と、第1膜厚(T1)(H1)で形成され、第1幅(W1)に依存して決定する第2幅(W2)を有する抵抗素子第2部分(3)とを具備する抵抗素子を構成する。ここにおいて、第1幅(W1)と第2幅(W2)との和は一定である。また、抵抗素子第1部分(2)は、抵抗素子第1部分(2)の底面からの高さが第1高さ(H1)となる位置に、抵抗素子第1部分(2)の上面を有する。また、抵抗素子第2部分(3)は、抵抗素子第1部分(2)の底面を含む面からの高さが第1高さ(H1)となる位置に、抵抗素子第2部分(3)の上面を有する。そして、抵抗素子第1部分(2)と抵抗素子第2部分(3)とは、接続部を介して互いに接続されている。

(もっと読む)

半導体装置

【課題】抵抗値の温度依存性の小さい抵抗素子を有する半導体装置を提供する。

【解決手段】半導体装置は、金属抵抗素子層Rm1,Rm2を有する。金属抵抗素子層Rm1は、金属抵抗膜層Rm11を含む。金属抵抗素子層Rm2は、金属抵抗膜層Rm12を含む。金属抵抗膜層Rm11は、窒化チタン抵抗および窒化タンタル抵抗のうちの一方であり、金属抵抗膜層Rm12は、窒化チタン抵抗および窒化タンタル抵抗のうちの他方である。窒化チタン抵抗の抵抗値は正の温度係数を有する一方、窒化タンタル抵抗の抵抗値は負の温度係数を有する。コンタクトプラグCP2によって、金属抵抗膜層Rm11と金属抵抗膜層Rm12とが電気的に接続されるので、窒化チタン抵抗の温度係数と窒化タンタル抵抗との温度係数が相殺される。これにより温度係数を小さくすることができる。

(もっと読む)

ポリシリコン抵抗の設計方法及び半導体装置の製造方法

【課題】半導体装置のサイズの大型化を抑制しつつ、ポリシリコン抵抗の抵抗値が設計値からずれた場合に補正できるようにする。

【解決手段】ポリシリコン抵抗の設計方法は、シリサイド領域1bが両端にそれぞれ形成されたポリシリコンにより構成され、シリサイド領域1bがコンタクト3へ接続されるポリシリコン抵抗1の、抵抗値を判定する工程を有する。抵抗値が設計値よりも大きい場合には、コンタクト3の位置とポリシリコン抵抗1の形成範囲とを変更せずに、シリサイドブロック膜の形成範囲を狭める補正を行うことによって、ポリシリコン抵抗1の抵抗値を減少させる工程を行う。抵抗値が設計値よりも小さい場合には、コンタクト3の位置を変更せずに、ポリシリコン(シリサイドブロック領域1a)の幅を狭める補正を行うことによって、ポリシリコン抵抗1の抵抗値を増大させる工程を行う。

(もっと読む)

半導体集積回路のレイアウト設計装置、レイアウト設計方法及びレイアウト設計プログラム並びに半導体集積回路装置の製造方法

【課題】半導体集積回路の設計TATの増大を防止する。

【解決手段】レイアウト設計装置は、パッケージに起因して半導体チップに加わるパッケージ応力の応力値の分布を示す応力分布データを読み込む応力分布データ読込み手段3と、半導体チップのチップレイアウトデータから素子レイアウトデータを抽出する素子レイアウトデータ獲得手段7と、半導体チップに搭載される各素子について応力値と素子の特性変動の関係を示した検量線データを保持する検量線データ保持部9と、応力分布データ、素子レイアウトデータ及び検量線データに基づいて各素子についてパッケージ応力による素子特性変動を算出する素子特性変動計算手段11と、素子特性変動を打ち消すように素子レイアウトデータを補正する素子レイアウト補正手段13と、補正後素子レイアウトデータを用いてチップレイアウトデータを補正するチップレイアウト補正手段と、を備えている。

(もっと読む)

半導体装置の製造方法

【課題】ポリシリコン抵抗体の上に急速熱酸化処理により形成され、シリサイド化ブロック用酸化膜の一部として用いる熱酸化膜の膜厚が多種のポリシリコン抵抗体間でばらつくことにより、ポリシリコン抵抗体が部分的にシリサイド化されることを回避する。

【解決手段】多種のポリシリコン抵抗体全てにおいて、急速熱酸化処理によりポリシリコン抵抗体上に生成される熱酸化膜の膜厚と、ポリシリコン抵抗体を含む非シリサイド化領域に形成された保護酸化膜の膜厚との和が、シリサイド化ブロック用酸化膜としてのブロック性能を確保するために必要な膜厚以上となるように、保護酸化膜の膜厚を決定する。多種のポリシリコン抵抗体間で急速熱酸化処理により生成される熱酸化膜の膜厚に差が生じる場合でも、熱酸化膜と保護酸化膜とをシリサイド化ブロック用酸化膜として用いることにより、充分なブロック性能を確保することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】チップサイズを増大させずに、より少ない製造工程数で製造された、抵抗値の異なる複数の抵抗素子を備えた半導体装置及び半導体装置の製造方法を提供する。

【解決手段】レジストマスク36をマスクとしてゲート電極23とマスク層22とを同一部材及び同一工程で形成し、形成されたマスク層22により高抵抗素子40となるポリシリコン高抵抗層16及びポリシリコン低抵抗層18の積層体と、低抵抗素子42となるポリシリコン高抵抗層16及びポリシリコン低抵抗層18の積層体と、をエッチングすることにより高抵抗素子40と、抵抗値が高抵抗素子40よりも低い低抵抗素子42と、を形成する。

(もっと読む)

分圧回路及び半導体装置

【課題】検出精度がよく、かつ回路規模、チップサイズの縮小させた分圧回路及び半導体装置を提供すること。

【解決手段】2進コードに従って抵抗値が重み付けされて形成される第1抵抗回路と、同じ2進コードに従って抵抗値が重み付けされて形成される第2抵抗回路と、同じ2進コードに従って抵抗値が重み付けされ、重み付けのビット数が最大である第3抵抗を有する第3抵抗回路と備え、第3抵抗の両端のいずれかを2つのトランスミッションゲートで択一的に出力端子と接続する構成とした。

(もっと読む)

半導体集積回路および集積回路製造方法および集積回路設計方法

【課題】SoCにおけるRF・アナログ集積回路のプロトタイピングにおいて,チップ毎に柔軟かつ簡便に短TATで素子パラメータを調整する手段を提供する。

【解決手段】本発明によれば,製造プロセス終了後にダイシングされた集積回路チップの最上部に,単一あるいは小数の金属層,絶縁層などの機能層を積層・パターニングし,インダクタンスや容量素子,抵抗素子,伝送線路などを構成して下地回路と結合したり,あらかじめ下地集積回路中に形成しておいた受動素子等を金属配線層でプログラミングすることにより,下地集積回路のRF・アナログ回路の特性を実チップ上でチップ毎に柔軟に,低コストかつ短TATで調整することができる。

(もっと読む)

集束加熱源を使用して半導体素子のインピーダンスを変更する方法

【課題】集束加熱源を使用して半導体素子すなわち半導体デバイスのインピーダンスを調整(すなわち、修正または変更)する方法が提供される。

【解決手段】この方法は、集束加熱源(例えば、レーザ)の溶融作用によって、より高ドーパント濃度の隣接領域からドーパントを拡散させることによって、低ドーパント濃度の領域のドーパント・プロファイルを変更する(すなわち、ドーパント濃度を増加させる)ことによって、半導体素子すなわち半導体デバイスのインピーダンスを微調整するために利用されてよい。本発明は、特に、以前には存在しなかった導電性リンクと導電路との形成のための、回路に対するレーザの使用に関する。さらに、本発明は、特に、ギャップ領域の長さに沿った1つまたは複数の導電性ブリッジの位置に応じてインピーダンスの変更(すなわち、トリミングまたは調整)が有利に行われることが可能な手段に関する。

(もっと読む)

電子デバイス

【課題】製造工程数や面積の増大を招くことなく、金属薄膜抵抗の抵抗率を異ならせる素子構造を提案する。

【解決手段】基板に形成された積層構造における絶縁層間の導電膜配置階層の1つに、抵抗素子の抵抗値を規定する抵抗膜5が配置されている。また、抵抗膜5の厚さ方向の少なくとも一方の他の導電膜配置階層に、水素吸蔵金属3が、抵抗膜5と絶縁された状態で、かつ金属抵抗膜の少なくともコンタクトエッジ間の領域の全域と平面視で重なる位置と大きさで配置されている。

(もっと読む)

電子デバイスおよびその製造方法

【課題】抵抗値を精度よく容易に設定可能な構造の抵抗素子を有する電子デバイスを実現する。

【解決手段】半導体等の基板に形成された積層構造における絶縁層間の導電膜配置階層の1つに、抵抗素子の抵抗値を規定する抵抗膜(金属薄膜11)が配置されている。この金属薄膜11は、2種類以上の抵抗率をもつ。この金属薄膜11は、望ましくは、抵抗率が異なる複数の面領域(高抵抗面領域RHと低抵抗面領域RL1,RL2)をもつ複抵抗領域型の金属薄膜11Wである。

(もっと読む)

拡散層抵抗を備える半導体装置及び製造方法

【課題】工程数の低減や製造コストの削減を図りつつ、各々が異なる抵抗値を有する複数の拡散層抵抗を備えた半導体装置及び製造方法を提供する。

【解決手段】半導体基板の表面側を酸化又は窒化せしめることによって保護膜41を形成し、当該保護膜下に伸張し且つ何れかの導電型の不純物を各々が含む複数の拡散層領域21,22,23を形成する。次いで、当該複数の拡散層領域のうちの少なくとも1つの拡散層領域上にフォトレジスト膜を形成し、半導体基板の裏面側に接地電位を供給しつつ、プラズマアッシング処理を当該フォトレジスト膜に施すことによってこれを除去する。最後に、各拡散層領域と電気的に接続された配線層60を絶縁層40を介して形成することによって、各拡散層領域を拡散層抵抗とする。

(もっと読む)

1 - 20 / 83

[ Back to top ]