Fターム[5F038AV02]の内容

半導体集積回路 (75,215) | 可変インピーダンス (2,334) | 可変素子(自身のインピーダンスを使用) (1,002) | トリミング (330)

Fターム[5F038AV02]の下位に属するFターム

エネルギービーム (144)

Fターム[5F038AV02]に分類される特許

1 - 20 / 186

半導体装置

半導体集積回路

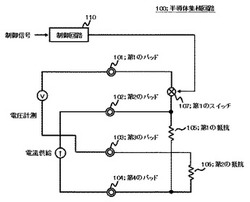

【課題】半導体集積回路に含まれる終端抵抗の抵抗値を4端子法によって測定をするためには、必要となる端子が増加し、半導体集積回路のチップサイズが増加するという問題がある。そのため、半導体集積回路のチップサイズ増加を抑制しつつ、終端抵抗の抵抗値を高精度で測定可能な半導体集積回路が、望まれる。

【解決手段】半導体集積回路は、第1乃至第4のパッドと、第2のパッドと第4のパッドの間に接続される第1の抵抗と、第3のパッドと第4のパッドの間に接続される第2の抵抗と、第1のパッドと第2のパッドの間に接続される第1のスイッチと、第1のパッド及び第3のパッドを4端子法における電圧測定端子として、第2のパッド及び第4のパッドを4端子法における電流供給端子として、それぞれ使用し第1の抵抗の抵抗値を測定するテストモードへの遷移指示を含む制御信号に基づき、第1のスイッチをオンする制御回路と、を備える。

(もっと読む)

半導体装置

【課題】発振周波数変動の許容範囲を任意に設定可能にする。

【解決手段】半導体装置(21)は、トリミングレジスタ(11)に保持されたトリミング値によって発振周波数が変更される発振器(12)と、発振周波数を補正可能な補正回路(20)とを含む。上記補正回路は、上限値を設定可能な上限値レジスタ(6)と、下限値を設定可能な下限値レジスタ(7)と、発振周波数を分周するための分周回路(13)と、分周回路の出力をカウントするカウンタ(3)とを含む。さらに上記補正回路は、カウンタの出力を保持可能なバッファレジスタ(4)と、バッファレジスタの保持値が、上限値と下限値との間に入っているか否かを判別する比較器(5)と、その判別結果に基づいてトリミング値を補正するトリミング値補正制御回路(8)とを含む。ユーザは、上限値と下限値とによって、発振周波数変動の許容範囲を任意に設定することができる。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

半導体装置

【課題】次段回路で基準電圧として用いられる定電圧を生成する基準電圧回路について、ツェナーダイオードの製造ばらつき等が出力定電圧の温度特性に及ぼす影響を低減する。また、当該出力定電圧の温度特性の平坦性を向上する。また、回路規模の増大を抑制しつつ優れた起動性、応答性および安定性を実現する。

【解決手段】分圧回路332は直列接続されたダイオード304,306,308に対して並列的に設けられている。分圧回路332の低電位側接続点yの電圧は正の温度特性を示し、分圧回路332の高電位側接続点xの電圧は負の温度特性を示す。分圧点zにおける定電圧V0が平坦な温度特性を持つように分圧抵抗316,318の抵抗値が設定されている。分圧回路332の分圧点zは、フィードバックループに接続されることなく次段回路へ接続されることにより、次段回路へ定電圧V0を出力する。

(もっと読む)

半導体集積装置

【課題】SiPのチップ間を接続するための端子数が増加する。

【解決手段】パッケージ内部に第1の半導体チップと第2の半導体チップが集積される半導体集積回路であって、前記第1の半導体チップは、第1の通信部と、複数のアナログ回路とを備え、前記第2の半導体チップは、第2の通信部と、前記複数のアナログ回路の特性調整用データを格納するメモリ部とを備え、前記第1の通信部と前記第2の通信部とがシリアルデータ通信線で接続され、前記シリアルデータ線を経由して前記第1の半導体チップが備える複数のアナログ回路の特性調整用データをそれぞれ複数のアナログ回路に転送する半導体集積回路。

(もっと読む)

半導体装置

【課題】回路規模が増大化する。

【解決手段】抵抗値が順に小さい値となって直列接続される複数のヒューズを備えるヒューズ部と、前記ヒューズ部の複数のヒューズのそれぞれ一端と、第1の電源電圧との間に接続される複数の選択スイッチと、前記第1の電源電圧から所定の電位差を有するヒューズ溶断用電圧を、前記ヒューズ部の最も小さい抵抗値のヒューズ側に出力するヒューズ溶融電圧出力回路と、ヒューズ溶断時に、前記ヒューズ溶融電圧出力回路が前記ヒューズ溶断用電圧を出力し、前記ヒューズ部の最も大きい抵抗値のヒューズに接続される選択スイッチから最も小さい抵抗値のヒューズに接続される選択スイッチまでを順に導通させる制御回路と、を備える半導体装置。

(もっと読む)

トリミング回路及び半導体装置

【課題】ヒューズを切断するための電流を入力する専用の端子を必要としないトリミング回路及び半導体装置を提供する。

【解決手段】内部回路の外部端子であるパッドに接続された入力端子と、電源端子と出力端子との間に設けられたヒューズと、入力端子と出力端子との間に設けられたダイオードと、を備え、パッドにダイオードが順方向バイアスになるように電圧を印加して、トリミング回路のトリミングを行うように構成した。

(もっと読む)

定電流回路

【課題】 1つのトリミング抵抗により出力電流の増加方向と減少方向の両方向の調整が可能な定電流回路を提供する。

【解決手段】 トリミング抵抗TR11と抵抗R11の電圧降下をトランジスタ対Q14、Q15により比較し、トリミング抵抗TR11の電圧降下が抵抗R11より小さい場合は、トランジスタQ11にトリミング抵抗に流れる電流のみを流し、トリミング抵抗TR11の電圧降下が抵抗R11より大きい場合は、トランジスタQ11にトリミング抵抗に流れる電流に加えて、トランジスタQ17から電流を供給する。この回路構成により、トリミング抵抗の抵抗値の増加に従い、出力電流Ioutが減少した後、増加する特性を得ることができる。

(もっと読む)

半導体装置

【課題】レーザートリミングの際に半導体基板のダメージを極力抑えながら導電体を溶断することが可能な半導体装置を提供する。

【解決手段】半導体基板10上にLOCOS絶縁膜11を覆う第1の絶縁膜12が形成され、第1の絶縁膜12上には、LOCOS絶縁膜11の平坦部11F上を通って、レーザートリミングにより溶断される導電体20が形成されている。第1の絶縁膜12及び導電体20を覆って、LOCOS絶縁膜11の平坦部11Fと重畳する領域内に凸レンズ状の凸部13Cを有した第2の絶縁膜13が形成されている。レーザートリミングの際、LOCOS絶縁膜11の平坦部11Fの両側の傾斜部11Sでは、レーザー光が半導体基板10の表面に斜めに入射するように反射されるため、半導体基板10のダメージを回避できる。また、第2の絶縁膜13の凸部13Cは、レーザー光を屈折させて導電体20に集光させる。

(もっと読む)

半導体ウェハ、半導体装置、及び半導体装置の製造方法

【課題】ヒューズメモリを利用したトリミングを行う半導体ウェハにおける各半導体チップの回路面積を小さくする。

【解決手段】半導体ウェハ10におけるシリコン基板上は、複数個のチップ領域TARとこの領域TARを囲むスクライブ領域SARとに区画されている。チップ領域TARには、トリミング対象回路11と、ヒューズ素子Fm(m=1〜2M)と、ヒューズ素子Fm(m=1〜2M)が断線状態であるか否かを検出する検出回路としての役割を果たす定電流源IPm(m=1〜2M)及びインバータINm(m=1〜2M)とが形成されている。スクライブ領域SARには、制御信号に応じてON/OFFが切り換わり、ONとなることによりヒューズ素子Fm(m=1〜2M)を断線させる電流を発生するNチャネル電界効果トランジスタTSm(m=1〜2M)がある。

(もっと読む)

抵抗分割回路及び電圧検出回路

【課題】スイッチ素子のオン抵抗の影響を排除することにより、トリミングの誤差が特定の条件において大きくなることを回避することができる抵抗分割回路、さらには精度がよい電圧検出回路を提供する。

【解決手段】直列接続した抵抗値に重み付けをした複数の抵抗素子と、抵抗素子とそれぞれ並列に接続されたスイッチ素子とを備えた抵抗分割回路で、対応する抵抗素子の抵抗値とスイッチ素子がショート状態のときの抵抗値との比を一定となるように構成した。

(もっと読む)

バンドギャップ型基準電圧発生回路

【課題】バンドギャップ型基準電圧発生回路において、高温における寄生ダイオードのリーク電流の影響を制御して、基準電圧の温度特性の向上を図る。

【解決手段】NPN型BIPトランジスタQ1の寄生ダイオードD1とは別に、i個(iは1以上の自然数)の温度特性制御ダイオードD31〜D3iをNPN型BIPトランジスタQ1のコレクタに接続する。温度特性制御ダイオードD31〜D3iは、Pチャネル型MOSトランジスタM1,M2からなるカレントミラー回路を介して、寄生ダイオードD21〜D2Kのリーク電流の増加による基準電圧Vrefへの影響をキャンセルするように作用する。

(もっと読む)

保護素子およびそれを備えた半導体装置

【課題】被保護素子に接続されることにより、被保護素子の破壊を未然に防止できる保護素子を提供すること。

【解決手段】アノード電極15とカソード電極16との間に主たる電流を流す被保護素子に対して、電気的に並列に接続される保護素子1であって、GaN層13よりもバンドギャップの大きなAlGaN層14が形成され、AlGaN層14の表面に離間してアノード電極15とカソード電極16とが形成され、アノード電極15とカソード電極と16の間の2次元電子ガス層13Aを流れる電流のオンオフを制御する制御電極19を備えたオンオフ可能領域21を備え、制御電極19が所定の抵抗体20を介してアノード電極15に接続されてなり、アノード電極15が被保護素子のアノード電極15と接続され、カソード電極16が被保護素子のカソード電極16と接続され、被保護素子より耐圧が低く設定されている。

(もっと読む)

半導体集積回路

【課題】外部電源電圧を降圧するレギュレータを内蔵することによるチップ面積の増大を抑え且つ降圧電圧の安定化を実現できる半導体集積回路を提供する。

【解決手段】外部電源電圧(Vext)よりも低い内部電源電圧(Vint)で動作する内部回路を持つ半導体集積回路において、内部電源電圧を生成するレギュレータ(150〜157)を、バッファ及び保護素子を配置するための第2の領域(2)に配置することにより、降圧電源回路のオンチップ化による面積オーバヘッドを低減する。降圧電圧を伝達するループ状の電源幹線(L20)を用い、電源幹線に外付け安定化容量を接続するための電極パッドを設ける等により、低消費電力を更に促進する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、ヒューズ層を覆う絶縁膜の膜厚を精度良く調整する。

【解決手段】半導体基板10上の第2の層間絶縁膜17上にヒューズ層18Tが形成され、ヒューズ層18Tは第3の層間絶縁膜20で覆われる。第3の層間絶縁膜20上には、キャップメタル24に覆われたパッド電極23が形成され、それらは第1及び第2のパッシベーション膜25,26に覆われる。次に、ヒューズ層18T上で開口する第1のレジスト層27をマスクとして、ヒューズ層18T上で第2のパッシベーション膜26から第3の絶縁膜の厚さ方向の途中までをエッチングする。その後、パッド電極23上で開口する第2のレジスト層30をマスクとして、パッド電極23上で第1及び第2のパッシベーション膜25,26及びキャップメタル層24をエッチングしてパッド電極23の表面を露出する。その後、保護膜32を形成する。

(もっと読む)

半導体装置のトリミング方法、及びトリミング制御回路

【課題】スイッチ素子の製造バラツキを排除し、より均一で確実な溶断が行える半導体装置のトリミング方法、及びトリミング制御回路を提供すること。

【解決手段】電位が異なる第1電源(電源端子c)と第2電源(接地端子d)との間にて直列接続された第1スイッチ素子S1〜S3およびフューズF1〜F3を内蔵した半導体装置101における第1スイッチ素子S1〜S3をオン制御することでフューズF1〜F3に電圧を印加してフューズF1〜F3を溶断する半導体装置101のトリミング方法であって、第1スイッチ素子S1〜S3をターンオン制御することにより、第1電源(電源端子c)からフューズF1〜F3を溶断させない第1電圧値を所定時間印加するステップと、第1電圧値の印加が完了した後、第1電源(電源端子c)からフューズF1〜F3を溶断させる第2電圧値を印加するように切り替えるステップと、を含む。

(もっと読む)

半導体装置及びその駆動方法

【課題】現行プロセスを用いて追加工程なしに製造でき、高い信頼性を有する多値化された電気ヒューズを有する半導体装置を提供する。

【解決手段】第1フィラメントFS1と、第1フィラメントFS1に接続された第2フィラメントFS2とを有する電気ヒューズ素子を有し、第1フィラメントFS1の第2フィラメントFS2との接続端と反対の端部に接続された第1フィラメントFS1と第2フィラメントFS2の直列抵抗を読み出す直列読み出し部RDSとを有する構成とする。

(もっと読む)

半導体集積回路

【課題】 ヒューズを用いてデータを記憶する半導体集積回路において、データの誤読み出しを抑制すること。

【解決手段】 半導体集積回路100は、直列に接続された複数のヒューズを含むヒューズ回路10と、複数のヒューズに対し切断用の電流を供給する切断電流供給部30と、複数のヒューズの切断情報を読み出す読み出し部20と、を備える。ヒューズ回路10は、第1端子N1及び第2端子N2を含み、複数のヒューズは、第1端子N1に接続された第1ヒューズF1と、第1ヒューズF1及び第2端子N2に接続された第2ヒューズF2とを含む。読み出し部20は、第1端子N1に接続された第1電源端子Vddと、第2端子N2に接続された第2電源端子Vssと、第1端子N1と第1電源端子Vddとの間(N3)に接続され、切断情報を出力する出力回路40とを含む。

(もっと読む)

アナログ電圧調整回路、及びアナログ電圧調整方法

【課題】検査工程と調整工程をほぼ同時に実行可能な、アナログ電圧調整回路を提供する。

【解決手段】アナログ電圧調整回路1は、外部装置から、目標電圧を示す目標電圧信号を入力する、目標電圧入力端子12と、目標電圧信号に基づいて生成された目標電圧を示すデータを取り込み、期待値データとして格納する、期待値データ格納回路7と、トリミングデータを格納し、トリミングデータに応じたトリミング信号を出力する、トリミングデータ格納回路11と、トリミング信号を取得し、トリミングデータに応じた電圧レベルで、アナログ出力信号を出力する、アナログ信号出力回路2と、アナログ出力信号の電圧レベルを示す測定データと、格納された前記期待値データとを比較し、比較結果を示す比較結果信号を生成する比較回路8と、比較結果信号に基いて、トリミングデータを変更するか否かを決定する、制御回路10とを具備する。

(もっと読む)

1 - 20 / 186

[ Back to top ]