Fターム[5F038AV03]の内容

半導体集積回路 (75,215) | 可変インピーダンス (2,334) | 可変素子(自身のインピーダンスを使用) (1,002) | トリミング (330) | エネルギービーム (144)

Fターム[5F038AV03]に分類される特許

1 - 20 / 144

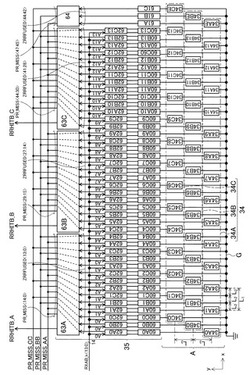

半導体装置及びトリミング方法

【課題】ヒューズ素子の列数増に伴うトリミング時間の伸長を抑制する。

【解決手段】x方向に延伸する接地配線Gと、接地配線のy方向の一方側に設けられたヒューズ素子領域Aにx方向に沿って3列に並べて配置され、かつそれぞれの一端が接地配線Gに共通に接続される複数のヒューズ素子と、ヒューズ素子領域Aを挟んで接地配線Gの反対側に設けられ、ヒューズ素子領域Aに配置された複数のヒューズ素子それぞれの他端と接続される救済回路とを備え、上記複数のヒューズ素子は、それぞれ1つの欠陥選択線を示すアドレス情報を記憶する複数のヒューズ素子グループに所定個ずつグループ化され、同一のヒューズ素子グループに属する所定個のヒューズ素子は、同一列に配置されることを特徴とする

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

半導体装置

【課題】抵抗体とヒューズ素子が並列に接続された半導体装置において、ヒューズ素子切断時に抵抗体への損傷がなく、抵抗体とヒューズ素子とを積層すること。

【解決手段】半導体基板上に第1の絶縁膜を介して形成された抵抗体を設け、抵抗体の上に第2の絶縁膜を介して形成された遮光層を設け、遮光層の上に第3の絶縁膜を介して形成されたヒューズ素子のヒューズ部を有し、抵抗体と遮光層とヒューズ部を重畳した半導体装置とする。

(もっと読む)

ラッチ回路、トリミング回路、システム、判定プログラム、確認方法、及び判定方法

【課題】入力信号の状態が適正であるかを確認することができる、ラッチ回路、トリミング回路、システム、判定プログラム、確認方法、及び判定方法を提供する。

【解決手段】トリミング回路14の読出回路20から出力されるトリミング素子であるヒューズ素子H1の状態に応じた入力信号I1が入力されるラッチ回路22を、ラッチ回路L1と、ラッチ回路L2と、一致確認回路26と、で構成している。ラッチ回路L1は、入力信号I1の論理値をタイミングT1で保持して、保持した論理値に応じた出力信号O1をトリミング回路14の外部に出力する。ラッチ回路L2は、タイミングT1よりも遅いタイミングT2で保持して、保持した論理値に応じた出力信号O2を出力する。一致確認回路26は、排他的論理和回路30により構成されており、出力信号O1と出力信号O2とが一致しているか否かを示す一致判定信号X1を外部の判定回路18に出力する。

(もっと読む)

ヒューズ回路及びトリミング良否判定方法

【課題】ヒューズ開口部の端部に必ず切断すべきヒューズを配設することにより、レーザー照射後のその切断/未切断をもって、端部のポリイミド膜の膜厚の良否を容易に判定する。

【解決手段】ヒューズ回路は、ヒューズ開口部FAの、ポリイミド膜の厚さが不本意に厚く残りやすい端部に配設された2つの切断確認用ヒューズ1a,1bと、ポリイミド膜の厚さ変動が端部に比べ少ない領域RAに配設された複数の実使用ヒューズ7a〜7dと、2つの切断確認用ヒューズ1a,1bからの信号を入力して当該ヒューズ1a,1bが確実に切断されているかを判定するヒューズ未切断判定回路2と、を備えている。なお、ヒューズ未切断判定回路2は、更にテストモード信号を入力すると共に、出力回路(例えばDQ回路)に判定結果を出力している。

(もっと読む)

半導体装置

【課題】半導体装置において、高電圧の配線層とその下方を横切るように配置された抵抗層との間の絶縁膜の耐圧を確保し、この配線層と抵抗層との間で破壊が起きるのを抑制することを目的とする。

【解決手段】第1半導体領域10に接続され第2半導体領域11上を通過するように第3配線層22が配置されている。第3配線層22と第2半導体領域11との間に配置される絶縁膜14内には、一端が第3配線層22に接続されると共に、他端が第1半導体領域11よりも電位の低い制御端子12に接続され、且つ第3配線層22とSOI層2との間において第3配線層22を少なくとも1回以上横切る構成で抵抗層25が配置されている。この抵抗層25は、第3配線層22を横切る部位の上面が他の部位よりも下方位置となるように段差状に形成されている。

(もっと読む)

半導体装置

【課題】レーザートリミングの際に半導体基板のダメージを極力抑えながら導電体を溶断することが可能な半導体装置を提供する。

【解決手段】半導体基板10上にLOCOS絶縁膜11を覆う第1の絶縁膜12が形成され、第1の絶縁膜12上には、LOCOS絶縁膜11の平坦部11F上を通って、レーザートリミングにより溶断される導電体20が形成されている。第1の絶縁膜12及び導電体20を覆って、LOCOS絶縁膜11の平坦部11Fと重畳する領域内に凸レンズ状の凸部13Cを有した第2の絶縁膜13が形成されている。レーザートリミングの際、LOCOS絶縁膜11の平坦部11Fの両側の傾斜部11Sでは、レーザー光が半導体基板10の表面に斜めに入射するように反射されるため、半導体基板10のダメージを回避できる。また、第2の絶縁膜13の凸部13Cは、レーザー光を屈折させて導電体20に集光させる。

(もっと読む)

半導体装置の製造方法

【課題】製造工程を簡略化することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に薄膜抵抗体15を構成する金属薄膜およびバリアメタル16を構成するバリアメタル薄膜を形成する。そして、金属薄膜およびバリアメタル薄膜をパターニングし、薄膜抵抗体15と当該薄膜抵抗体15上にバリアメタル膜16aを形成する。その後、バリアメタル膜16a上に絶縁膜17を形成し、絶縁膜17にバリアメタルエッチング部16bを露出させる開口部17aと、コンタクト部を露出させるコンタクトホール17bを形成する。続いて、コンタクトホール17bを介してバリアメタル膜16aと電気的に接続される導電性薄膜18cを形成する。その後、導電性薄膜18cのうちバリアメタルエッチング部16b上に位置する部分をウェットエッチングによってパターニングし、バリアメタル膜16aのうちバリアメタルエッチング部16bをパターニングする。

(もっと読む)

垂直集積システム

【課題】コストのかかる空間をとらずに電子部品内に個別パッシブ部品を組み込むことが可能な垂直集積システムを提供する。

【解決手段】集積回路システム100は、半導体ダイ110の前面上に製造された第一のアクティブ層と、半導体ダイ110の裏面上の第二の予め製造された層とを含み、その第二の予め製造された層は、その中に埋め込まれた電気部品を有し、その電子部品は、少なくとも一つの個別パッシブ部品140を含む。また、集積システム100は、第一のアクティブ層及び第二の予め製造された層を結合する少なくとも一つの電気経路150も含む。

(もっと読む)

バンドギャップ型基準電圧発生回路

【課題】バンドギャップ型基準電圧発生回路において、高温における寄生ダイオードのリーク電流の影響を制御して、基準電圧の温度特性の向上を図る。

【解決手段】NPN型BIPトランジスタQ1の寄生ダイオードD1とは別に、i個(iは1以上の自然数)の温度特性制御ダイオードD31〜D3iをNPN型BIPトランジスタQ1のコレクタに接続する。温度特性制御ダイオードD31〜D3iは、Pチャネル型MOSトランジスタM1,M2からなるカレントミラー回路を介して、寄生ダイオードD21〜D2Kのリーク電流の増加による基準電圧Vrefへの影響をキャンセルするように作用する。

(もっと読む)

半導体装置、及び、その製造方法

【課題】半導体装置、及び、その製造方法を提供する。

【解決手段】PN接合を有する第1半導体素子と、PN接合を有する第2半導体素子と、第1半導体素子と第2半導体素子とを構成要素として含む回路と、を有し、回路から、第1半導体素子のPN接合に生じる第1順方向電圧と、第2半導体素子のPN接合に生じる第2順方向電圧とが加算された加算信号が出力される半導体装置であって、第1半導体素子と第2半導体素子とが直列接続されており、第1半導体素子及び第2半導体素子それぞれの実使用温度域において、回路が第2半導体素子を構成要素として含まない場合に、回路から出力される第1信号の温度特性と、回路が第1半導体素子を含まない場合に、回路から出力される第2信号の温度特性と、が反転している。

(もっと読む)

半導体装置及びその製造方法

【課題】トリミング素子からのトリミング時の気化ガスの圧力によりトリミング素子の下部の層間絶縁膜にクラックが入るのを防止する。

【解決手段】層間絶縁膜2上にトリミング素子Tを形成する。トリミング素子Tの上を層間絶縁膜3aで被覆する。トリミング素子Tの斜め上方領域の層間絶縁膜3a上にクラック誘導体Gを形成する。トリミング素子T及びクラック誘導体Gはレーザー光の照射領域に配置される。レーザー光を照射すると、トリミング素子Tの周辺及びクラック誘導体Gの周辺の層間絶縁膜3a等に重畳して広く延在する高温領域6が形成され、該高温化した層間絶縁膜3a等の剛性が低下する。その結果、トリミング素子Tの上辺のコーナー部に気化ガスの圧力がかかりやすくなり、トリミング素子Tの下辺のコーナー部にかかる気化ガスの圧力が小さくなるので、トリミング素子Tの下側の層間絶縁膜2のクラック5発生を防止できる。

(もっと読む)

半導体集積回路および電子機器

【課題】不揮発性記憶素子にフューズ素子を用いた半導体集積回路において、目的とするデータと、検査データとしての目的とするデータの論理否定データとを記憶し、フューズ素子の不可逆性を利用することで、記憶回路と検証回路の回路規模をあまり大きくすることなく、またデータ検証の処理時間の増大を招くことなく、記憶データの信頼性と正真性を保証する。

【解決手段】記憶すべき情報を示す特定データを不可逆的に記憶する不揮発性記憶回路100aを有する半導体集積回路100において、該不揮発性記憶回路100aを、該特定データの非反転データを記憶する第1の記憶回路101と、該特定データの反転データを記憶する第2の記憶回路102とを有する構成とした。

(もっと読む)

集束加熱源を使用して半導体素子のインピーダンスを変更する方法

【課題】集束加熱源を使用して半導体素子すなわち半導体デバイスのインピーダンスを調整(すなわち、修正または変更)する方法が提供される。

【解決手段】この方法は、集束加熱源(例えば、レーザ)の溶融作用によって、より高ドーパント濃度の隣接領域からドーパントを拡散させることによって、低ドーパント濃度の領域のドーパント・プロファイルを変更する(すなわち、ドーパント濃度を増加させる)ことによって、半導体素子すなわち半導体デバイスのインピーダンスを微調整するために利用されてよい。本発明は、特に、以前には存在しなかった導電性リンクと導電路との形成のための、回路に対するレーザの使用に関する。さらに、本発明は、特に、ギャップ領域の長さに沿った1つまたは複数の導電性ブリッジの位置に応じてインピーダンスの変更(すなわち、トリミングまたは調整)が有利に行われることが可能な手段に関する。

(もっと読む)

半導体装置

【課題】アンチフューズにより多数のフューズ設定を切り替えることのできる半導体装置を提供する。

【解決手段】異なる機能または特性を有する機能回路に対応して設けられたn個の機能判定回路41−1〜41−nと、n個のフューズ素子を有し、機能判定回路各々の判定に用いる機能設定情報を格納するフューズ回路31、フューズ回路32と、アンチフューズ素子AF1の導通・非導通状態に応じて、フューズ回路のいずれか1つを選択するアンチフューズ判定回路20と、を備える。

(もっと読む)

温度検出器、温度検出器用抵抗器の調整装置、温度検出器用抵抗器の調整方法および半導体装置

【課題】感温素子にかかる温度特性の傾きをほぼ一致させる調整を行うことにより、温度検出器相互間のばらつきを低減できるようにする。

【解決手段】感温ダイオードD(感温素子)を備え、温度に応じた電圧を出力する温度検出器10おいて、感温ダイオードDごとに異なる温度特性の傾きが所定の傾きとなるように、温度の変化に従って感温ダイオードDに流す電流Ifを調整する抵抗器R2(調整部)を備える。この構成によれば、感温ダイオードDの温度特性の傾きが異なっても、抵抗器R2が感温ダイオードDに流す電流Ifを調整することで所定の傾きとなるように調整する。そのため、感温ダイオードDにかかる温度特性の傾きが所定の傾きでほぼ一致するようになるので、温度検出器10相互間のばらつきを低減することができる。

(もっと読む)

半導体装置

【課題】ヒューズ切断処理時間を短縮できるヒューズ素子を提供する。

【解決手段】ヒューズ素子1の第1切断可能配線3、第2切断可能配線5及び第3配線7は、レーザースポット11のスポット径Rよりも小さい線幅Wをもつ。第1切断可能配線3、第2切断可能配線5は、スポット径Rよりも長い長さL1、L2をもつ。第1切断可能配線3の一端、第2切断可能配線5の一端及び第3配線7の一端は、ヒューズ素子1の切断可能交差部9に接続されている。切断可能交差部9はスポット11のサイズよりも小さい平面サイズの一辺の長さが寸法Wの正方形に形成されている。第1切断可能配線3の一端、第2切断可能配線5の一端及び第3配線7の一端は、互いに切断可能交差部9の異なる辺に接続されており、互いに接触していない。ヒューズ素子1は、第1切断可能配線3からなるヒューズと第2切断可能配線5からなるヒューズが直列に接続された回路と等価である。

(もっと読む)

半導体装置の製造方法、製造プログラム、及び半導体装置

【課題】回路規模の増大を抑制しつつ、素子破壊によってノード間の電気的接続を制御する電流制御素子を有する半導体装置の信頼性を高める。

【解決手段】本発明による半導体装置の製造方法は、半導体ウエハ1上に形成された素子特性抽出用パタン30の素子特性を測定するステップと、測定された素子特性を、素子特性抽出用パタン30に対応付けられた電流制御素子20の素子特性として抽出するステップと、抽出された素子特性に基づいて、半導体ウエハ1上におけるノード間に形成された電流制御素子20に供給するエネルギーを設定するステップと、設定されたエネルギーを電流制御素子に供給し、電流制御素子の素子破壊によってノード間の電気的接続を不可逆的に制御するステップとを具備する。

(もっと読む)

インダクタを備えた半導体集積回路

【課題】半導体集積回路をパッケージに実装した後に、インダクタンスを増加および減少させる調整が可能な半導体集積回路を提供する。

【解決手段】LSIの内部回路106が形成された同一の半導体基板に磁気検出素子100が形成されており、ボンディングパッド114とLSIの内部回路106の間に接続された第1インダクタ101のインダクタンスを磁気検出素子100と磁気検出回路105の出力電圧でモニタし、第1インダクタ101の片方の端子と第2インダクタ102の一端と第3インダクタ103の一端が第1接続部107を介して接続される第1スイッチ108、第2インダクタ102の片方の端子が第2接続部109を介して接続される第2スイッチ110、および、第3インダクタ103の片方の端子が第3接続部111を介して接続される第3スイッチ112を接続または切断状態に切り替えることにより、第一のインダクタ101をトリミングする。

(もっと読む)

トリミング回路

【課題】トリミング処理部にヒューズ等の配線の再接続対策を施した場合でも、その再接続判定結果を保持するための特別なレジスタを不要とし、製造コストを最小限に抑えることが実現できるようにする。

【解決手段】トリミングデータをトリミング対象回路140に入力させることによって該トリミング対象回路140の回路特性値を調整するとき、トリミング対象回路140に入力させるトリミングデータを格納するシフトレジスタ130と、ヒューズの切断/非切断によってトリミングデータを発生するトリミング処理部110と、プリテスト時に外部入力したテスト用のトリミングデータTDATAをシフトレジスタ130に転送し、実際のトリミング時にトリミング処理部110で発生したトリミングデータをシフトレジスタ130に転送するセレクタ部120とを備える。

(もっと読む)

1 - 20 / 144

[ Back to top ]