Fターム[5F038AV16]の内容

半導体集積回路 (75,215) | 可変インピーダンス (2,334) | 可変回路(他素子のインピーダンスを使用) (1,117) | スイッチ素子による切換 (1,056) | 変更不能 (524) | 書込回路(書込用端子も含む) (58)

Fターム[5F038AV16]に分類される特許

1 - 20 / 58

半導体記憶素子及び半導体記憶装置

【課題】LSI素子の性能劣化及びヒューズ素子の欠陥の増加を抑制できる半導体記憶素子及び半導体記憶装置を提供する。

【解決手段】半導体記憶素子100は、第1ヒューズ線111と、第1ヒューズ線111と並列接続された第2ヒューズ線112とを有し、切断されているか否かによって2値のデータを保持するヒューズ素子110と、一端がワード線130に接続されており、ヒューズ素子110に電流を流すか否かを選択する選択素子120と、を備える。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

半導体装置

【課題】回路規模が増大化する。

【解決手段】抵抗値が順に小さい値となって直列接続される複数のヒューズを備えるヒューズ部と、前記ヒューズ部の複数のヒューズのそれぞれ一端と、第1の電源電圧との間に接続される複数の選択スイッチと、前記第1の電源電圧から所定の電位差を有するヒューズ溶断用電圧を、前記ヒューズ部の最も小さい抵抗値のヒューズ側に出力するヒューズ溶融電圧出力回路と、ヒューズ溶断時に、前記ヒューズ溶融電圧出力回路が前記ヒューズ溶断用電圧を出力し、前記ヒューズ部の最も大きい抵抗値のヒューズに接続される選択スイッチから最も小さい抵抗値のヒューズに接続される選択スイッチまでを順に導通させる制御回路と、を備える半導体装置。

(もっと読む)

半導体集積装置

【課題】SiPのチップ間を接続するための端子数が増加する。

【解決手段】パッケージ内部に第1の半導体チップと第2の半導体チップが集積される半導体集積回路であって、前記第1の半導体チップは、第1の通信部と、複数のアナログ回路とを備え、前記第2の半導体チップは、第2の通信部と、前記複数のアナログ回路の特性調整用データを格納するメモリ部とを備え、前記第1の通信部と前記第2の通信部とがシリアルデータ通信線で接続され、前記シリアルデータ線を経由して前記第1の半導体チップが備える複数のアナログ回路の特性調整用データをそれぞれ複数のアナログ回路に転送する半導体集積回路。

(もっと読む)

半導体デバイスの電気的にプログラミング可能なヒューズモジュール

【課題】より小型なeヒューズモジュールを提供する。

【解決手段】半導体デバイスが、eヒューズモジュールおよびプログラミング電流生成器を有する。eヒューズモジュールが電気的にプログラミングするeヒューズ素子(226)のアレイを含む。プログラミング電流発生器が、複数の基準トランジスタ素子(M0〜M6)のセットと、基準トランジスタ素子(M0〜M6)を活性化させて、選択された基準電流を生成するセレクタ(254)と、アレイの選択されたeヒューズ素子(226)に、選択された基準電流に応じたプログラミング電流を印加して、eヒューズ素子(226)の抵抗をプログラミングするカレントミラー(M7、M8、M9)とを有する。

(もっと読む)

半導体ウェハ、半導体装置、及び半導体装置の製造方法

【課題】ヒューズメモリを利用したトリミングを行う半導体ウェハにおける各半導体チップの回路面積を小さくする。

【解決手段】半導体ウェハ10におけるシリコン基板上は、複数個のチップ領域TARとこの領域TARを囲むスクライブ領域SARとに区画されている。チップ領域TARには、トリミング対象回路11と、ヒューズ素子Fm(m=1〜2M)と、ヒューズ素子Fm(m=1〜2M)が断線状態であるか否かを検出する検出回路としての役割を果たす定電流源IPm(m=1〜2M)及びインバータINm(m=1〜2M)とが形成されている。スクライブ領域SARには、制御信号に応じてON/OFFが切り換わり、ONとなることによりヒューズ素子Fm(m=1〜2M)を断線させる電流を発生するNチャネル電界効果トランジスタTSm(m=1〜2M)がある。

(もっと読む)

書き込み制御回路及び半導体装置

【課題】電気的に1回限りの書き込みが行われる記憶素子への誤書き込みを抑制する。

【解決手段】電圧検出部12は、電気的に1回限りの書き込みが行われる記憶素子(電気ヒューズ素子2)へ供給される書き込み電圧を検出し、書き込み電圧が所定の閾値電圧以上となると、書き込み制御部11に、書き込み信号に係わらず電気ヒューズ素子2への書き込みを停止させることで、書き込み電圧に異常が発生し、過電圧になることによる誤書き込みを抑制できる。

(もっと読む)

半導体装置のトリミング方法、及びトリミング制御回路

【課題】スイッチ素子の製造バラツキを排除し、より均一で確実な溶断が行える半導体装置のトリミング方法、及びトリミング制御回路を提供すること。

【解決手段】電位が異なる第1電源(電源端子c)と第2電源(接地端子d)との間にて直列接続された第1スイッチ素子S1〜S3およびフューズF1〜F3を内蔵した半導体装置101における第1スイッチ素子S1〜S3をオン制御することでフューズF1〜F3に電圧を印加してフューズF1〜F3を溶断する半導体装置101のトリミング方法であって、第1スイッチ素子S1〜S3をターンオン制御することにより、第1電源(電源端子c)からフューズF1〜F3を溶断させない第1電圧値を所定時間印加するステップと、第1電圧値の印加が完了した後、第1電源(電源端子c)からフューズF1〜F3を溶断させる第2電圧値を印加するように切り替えるステップと、を含む。

(もっと読む)

半導体装置

【課題】印加電圧の過剰による、アンチヒューズ素子の誤コネクトや書き込みが正確に行われないアンチヒューズ素子の発生を抑制する。

【解決手段】本発明の半導体装置は、アンチヒューズ素子の一端の電位AF_Gと電位VPPRとを比較し、電位AF_Gが電位VPPR以上の場合には、アンチヒューズ素子の一端に接続される電源線の電位VPPSVTを昇圧し、昇圧された電位によりアンチヒューズ素子の一端と他端とが導通状態となることで、電位AF_Gが電位VPPRよりも低くなった場合には、昇圧を停止する。

(もっと読む)

半導体装置及びヒューズ回路の状態判定方法

【課題】切断したヒューズ素子の再癒着等があってもシステムの安全性が確保できる信頼性の高い半導体装置及びヒューズ回路の状態判定方法を提供する。

【解決手段】導通または非導通にそれぞれ設定可能な複数のヒューズ素子と、複数のヒューズ素子にそれぞれ接続され複数のヒューズ素子が導通または非導通のいずれの状態であるかをそれぞれ読み出す読出し回路と、読出し回路に接続され、複数のヒューズ素子の導通、非導通の状態を判定して1ビットのデータとして出力するデータ出力回路と、読出し回路に接続され、複数のヒューズ素子が一致して導通または非導通の状態にあるか否かをモニタする状態モニタ回路と、を含むヒューズ回路を備える。

(もっと読む)

半導体装置

【課題】高周波動作向けの半導体装置を高性能化させる。

【解決手段】シリコン基板S1上に形成された抵抗素子TDR1および不揮発性メモリNVM1を有する半導体装置であって、不揮発性メモリNVM1は、シリコン基板S1上に埋め込み酸化層BOX1を介して配置されたシリコン層SOI1に形成されている。特に、抵抗素子TDR1と不揮発性メモリNVM1とは互いに電気的に接続され、不揮発性メモリNVM1のオン状態またはオフ状態により、抵抗素子TDR1の導通状態または非導通状態が切り替わる。

(もっと読む)

半導体装置

【課題】バーンイン試験が実施される半導体装置であって、自装置の品質を表す情報であるバーンイン試験の実施時間を特定することが容易な半導体装置を提供する。

【解決手段】半導体装置1は、実施されたバーンイン試験時間を特定するための特定情報を記憶する記憶部2と記憶部2内に特定情報を記憶させ、また記憶された特定情報を読み出す制御部3とを含む。

(もっと読む)

半導体装置

【課題】異なる電圧で動作する回路を備えた半導体装置において、面積の増加を抑制することのできる半導体装置を提供する。

【解決手段】半導体装置は、外部端子10に接続され、該外部端子から入力される第1電圧で動作する第1回路20と、外部端子に抵抗素子を介して接続され、第1電圧より絶対値が小さい第2電圧で動作する第2回路40と、抵抗素子と第2回路との間の第1ノードに接続され、制御信号により導通と非導通とのいずれか一方が選択される分圧素子と、を具備する。分圧素子は、第1電圧が外部端子に印加され第1回路を動作させる場合、制御信号により導通状態が選択される。

(もっと読む)

電子部品装置および変化部品の製造方法

【課題】製造ばらつき等に対しても、高品質で電気的接続状態を変化させる。

【解決手段】電子部品装置200は、第1のヒューズ素子102aを含む第1のヒューズユニット100a、および第2のヒューズ素子102bを含む第2のヒューズユニット100bを含む電気ヒューズ101と、第1のヒューズ素子102aおよび第2のヒューズ素子102bの少なくともいずれか一方が電気的に切断されている場合に、電気ヒューズ101が電気的に切断されていると判定する判定回路150とを含む。第1のヒューズユニット100aおよび第2のヒューズユニット100bは、それぞれ独立に電流が印加され、所定の電流または電圧を印加した場合に電気的接続状態の変化が生じない割合に影響を与える制御パラメータの適正範囲が異なるように構成されるかまたは、値の異なる電流により切断される。

(もっと読む)

半導体装置と、それを用いた可変インピーダンス回路および共振回路

【課題】電源電圧が遮断されている場合でも記憶データに基づいてスイッチ回路を導通状態または非導通状態にすることが可能な半導体装置を提供する。

【解決手段】この半導体集積回路装置では、浮遊ゲートおよび制御ゲートを有するメモリトランジスタMAと、ゲートが浮遊ゲートに接続され、メモリトランジスタMAの記憶データに応じてオンまたはオフするNチャネルMOSトランジスタQAとを含む。したがって、電源電圧VCCが遮断されている場合でも、メモリトランジスタMAの記憶データに基づいてトランジスタQAをオンまたはオフさせることができる。

(もっと読む)

半導体チップ、半導体ウエハ、及び半導体チップの製造方法

【課題】ウエハ面内の複数のチップに対し、チップ毎に異なる内容の電気的な操作(チップIDの書き込み等)を、チップ毎ではなく複数チップ単位で一括して行えるようにする。

【解決手段】半導体チップ10は、対向する左辺S1及び右辺S2を有する矩形の主面108を有する。主面108上には、半導体素子104A及びBと、配線L11及びL12が形成されている。配線L11は、左辺S1から右辺S2に到達するように形成されるとともに、半導体素子104Aに結合されている。配線L12は、少なくとも左辺S1に接するように形成されるとともに、半導体素子104Bに結合されている。さらに、右辺S2上における配線L11の端部(TR0)と左辺S1上における配線L12の端部(TL0)は、辺S1及びS2に垂直な同一直線上に実質的に位置するように配置されている。

(もっと読む)

半導体装置

【課題】半導体チップがパッケージに実装された状態でのヒューズ専用端子を不所望に増加させることなく、最終テスト工程での電気ヒューズ溶断を実現する。

【解決手段】第1パッド(P1)、第2パッド(P3)、第3パッド(P2)を半導体チップに設ける。上記第1パッドと上記第3パッドとの間には、所定電圧が印加されることでプログラミング可能な第1ヒューズ素子を有する第1ヒューズ部(WFM)を設ける。上記第2パッドと上記第3パッドとの間には、所定電圧が印加されることでプログラミング可能な第2ヒューズ素子を有する第2ヒューズ部(PFM)を設ける。上記第2パッドに結合された第1端子(T3)と、上記第3パッドに結合された第2端子(T2)をパッケージに設ける。上記第1端子は、上記第2端子とは電気的に独立しており、上記第1端子を介して、上記第2ヒューズ部にヒューズ溶断のための電圧を印加することができる。

(もっと読む)

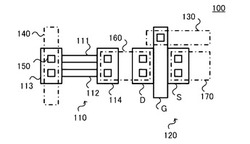

半導体集積回路装置

【課題】短時間でプログラム状態の検査が行えるワンタイムプログラマブルメモリを内蔵した半導体集積回路装置を提供する。

【解決手段】電気的に切断可能なヒューズ素子11と、第1スイッチ素子12とが縦続接続されたメモリセル13を複数有するワンタイムプログラマブルメモリ14と、各メモリセル13に、ヒューズ素子11と第1スイッチ素子12との接続ノードN1と、制御信号Vmに応じて出力インピーダンスがハイインピーダンス状態になる内部回路15に接続されている出力端子16との間に接続され、制御信号Vmに応じて駆動される第2スイッチ素子17と、を具備する。

(もっと読む)

半導体装置

【課題】ポリシリコン配線構造を利用する場合にプログラム後の抵抗値のばらつきがなく高抵抗値化が図れ、良好なプログラム特性や高信頼性を有する半導体装置を提供する。

【解決手段】第1の端子部12aと、第2の端子部12cと、前記第1および第2の端子部の相互間を接続するヒューズリンク12bとを有する半導体装置であって、前記第1の端子部および前記ヒューズリンクは、不純物イオンがドープされたポリシリコン層とその上に積層された金属元素を含む層とを有し、前記第2の端子部は、前記ヒューズリンクとの接続端側に不純物イオンがドープされていないポリシリコン層とその上に積層された金属元素を含む層とを有する。

(もっと読む)

トリミング回路

【課題】トリミング処理部にヒューズ等の配線の再接続対策を施した場合でも、その再接続判定結果を保持するための特別なレジスタを不要とし、製造コストを最小限に抑えることが実現できるようにする。

【解決手段】トリミングデータをトリミング対象回路140に入力させることによって該トリミング対象回路140の回路特性値を調整するとき、トリミング対象回路140に入力させるトリミングデータを格納するシフトレジスタ130と、ヒューズの切断/非切断によってトリミングデータを発生するトリミング処理部110と、プリテスト時に外部入力したテスト用のトリミングデータTDATAをシフトレジスタ130に転送し、実際のトリミング時にトリミング処理部110で発生したトリミングデータをシフトレジスタ130に転送するセレクタ部120とを備える。

(もっと読む)

1 - 20 / 58

[ Back to top ]