Fターム[5F038AV20]の内容

Fターム[5F038AV20]に分類される特許

1 - 18 / 18

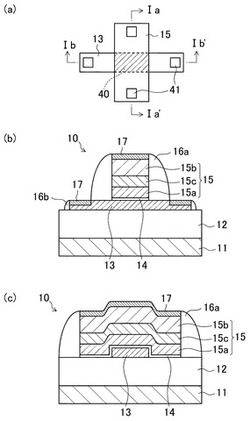

半導体装置及びその製造方法

【課題】容量値及びその変化量が大きく且つQ値の高い可変容量素子を備える半導体装置及びその製造方法を実現する。

【解決手段】半導体装置は、可変容量素子を備え、当該可変容量素子は、半導体基板11上に形成された下部電極13と、下部電極13上に形成された容量絶縁膜14と、容量絶縁膜14上に形成された上部電極15とを備える。上部電極15は、容量絶縁膜14上に位置する低濃度不純物層15aと、低濃度不純物層15a上に位置し且つ低濃度不純物層15aよりも不純物濃度が高い高濃度不純物層15bとを有する。

(もっと読む)

可変容量装置

【課題】 回路の小型化と消費電力の低減が可能な可変容量装置を提供する。

【解決手段】 容量検出回路31は、可変容量素子2の駆動容量C1のキャパシタンス値に応じた検出信号Sxと、基準となる基準信号Syとを出力する。駆動電圧制御回路21は、検出信号Sxと基準信号Syとを比較し、この比較結果に応じて駆動電圧Vcontを制御し、駆動容量C1を増加または減少させる。駆動容量C1の一端側には駆動電圧Vcontが印加され、他端側には容量検出回路31の検出用電流回路33から検出用電流Icontが周期的に入力される。このため、駆動容量C1が検出用電流回路33に接続されると、駆動容量C1のキャパシタンス値と検出用電流Icontの大きさとに応じて、駆動容量C1の他端側の電圧が上昇し、この電圧に応じた検出信号Sxが出力される。

(もっと読む)

集積回路とその製造方法

【課題】今後ますます増加するトランジスタの閾値のばらつきに対して、高速に動作させることができる集積回路を提供する。

【解決手段】集積回路1は、電流制御型のMOS電流論理回路10と、電流制御型のMOS電流論理回路10の定電流用MOSFET16に接続される可変抵抗素子20と、電流制御型のMOS電流論理回路10の閾値のばらつきにより生じる出力基準電圧の変動△VBを検出するアンプ22と、可変抵抗素子20の抵抗値を書き込む回路34と、を備えている。電流制御型のMOS電流論理回路10の基準電圧VBと出力信号との差がアンプ22によって検出され、可変抵抗素子20の抵抗が書き込み回路34によって書き込まれる。回路を構成するトランジスタの閾値がばらついても、集積回路1は高速且つ安定に動作する。

(もっと読む)

半導体装置、半導体集合部材及び半導体装置の製造方法

【課題】様々なオン抵抗の素子を容易に製造することができる半導体装置、半導体集合部材及び半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、素子部と、第1の電極部と、第2の電極部と、延出部と、を備える。素子部は、基板に設けられる。第1の電極部は、素子部の上に設けられ、素子部と導通する。第2の電極部は、素子部の上において第1の電極部と離間して設けられ、素子部と導通する。延出部は、素子部の上に設けられ、第1の電極部及び第2の電極部の周縁部から基板の周縁部に向けて延出して設けられる。

(もっと読む)

半導体装置

【課題】 制御端子が浮遊状態になると、予期しないリーク電流などにより電極に電荷が蓄積され、電極の電位が変動し、スイッチが誤動作してしまう可能性がある。

【解決手段】 クーロン力により湾曲させることで第1の信号電極と第2の信号電極とを接触または分離することが可能な架橋部と、前記架橋部を制御するための制御端子とを有するスイッチ素子と、前記制御端子に接続された第1の不揮発性半導体素子と、前記制御端子および前記第1の不揮発性半導体素子に接続された第2の不揮発性半導体素子とを備える。

(もっと読む)

可変ゲート電界効果トランジスタ(FET)及びこのFETを備える電気電子装置

【課題】可変ゲート電界効果トランジスタ(FET)及びこのFETを備える電気電子装置を提供する。

【解決手段】熱によるFETのソース及びドレイン間の電流減少の問題を効果的に解決し、またFETの温度を低めることができる可変ゲートFET及びこのFETを備える電気電子装置を提供し、可変ゲートFETは、FETと、FETの表面または発熱部分に取り付けられ、回路的には、FETのゲート端子に連結されておりゲート端子の電圧を変化させるゲート制御素子と、を備え、FETの温度が所定温度以上に上昇しているときに、ゲート制御素子が、ゲート端子の電圧を変化させて、FETのソース及びドレイン間のチャンネル電流を制御する。

(もっと読む)

半導体装置

【課題】製造工程のばらつきによる誤差を考慮したトリミングコードの設定を容易に行うことができるようにする。

【解決手段】半導体装置は、被調整電源1の出力電圧Vaを調整するトリミングコードTMRC(=TMRC1)を変化させながら発生し、被調整電源1の出力電圧Vaが目標電圧Vtに対応する値となった場合のトリミングコードTMRCをトリミングコード記憶回路3に記憶し、記憶したトリミングコードTMRC(=TMRC2)に基づき被調整電源1の出力電圧Vaを設定する。

(もっと読む)

半導体装置

【課題】プロセス、電圧および温度による影響を受けることなく、書込電流を制御するトランジスタへ定電流に応じた内部電圧を供給する。

【解決手段】半導体装置は、第1および第2主電極ならびに制御電極を有する第1トランジスタと、この第1トランジスタの第1主電極の電圧が所定の電圧となるように第1トランジスタの第2主電極および制御電極間の電圧を制御する制御回路と、第1および第2主電極ならびに制御電極を有する第2トランジスタとを含む内部電圧発生回路を備える。第2トランジスタは、第2主電極および制御電極間が第1トランジスタの第2主電極および制御電極間の電圧でバイアスされる。

(もっと読む)

共振回路及びその製造方法並びに電子装置

【課題】振動子の構造寸法のばらつきに起因する共振周波数の変動を抑制することのできる共振回路及びその製造方法を実現する。

【解決手段】本発明の共振回路30は、基板と、該基板上に形成された固定電極12、及び、該固定電極の少なくとも一部に対向する可動部を備えた可動電極13を有するMEMSレゾネータ10と、該MEMSレゾネータにバイアス電圧を印加するための電圧印加手段20と、を具備し、前記電圧印加手段は、前記可動部を構成する層と同じ層で構成され、該層の厚みで抵抗値が変化する補償用抵抗R11と、該補償用抵抗に接続され、前記可動部を構成する層と異なる構造で構成される基準抵抗R12とを分圧抵抗とし、前記補償用抵抗と前記基準抵抗の接続点電位を前記MEMSレゾネータの少なくとも一方の端子10bに出力し、前記抵抗値の変化により前記層の厚みと正の相関を有する前記バイアス電圧を前記振動子に与える分圧回路を有する。

(もっと読む)

金属−絶縁体転移(MIT)素子の自己発熱防止回路、及びその防止回路用の集積素子の製造方法

MIT素子の自己発熱問題を解決できるMIT素子の自己発熱防止回路、及びその防止回路用の集積素子の製造方法を提供する。該自己発熱防止回路は、所定の臨界温度以上で急激なMITが発生し、電流駆動素子に連結されて電流のフローを制御するMIT素子と、MIT素子に連結されて、MIT以後にMIT素子の自己発熱を制御するトランジスタと、MIT素子及びトランジスタに連結された抵抗素子と、を備える。  (もっと読む)

(もっと読む)

可変キャパシタ

【課題】静電力を利用して容量を可変にしつつ、可変容量比を高める。

【解決手段】可動板12は、基板11に対して上下動し得るように板ばね部14により支持される。可動板12の上方に、基板11に対して固定された固定板13が配置される。基板11上の固定側駆動電極32が相対的に下で、板ばね部14に設けられた可動側駆動電極33が相対的に上に配置される。固定板13に設けられた固定側容量電極34が相対的に上で、可動板12に設けられた可動側容量電極31が相対的に下に配置される。これにより、駆動電極32,33間に生ずる静電力が可動電極31,34間の間隔が拡がる方向に生ずるように、電極31〜34が配置される。

(もっと読む)

高周波回路用容量素子

【課題】基板との間の寄生容量を低減することができる高周波回路用容量素子を提供する。

【解決手段】コンデンサ2は、第1の電極と該第1の電極との間に容量を形成する第2の電極8とを有する。支持板3は、基板1とコンデンサ2との間を機械的に接続して、コンデンサ2を基板1から浮いた状態に支持する。コンデンサ2の端部と支持板3の端部とが機械的に接続されている。

(もっと読む)

半導体集積回路装置

【課題】制御される電流値の合わせ込みが可能で、比較的大きい電流を制御するものであっても組み立て前のウェハ検査を可能とする。

【解決手段】IC11のチップ12に、実使用時に使われるシャント抵抗Rmよりも高抵抗のシャント抵抗Rsを形成する。ウェハ検査ではスイッチ回路SW1、SW2をオフ、SW3、SW4をオンとし、制御信号生成回路16にシャント抵抗Rsの両端電圧を入力する。IC11の実使用時にはスイッチ回路SW1、SW2をオン、SW3、SW4をオフとし、制御信号生成回路16にシャント抵抗Rmの両端電圧を入力する。ウェハ検査の結果、シャント抵抗Rmの抵抗値が目標値に等しい場合、組み立て工程でパッドPmとリード電極Tbとを接続し、パッドPsをオープンとする。シャント抵抗Rmの抵抗値が目標値よりも高い場合、組み立て工程においてさらにパッドPsとリード電極Tbを接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】アンテナ搭載ICチップの小型化、低コスト化を図りつつ、共振周波数の適切な調整を行うことが可能な半導体装置とその製造方法を提供する。

【解決手段】電極3Aを一方の面に有する半導体基板2の一面を覆うように絶縁樹脂層4を形成する。次いで、絶縁樹脂層4が形成された半導体基板2の上に、電極3Aと整合する位置に開口部を形成し、前記電極3Aを露出させる。次に、絶縁樹脂層4の上に、開口部の一つを通して一端5aが電極3Aと電気的に直接接続されるアンテナ本体5、及び図示しない他の開口部を介して一端6aa,6ba,6caが全て、図示しない他の電極と電気的に直接接続される、前記アンテナ本体5の長さを調整する長さの異なる複数の調整部6a,6b,6cを有するアンテナ長調整用配線6をそれぞれ形成することにより、半導体装置1とする。

(もっと読む)

半導体装置

【課題】小さな駆動電圧で大きなコンタクト力が得られる半導体装置を提供する。

【解決手段】半導体装置は、弾性部材15、第1,第2の電極21,22、圧電アクチュエータ13及び静電アクチュエータ12を備えている。弾性部材は、基板10との間に空隙35’を形成するように、一端がアンカー27を介して固定されている。第1,第2の電極は、弾性部材の他端と基板にそれぞれ対向して配置される。圧電アクチュエータは、弾性部材の他端を基板に近づけるように変形させる。静電アクチュエータは、弾性部材内に配置された第3の電極と、第3の電極と対向するように基板上に配置された第4の電極とからなり、前記弾性部材の他端を前記基板に近づけるように変形させる。そして、圧電アクチュエータと静電アクチュエータの駆動によって第1の電極と第2の電極との距離が変化する。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】 チップの仕上がり抵抗値次第でアセンブリ工程でボンディング位置を変更することにより製品仕様許容範囲よりもチップの製造ばらつきが大きい場合でも製造歩留を下げない半導体集積回路装置を提供する。

【解決手段】 直列接続された抵抗素子114−119及び接続パッド108−111を有する半導体集積回路チップと、チップが搭載され第1及び第2の外部端子104、105及びこれら外部端子の夫々に接続された第1及び第2の配線パターン106、107を有するパッケージ基板102とを備える。抵抗素子114の1端は、第1の配線パターン106にボンディングワイヤ121で接続される第1の接続パッド108に接続され、第1の抵抗素子の他端及び第1の抵抗素子以外の抵抗素子の端子のうちの1つは、接続パッド109−111の1つにボンディングワイヤ113により接続されている。

(もっと読む)

可変容量コンデンサ

【課題】 印加電圧による容量変化が大きく、Q値が高く、温度特性の良好な可変容量コンデンサを提供すること。

【解決手段】 直列に接続された第1の可変容量素子および第1の容量素子と、直列に接続された第2の可変容量素子および第2の容量素子とが、第1の可変容量素子の外側と第2の容量素子の外側とを第1接続点で接続し、第2の可変容量素子の外側と第1の容量素子の外側とを第2接続点で接続して並列に接続され、第1の可変容量素子および第1の容量素子の間と第2の可変容量素子および第2の容量素子の間とに第3の容量素子が接続され、第1接続点および第2接続点の間に第4の容量素子が接続されているとともに、第3の容量素子と第4の容量素子とが静電的に結合しており、第1の接続点および第2の接続点が端子に接続されていることを特徴とする可変容量コンデンサ。

(もっと読む)

MOS容量型半導体装置およびこれを用いた水晶発振器

【課題】

小型で且つ良好な容量変化の可能な高周波用の容量素子を構成する半導体装置を提供する。

【解決手段】

基板表面にゲート絶縁膜を介して形成されたゲート電極と、前記ゲート電極をはさむように配されるソース・ドレイン領域と、前記基板にコンタクトするためのコンタクト拡散領域を備えたバックゲートとを具備し、ソースまたはドレイン領域とゲート電極との間、およびゲート電極とバックゲートとの間に印加される電圧を調整することにより、ゲート絶縁膜に蓄積される電荷を調整可能にしたMOS容量型半導体装置において、前記ソース・ドレイン間距離または、前記バックゲートと前記ゲート電極との間隔とが、前記印加される電圧の周期内に、電子または正孔が前記ゲート絶縁膜と基板との界面に蓄積されうるように決定される。

(もっと読む)

1 - 18 / 18

[ Back to top ]