Fターム[5F038BE02]の内容

Fターム[5F038BE02]の下位に属するFターム

コード化 (37)

Fターム[5F038BE02]に分類される特許

1 - 20 / 36

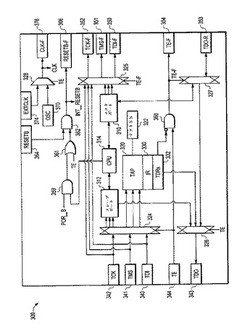

マルチICデバイスをテストするための方法および装置

【課題】マルチICデバイスをテストするための方法および装置を提供する。

【解決手段】集積回路は、入力信号を受け取るように構成される第1の入力相互接続と、テスト・イネーブル信号を受け取るように構成される第1のテスト・イネーブル相互接続と、前記入力信号に対応する値に基づいて該集積回路のテストを実行するためのコントローラと、入力ポートと、前記第1の入力相互接続、前記コントローラ、および前記入力ポートに結合され、前記テスト・イネーブル信号がアサートされていないことに応答して前記入力信号を前記入力ポートに渡し、前記テスト・イネーブル信号がアサートされていることに応答して前記入力信号を前記コントローラに渡すように制御可能である第1のマルチプレクサとを備える。

(もっと読む)

テストモード設定回路

【課題】端子数の少ないテストモード設定回路を提供する。

【解決手段】半導体装置のテストモードを制御するテスト端子に、低閾値電圧のディテクタと高閾値電圧のディテクタを設け、低閾値電圧のディテクタによって論理回路のリセットを解除し、高閾値電圧のディテクタでテストモードを切替え制御するような構成にした。従って、テスト端子とリセット端子とテストモード制御端子が共通になり、端子の数を大幅に削減することが可能である。

(もっと読む)

電圧レギュレータを有する集積回路装置

【課題】集積回路装置のモード端子の数を低減する。

【解決手段】第1の電源端子VCCに接続され第1の電源電圧VDDEを供給する第1の電源配線11と,第1の電源電圧VDDEから第2の電源電圧VDDIを生成し第2の電源配線13に出力する電圧レギュレータ12と,電圧レギュレータの出力に接続され外部キャパシタが接続されるキャパシタ端子Cと,キャパシタ端子に印加される電圧に従い第1の状態と第2の状態とを判定する判定回路21とを有する。この判定回路は、キャパシタ端子Cに第3の電源電圧が印加されないで電圧レギュレータが動作する第1の動作モードと,キャパシタ端子Cに第3の電源電圧が印加されると共に電圧レギュレータが停止する第2の動作モードとを切り換えるので、モード端子数を削減することができる。

(もっと読む)

半導体ウェハ

【課題】テストパッドの数を減らすことができ、かつウェハ状態で各トランジスタを個別にテストすることができる半導体ウェハを得る。

【解決手段】半導体ウェハ1内に複数の半導体装置2が行列状に配置されている。複数の半導体装置2を分離するためのダイシングライン3が設けられている。各半導体装置2は、複数のトランジスタ4を含む。複数のトランジスタ4のコレクタ(第1端子)に、それぞれ個別に複数のテストパッド5(第1テストパッド)が接続されている。複数のトランジスタ4のエミッタ(第2端子)に接地電極11が共通に接続されている。複数のトランジスタ4のベース(制御端子)に、ダイシングライン3内を通る配線6を介して、共通にテストパッド7(第2テストパッド)が接続されている。

(もっと読む)

温度測定用半導体装置、半導体装置の温度測定システムおよび半導体装置の温度測定方法

【課題】プリント基板の配線の発熱に基づく半導体装置の温度を確実に測定可能な装置及び方法を提供する。

【解決手段】半導体装置とともに半導体パッケージを構成するプリント基板34に電気的に接続されて搭載可能であり、プリント基板34の発熱に基づく半導体装置内の温度上昇を測定するための温度測定用半導体装置36であって、マトリックス状に配置された複数の温度センサ60と、温度センサ60によって検出された温度データを通信する通信手段65とが作りこまれて形成されている。

(もっと読む)

信号保持回路、並びにそれを利用した抵抗切替回路及び定電圧源

【課題】制御信号用の端子を設ける必要がない信号保持回路を提供する。

【解決手段】入力端子と第1及び第2の出力端子を有し、第1の電源に接続されているとき、前記入力端子に入力される入力信号と同じ論理の第1の信号と前記入力信号と逆の論理の第2の信号を、前記第1及び第2の出力端子からそれぞれ出力し、前記第1の電源が切り離されているとき、前記第1及び第2の出力端子は共にハイインピーダンスとなる、入力回路と、

第2の電源により動作し、前記第1及び前記第2の出力端子と接続され、前記第1及び第2の出力端子がハイインピーダンスでないとき、前記第1の信号又は前記第2の信号と同じ論理の信号を出力信号として出力し、前記第1及び第2の出力端子がハイインピーダンスであるとき、前記出力信号を保持する、記憶回路と、を備える。

(もっと読む)

半導体集積回路

【課題】製造テストに用いる入出力端子数を削減することができる半導体集積回路を提供する。

【解決手段】データが入力される複数の入力端子と、所望の処理を行う内部回路と、クロック信号が入力されるクロック端子と、複数の入力端子と内部回路との間に設けられ、通常動作モードのとき、入力端子それぞれからデータが入力され、該データを内部回路に出力し、テスト動作モードのとき、クロック信号に基づいて、複数の入力端子の一部から入力される時分割数がX(X≧2)の時分割多重化されたデータを分離して、内部回路に出力する入力信号制御ブロックとを備える。

(もっと読む)

表示装置及び半導体装置

【課題】高精細・多階調・低コスト・低消費電力の表示装置の提供。

【解決手段】表示パネル部110と、走査回路109と、データ線駆動回路とを有する表示装置において、表示パネル部の外に、表示メモリ111と、出力バッファ112と、コントローラ113と、を有するコントローラIC102を備え、表示パネル部110には、データ線駆動回路及び走査回路を含む周辺回路が、画素スイッチをなすトランジスタと同一プロセスで形成され、データ線駆動回路は、デジタル信号の表示データをアナログ信号に変換するDAC回路106を備え、コントローラIC102と、表示パネル部のデータ線駆動回路との間のデータ転送用のバスの幅が、コントローラと上位装置の間のバスよりも、一回あたりの転送で多くのビットデータが並列転送されて、データ線駆動回路の動作周波数を下げる構成とし、表示信号を伝える配線が、他の表示信号を伝える配線と交差しないようにする。

(もっと読む)

MCP半導体記憶装置とそのテスト方法

【課題】複数チップを同時に選択状態にし複数チップから内部データを同時に読み出した場合、良否判定を可能とする半導体記憶装置及びそのテスト方法の提供。

【解決手段】端子(DQ1、DQ2)が共通に接続されたチップ(RAM)11a、11bを少なくとも備え、チップ11a、11bは、テスト時に、端子(DQ1、DQ2)を第1電源電位側に設定する駆動能力と、前記出力端子を第2電源電位側に設定する駆動能力とに差を設けるデータ入出力回路(12a、12b)をそれぞれ備えている。テスト時に、前記第2の駆動能力を前記第1の駆動能力よりも高く設定し、前記各チップから前記端子に出力される信号レベルが、前記第2の電源電圧レベルの場合をフェイル信号、前記第1の電源電圧レベルの場合をパス信号とする条件のもとで、複数のチップのうち1つでもフェイル信号を出力する場合に、DQ1、DQ2の共通接続された端子DQには、前記第2の電源電圧レベルが出力される。

(もっと読む)

試験構造を集積回路に組み込むためのシステムおよび方法

【課題】 高い歩留まりを得ることができるように、カスタマイズされた回路を正確に試験するための手段を提供する。

【解決手段】 例えばASICのような集積回路においてデバイス固有の試験を実行しパラメータ・データを取得して、過剰な試験時間要件も、追加のシリコンも、特別な試験機器も必要とすることなく、各チップを個別に試験するためのシステムおよび方法(1000)が提供される。試験システムは、IC設計における未使用のバックフィル空間に組み込まれたデバイス試験構造(920)を含み、ICに含まれる選択された1組のデバイスと同一の1組のダミー・デバイス(940)を試験する。デバイス試験構造(920)は、カスタマ要件および設計要件(1010)に従って、ライブラリ(920)から選択される。選択された試験構造は、更に、優先度(1040)の順序で優先順位をつけて(1030)、設計内の設計要素に割り当てられる。配置アルゴリズム(1060)が、設計、レイアウト、および製造要件を用いて、選択した試験構造を、製造される設計(950)の最終レイアウトに配置する。

(もっと読む)

集積回路、電子回路基板及び検査方法

【課題】 小型化を達成可能な集積回路、電子回路基板、DC−DCコンバータ及びこれらの回路の検査方法を提供する。

【解決手段】 機能回路FCに特定の検査信号が入力されると、その出力端子SW,E(VOUT)から検査信号に応じたモニタ信号が出力される。機能回路FCが正常であれば、判定器12D入力されるモニタ信号の値は、機能回路が正常である場合に期待される信号となり、異常であれば、正常時の信号とは異なることとなる。したがって、テスト回路49から検査信号を機能回路FCに入力することにより、機能回路FCの検査が可能となる。検査信号は、機能回路FCの電源端子Vccを介してテスト回路49に入力されるため、検査用の付加的な端子が不要となり、装置を小型化することが可能となる。

(もっと読む)

テスト回路、テスト方法、半導体集積回路

【課題】 LSI回路の占有面積と入出力端子数の増加を抑制しつつLSI回路のテスト時間の短縮化を可能にするLSIのテスト回路を提供する。

【解決手段】 スキャンパスが形成されたテスト対象チップ2に対するテストを行うための同チップ2とは別のテスト用チップ3上に形成されており、スキャンイン信号SINが入力端子31より入力されると、テスト入力制御回路36によって各スキャンパス毎の分岐入力テスト信号SIN1及びSIN2を生成し、夫々を入力用電極11或いは14に供給する。スキャンサンプルモードになった後、各スキャンパスからせられたテスト結果が出力用電極17及び18よりテスト出力制御回路37に対して与えられ、これらが一の信号として多重化されて出力端子34より外部に供給される。

(もっと読む)

半導体装置

【課題】局所的な特性変動の問題に対しても有効に対応でき、かつ高速化と低消費電力化を両立させることが可能な半導体装置を提供すること。

【解決手段】半導体装置100は、内部に満遍なく配置され、配置された場所の局所的な特性変動を遅延情報として検出する複数のセンサ回路101a〜101gと、複数のセンサ回路101a〜101gにより検出された遅延情報をとりまとめて外部に送出する出力インターフェース回路102とを備え、その外側に、検出された遅延情報を統計的に処理し、プロセスばらつき等の状態を判断して制御コードを生成する演算部110と、不揮発性メモリ103に記録された制御コードから出力すべき電圧を決定する出力電圧制御部120と、半導体装置100に電源電圧131aと接地電位131bを供給する電源電圧発生部130とを備える。

(もっと読む)

トリミング回路

【課題】集積回路のトリミングを行う回路において、ウエハテストでの試験漏れを無くす若しくはごく少なくし、チップの面積、サイズを小さくすることができ、コスト高になるのを抑え、さらにパッケージコストも削減することができるようにする。

【解決手段】集積回路に標準装備された外部端子の中で集積回路の内部節点と接続可能な例えば入力端子Ti1に抵抗R1を介してヒューズF1を接続する。そして、このヒューズF1を接続した入力端子Ti1の電圧を測定して集積回路のトリミングデータを算出するとともに、その入力端子Ti1を介して外部から試験電圧を印加して集積回路がその試験電圧で動作したときの特性を測定する。

(もっと読む)

半導体集積回路

【課題】ICをより小さく作る。

【解決手段】モータ駆動回路100は、シリアルコントローラ24をシリアルデータSDATAの取り込み待ち状態にするための契機としてストローブ信号STBのネガティブエッジを利用するとともに、ストローブ信号STBの次のポジティブエッジまでの時間が所定時間以上であったときには、タイマー22から出力されるパワーセーブ信号PSのネガティブエッジという形でストローブ信号STBのネガティブエッジを省電モードに移行するための移行指示として利用する。

(もっと読む)

半導体集積回路装置および不揮発性メモリ装置

【課題】 不揮発性メモリ装置にデータを電気的に書き込むときに、半導体集積回路基板には高電圧が印加されないようにする。

【解決手段】 1つの配線基板(51)上に、第1の電圧で電気的にデータを書込み可能な不揮発性メモリ装置(15B)と、第1の電圧よりも低い第2の電圧で動作する半導体集積回路基板(10E)とが搭載された半導体集積回路装置(20E)において、不揮発性メモリ装置は、第1の電圧が供給される第1の端子(15−3)と第2の電圧を出力する第2の端子(15−4)とを持ち、半導体集積回路基板(10E)は、第2の端子と電気的に接続された第3の端子(RES#)を持つ。不揮発性メモリ装置(15B)は、第1の端子と第2の端子との間に設けられて、第1の電圧を第2の電圧に変換する電圧変換回路を有する。不揮発性メモリ装置(15B)は、半導体集積回路基板(10E)上に積層されている。

(もっと読む)

ウェハおよび半導体装置のテスト方法

【課題】テスト用の信号数を減らすことにより、テスト用パッドやプローブカードのコンタクトピンの数を削減できるウェハを提供すること。

【解決手段】チップ領域2に対して隣り合うスクライブライン8に設けられた少なくとも3つのパッド10A,10B,10Cを備える。それらの3つのパッドは、チップ領域2内の電源電位部5に接続された電源用パッド10Aと、チップ領域2内の接地電位部6に接続された接地用パッド10Bと、チップ領域2内の半導体装置7に接続され、その半導体装置7の動作状態を通常動作状態とスタンバイ状態との間で切り替える切替用パッド10Cである。3つのパッド10A,10B,10Cには、ウェハテスト時にそれぞれプローブカードのコンタクトピン9A,9B,9Cが当接される。

(もっと読む)

モノリシックセンサ配置、およびそのモノリシックセンサ配置を制御する方法

【課題】 変更された操作条件に引き続き適合することを可能にするように配置されたモノリシックセンサを提供すること。

【解決手段】 モノリシックセンサ配置は、ハウジングと、ハウジング内に集積化されているセンサSと、センサSとの接触を可能とするべく、ハウジング上に設けられている少なくとも2つの接続端子C0,C1とを備える。また、ハウジングは統合デジタル回路を含み、該回路には、自由にプログラム可能なデジタルプロセッサCPUと、プログラムメモリMPと、データメモリMDとが備えられる。それらは、センサの機能、および/または測定データの制御および/または処理を行うために使用される。

(もっと読む)

テストモード設定回路

【課題】ノイズなどの誤信号によるテストモードへの移行を防止し、さらにテストモードから容易に抜け出るようにする。

【解決手段】パワーオンリセット信号PORと専用のリセット信号TESTRがHになると、シフトレジスタ2は、クロックCLKに同期して制御信号TESTDを順次入力してシフトする。デコード回路3は、シフトレジスタ2から出力されるデータQ6−Q0が「H**L**H」(*は任意)になると移行許可信号TESTFをHにする。制御信号TESTDとリセット信号TESTRがHであることを条件として、最終的に出力する移行許可信号TESTEをHにする。デコード回路3は、データQ5、Q4、Q2、Q1をデコードしてテストモード選択信号TEST1〜TEST16を生成する。

(もっと読む)

画像出力装置および画像データ出力方法

【課題】2画面(2系統)分の画像データの同時出力機能を出力ピン数を増加させることなく実現可能とした画像出力装置を提供する。

【解決手段】本発明の画像出力装置が備える多重データ生成部100の出力タイミング生成部102は、ビデオデータA,Bを、従来通り、タイミングクロックA,Bの片側エッジに従って取り込んでいく。セレクタ101は、クロックの両エッジ、つまり立ち上がりエッジでビデオデータA、立ち下がりエッジでビデオデータBを出力する指示を出力タイミング生成部102に与える。その結果、ビデオデータA,Bが交互に並べられた多重データが生成され、クロックの立ち上がりエッジで画像データを取り込むビデオエンコーダ向けにビデオデータA、クロックの立ち下がりエッジで画像データを取り込むビデオエンコーダ向けにビデオデータBを1画面分のインタフェースで同時出力可能となる。

(もっと読む)

1 - 20 / 36

[ Back to top ]